【友晶科技】基于FPGA和ADV7123的VGA彩条显示(DE10-Standard、DE1-SOC、DE2-115)

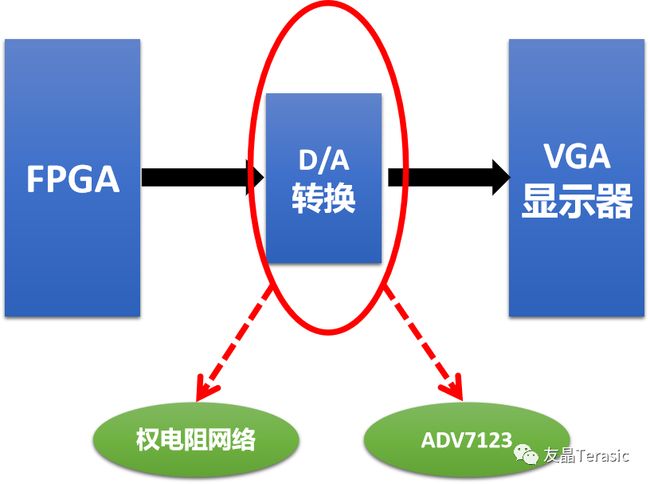

前面推送过《基于权电阻网络的VGA彩条显示》文章,里面介绍的是DE0-CV和DE10-Lite开发板基于权电阻网络的VGA彩条显示的设计。今天将介绍DE10-Standard开发板基于ADV7123芯片(替换权电阻网络)的VGA彩条显示的设计。

下面我们先从ADV7123芯片开始讲解。(关于VGA接口定义、 行同步和场同步、分辨率、像素时钟计算等相关知识参见《基于权电阻网络的VGA彩条显示》,此篇不再赘述。)

解读ADV7123芯片

ADV7123芯片是一款高速数模转换器。它内置三个高速、位宽为10位、带互补输出的视频DAC。该芯片的主要功能是将RGB888的颜色数据转换成模拟的电压信号,然后送到VGA接口的3个通道(R、G、B)。RGB888颜色数据是24位(R、G、B分量各占8位),共可显示 2^24=16777216 种颜色。

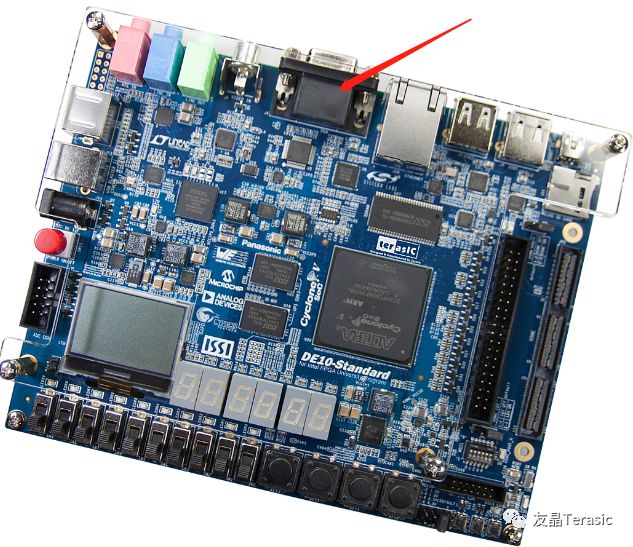

DE10-Standard、DE1-SOC、DE2-115开发板上都有一个15 引脚的D-SUB连接器,用于VGA输出。

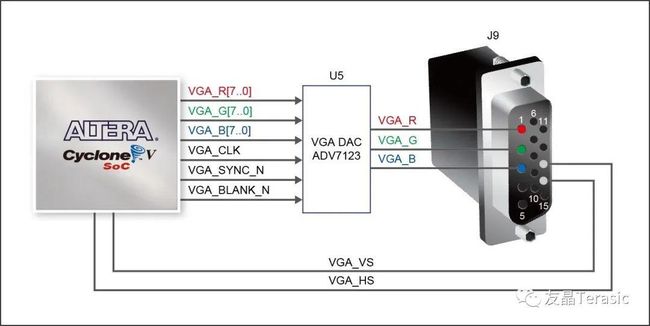

VGA信号从FPGA产生,经过ADV7123芯片后通过D-SUB连接器输出给VGA显示器。FPGA与VGA之间的信号连接如图:

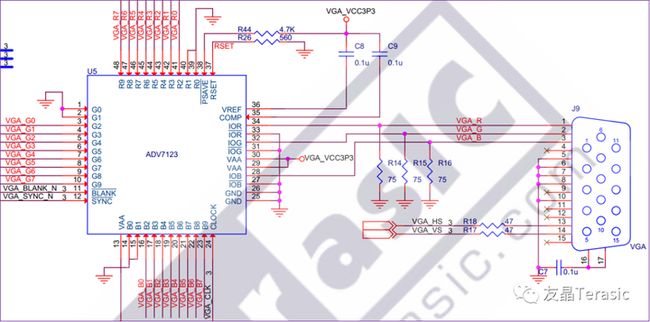

与上一篇的权电阻网络方案相比, ADV7123的方案会多三个控制信号VGA_CLK和VGA_BLANK_N和VGA_SYNC_N,信号连接电路图如下:

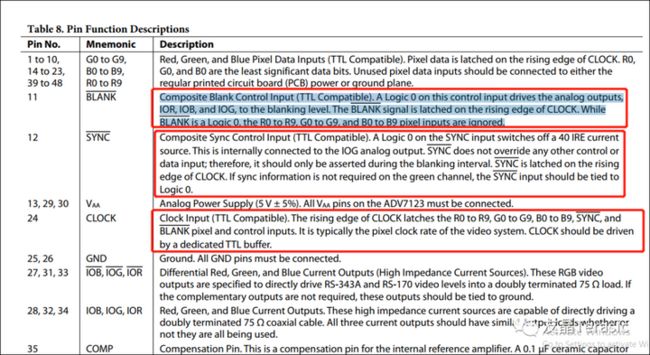

这三个信号的定义参考ADV7123手册。

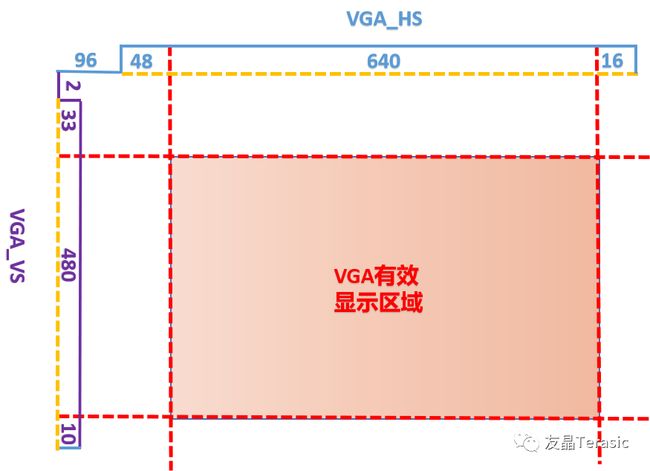

CLOCK是像素时钟信号,由FPGA端VGA_CLK信号提供,如果我们选择分辨率640*480@60Hz的话,VGA_CLK信号应该输出25.2MHz(800*525*60)时钟。

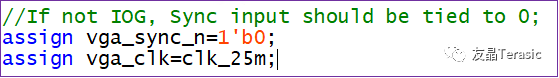

SYNC是复合同步控制IOG输入信号,这里我们不用这个模式就直接将该信号拉低为0(assign VGA_SYNC_N=1'b0)。

BLANK为复合消隐信号,低电平有效。我们先来了解消隐的概念。

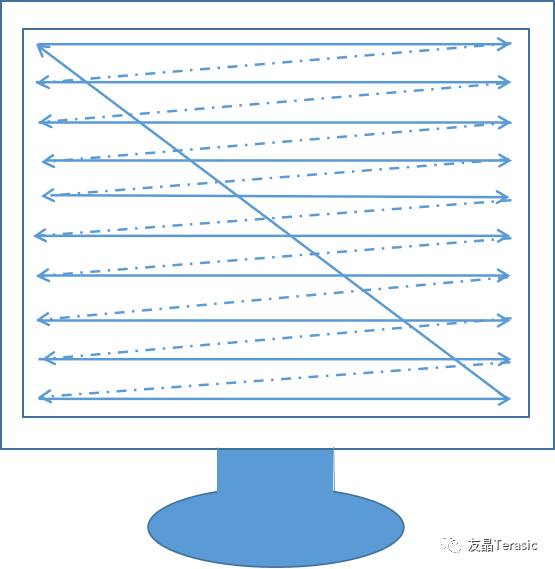

在显示器的扫描过程中,扫描总是从显示器的左上角开始,水平向前行进,同时扫描点也以较慢的速率向下移动。当扫描点到达显示器右侧边缘时,扫描点快速返回左侧,重新开始在第1行的起点下面进行第2行扫描。当扫描完显示器上所有的行,就形成一帧,然后电子束要从显示器的右下角返回到显示器的左上角,开始新一帧的扫描。

电子束在行与行之间的返回过程以及在帧与帧之间的返回过程(从右下角返回到显示器的左上角)都称之为逆程,扫描正程期间传送图像信号,逆程期间不传送图像信号。电子束逆程扫描在荧光屏上出现回扫线,将对正程的图像造成干扰,影响图像的清晰度。因此需使显示器在行、场扫描逆程期间电子束截止,以消除行、场逆程回扫线,即实现消隐。

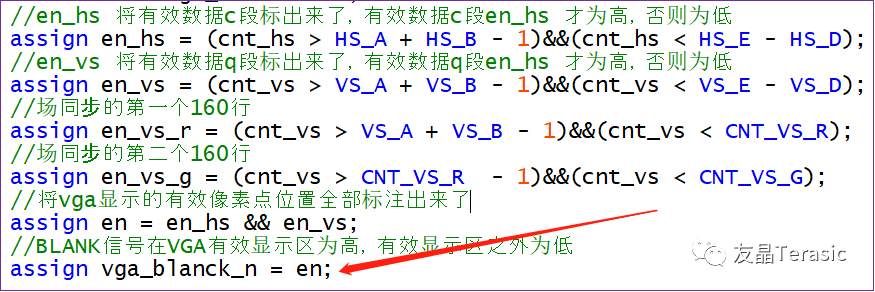

当BLANK为低电平时,模拟视频输出消隐电平,此时从R7~R0,G7~G0,B7~B0输入的所有数据被忽略。所以在本设计中VGA_BLANK_N信号应该这样设计:在VGA有效显示区为高,有效显示区之外为低。

至此三个信号分析完毕,完整代码也就可以写出来了(完整代码参考文末下载链接)。

代码解析

代码移植自上篇《基于权电阻网络的VGA彩条显示》,在其基础上做如下修改:

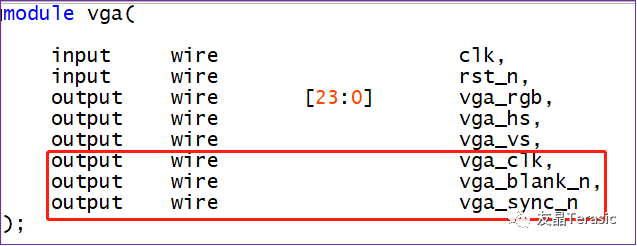

1. 在vga.v里面添加三个控制信号VGA_CLK和VGA_BLANK_N和VGA_SYNC_N:

在vga.v里面添加如下两行代码:

在vga_ctl.v里面添加:

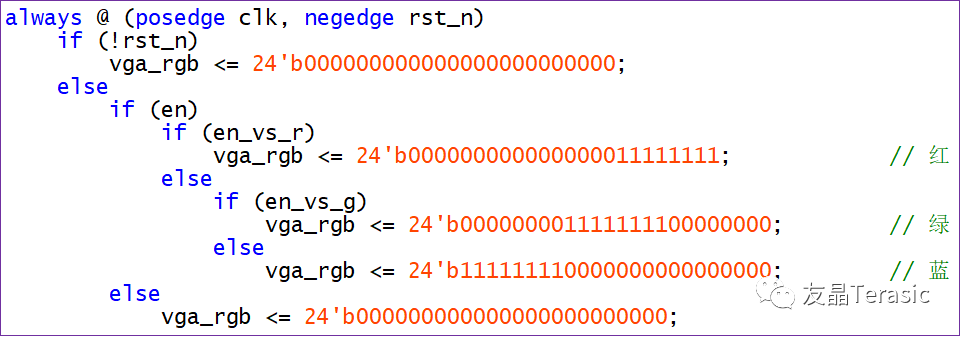

2. 将之前的RGB444改成RGB888:

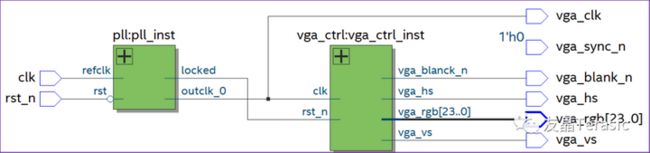

整个工程的RTL视图如下:

引脚分配

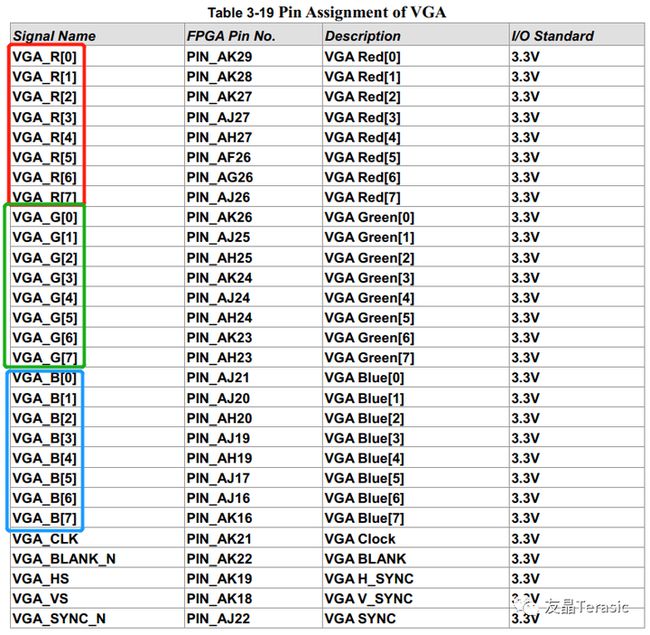

DE10-Standard 的 VGA 管脚分配参考手册DE10-Standard_User_manual.pdf第35页:

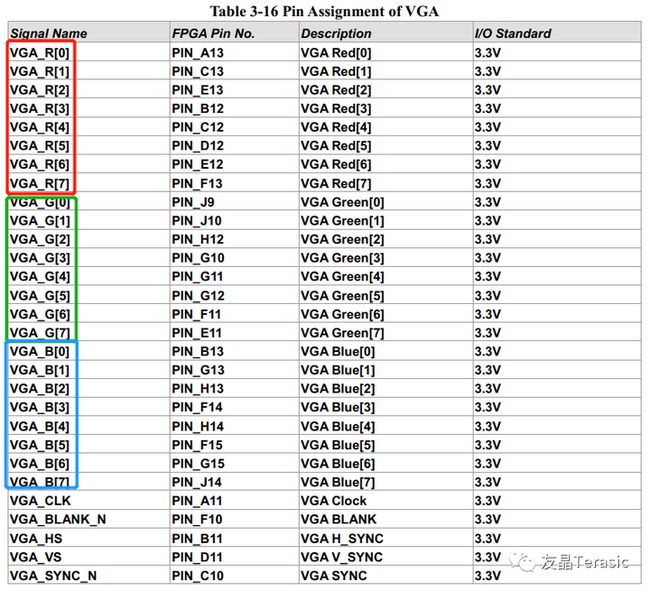

DE1-SOC 的 VGA 管脚分配参考手册DE1-SoC_User_manual.pdf 第35页:

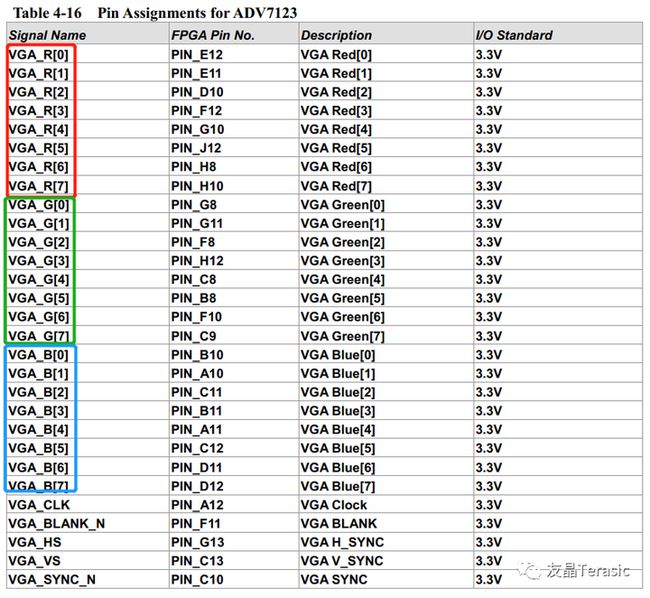

DE2-115 的 VGA 管脚分配参考手册DE2_115_User_manual.pdf第55页:

测试结果

-

给DE10-Standard开发板连接好VGA显示器、电源和USB下载线。然后上电。

-

调用Quartus的下载工具Programmer将sof文件下载到开发板配置FPGA。

-

配置成功后可以看到VGA显示器显示如下。

源码下载

DE10-Standard开发板对应源码下载地址:http://mail.terasic.com.cn/~bingxia/DE10-Standard_VGA.rar

DE2-115和DE1-SOC 的源码和DE10-Standard源码一样,只需修改引脚分配即可。