AD9361纯逻辑控制从0到1连载2-将脚本转化为verilog代码

首先查看一下,上一章我们生成的脚本文件fdd_600m:

//************************************************************

// AD9361 R2 Auto Generated Initialization Script: This script was

// generated using the AD9361 Customer software Version 2.1.3

//************************************************************

// Profile: Custom

// REFCLK_IN: 40.000 MHz

RESET_FPGA

RESET_DUT

BlockWrite 2,6 // Set ADI FPGA SPI to 20Mhz

SPIWrite 3DF,01 // Required for proper operation

ReadPartNumber

SPIWrite 2A6,0E // Enable Master Bias

SPIWrite 2A8,0E // Set Bandgap Trim

REFCLK_Scale 40.000000,1,2 // Sets local variables in script engine, user can ignore

SPIWrite 2AB,07 // Set RF PLL reflclk scale to REFCLK * 2

SPIWrite 2AC,FF // Set RF PLL reflclk scale to REFCLK * 2

SPIWrite 009,17 // Enable Clocks

WAIT 20 // waits 20 ms

//此

//处

//有

//省

//略

//************************************************************

// Setup RSSI and Power Measurement Duration Registers

//************************************************************

SPIWrite 150,08 // RSSI Measurement Duration 0, 1

SPIWrite 151,00 // RSSI Measurement Duration 2, 3

SPIWrite 152,FF // RSSI Weighted Multiplier 0

SPIWrite 153,00 // RSSI Weighted Multiplier 1

SPIWrite 154,00 // RSSI Weighted Multiplier 2

SPIWrite 155,00 // RSSI Weighted Multiplier 3

SPIWrite 156,00 // RSSI Delay

SPIWrite 157,00 // RSSI Wait

SPIWrite 158,01 // RSSI Mode Select

SPIWrite 15C,62 // Power Measurement Duration

注意到,其中大部分都是SPIWrite命令,少部分的SPIRead命令,以及其他包括RESET_FPGA,RESET_DUT,BlockWrite,ReadPartNumber,WAIT,WAIT_CALDONE等。

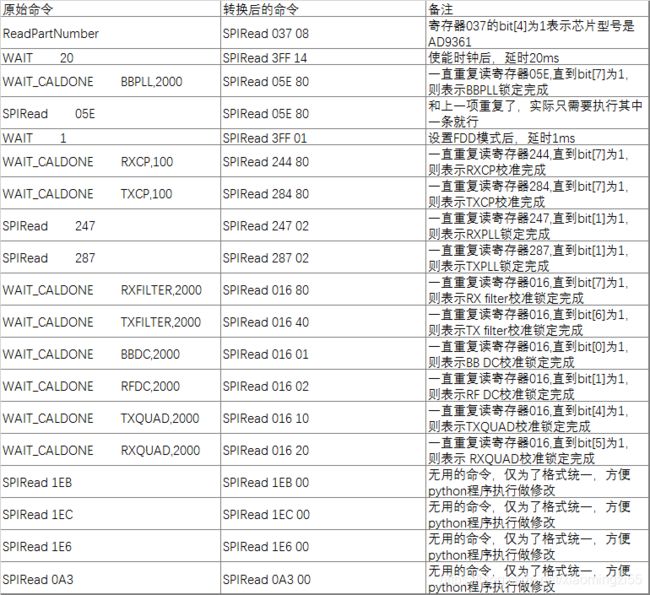

其中,RESET_FPGA,RESET_DUT是复位FPGA和AD9361的操作,我们直接在初始化前复位就好了,BlockWrite这行是用来确定SPI时钟频率的,我们直接忽略,因为SPI时钟频率由FPGA的代码确定。ReadPartNumber是指读取寄存器037的值,因此可以直接转换为SPIRead,或者直接丢掉这行命令,对初始化没有影响。WAIT_CALDONE都是读某个确定的寄存器,读回某个值后继续执行下一步的操作,因此我们也可以将其转换为SPIRead的命令。而WAIT我们也可以将其转换为某个特定的SPIRead命令,代码在执行到这行命令的时候,固定延时等待就好了。

综上所述,整个脚本我们都可以转换为SPIWrite和SPIRead的组合。因此我们定义一个17bit的数,最高位bit[16]表示读或者写,1为写,0为读。接下来bit[15:8]表示我们要读写的地址,最后8bit根据命令不同,填入不同的值,具体如下:

以上所有的替换,删除等操作以及最终转换为verilog代码,都通过自己用python编写代码来自动完成。

最终生成的verilog代码是一个如下的函数。

function [18:0] fdd_600m;

input [12:0] index;

begin

case(index)

//************************************************************

// AD9361 R2 Auto Generated Initialization Script: This script was

// generated using the AD9361 Customer software Version 2.1.3

//************************************************************

// Profile: Custom

// REFCLK_IN: 40.000 MHz

13'd0 :fdd_600m={1'b1,10'h3DF,8'h01}; // Required for proper operation

13'd1 :fdd_600m={1'b0,10'h037,8'h08}; // ReadPartNumber

13'd2 :fdd_600m={1'b1,10'h2A6,8'h0E}; // Enable Master Bias

13'd3 :fdd_600m={1'b1,10'h2A8,8'h0E}; // Set Bandgap Trim

13'd4 :fdd_600m={1'b1,10'h2AB,8'h07}; // Set RF PLL reflclk scale to REFCLK * 2

13'd5 :fdd_600m={1'b1,10'h2AC,8'hFF}; // Set RF PLL reflclk scale to REFCLK * 2

13'd6 :fdd_600m={1'b1,10'h009,8'h17}; // Enable Clocks

13'd7 :fdd_600m={1'b0,10'h3FF,8'h14}; // waits 20 ms

//此

//处

//省

//略

//多

//行

//。

//。

//。

//************************************************************

// Setup RSSI and Power Measurement Duration Registers

//************************************************************

13'd2567:fdd_600m={1'b1,10'h150,8'h08}; // RSSI Measurement Duration 0, 1

13'd2568:fdd_600m={1'b1,10'h151,8'h00}; // RSSI Measurement Duration 2, 3

13'd2569:fdd_600m={1'b1,10'h152,8'hFF}; // RSSI Weighted Multiplier 0

13'd2570:fdd_600m={1'b1,10'h153,8'h00}; // RSSI Weighted Multiplier 1

13'd2571:fdd_600m={1'b1,10'h154,8'h00}; // RSSI Weighted Multiplier 2

13'd2572:fdd_600m={1'b1,10'h155,8'h00}; // RSSI Weighted Multiplier 3

13'd2573:fdd_600m={1'b1,10'h156,8'h00}; // RSSI Delay

13'd2574:fdd_600m={1'b1,10'h157,8'h00}; // RSSI Wait

13'd2575:fdd_600m={1'b1,10'h158,8'h01}; // RSSI Mode Select

13'd2576:fdd_600m={1'b1,10'h15C,8'h62}; // Power Measurement Duration

13'd2577:fdd_600m={1'b1,10'h15C,8'h02}; // Power Measurement Duration

//************************************************************

//Manually add:Force RX and TX on

//************************************************************

13'd2578:fdd_600m={1'b1,10'h014,8'h6D}; // Set Force rx and tx State bit

13'd2579:fdd_600m={1'b0,10'h3FF,8'hFF}; // end of command

endcase

end

endfunction

下一个章节讲解如何使用这个函数。

链接:https://pan.baidu.com/s/1ZllL8FwZqQB3KavLxGuakA?pwd=7y0b

提取码:7y0b

–来自百度网盘超级会员V3的分享