【ug572】UltraScale体系结构时钟资源手册节选(二)

时钟缓冲区

The PHY global clocking contains several sets of BUFGCTRLs, BUFGCEs, and BUFGCE_DIVs. Each set can be driven by four GC pins from the adjacent bank, MMCMs, PLLs in the same PHY, and interconnect. The clock buffers then drive the routing and distribution resources across the entire device. Each PHY contains 24 BUFGCEs, 8 BUFGCTRLs, and 4 BUFGCE_DIVs but only 24 of them can be used at the same time.

PHY 全局时钟包含多组 BUFGCTRL、BUFGCE 和 BUFGCE_DIV。每组可由来自相邻bank、MMCM、同一 PHY 中的 PLL 和互连的四个 GC 引脚驱动。然后,时钟缓冲器驱动整个器件的路由和分配资源。每个 PHY 包含 24 个 BUFGCE、8 个 BUFGCTRL 和 4 个 BUFGCE_DIV,但只能同时使用其中的 24 个。

IMPORTANT: It is recommended to only allow the Vivado® Placer to assign all global clock buffers to specific locations. Each CR contains 24 BUFGCEs, 8 BUFGCTRLs and 4 BUFGCE_DIVs. These clock buffers share the 24 routing tracks and therefore collisions may occur resulting in unroutable designs. If the design requires a number of global clock buffers to be in a certain CR then it is recommended to attach the CLOCK_REGION property to these buffers instead of a specific LOCATION property.

建议仅允许 Vivado® Placer 将所有全局时钟缓冲区分配到特定位置。每个CR包含24个BUFGCE、8个BUFGCTRL和4个BUFGCE_DIV。这些时钟缓冲器共享 24 个布线轨道,因此可能会发生冲突,导致设计无法布线。如果设计需要多个全局时钟缓冲区位于某个 CR 中,则建议将 CLOCK_REGION 属性附加到这些缓冲区,而不是特定的 LOCATION 属性。

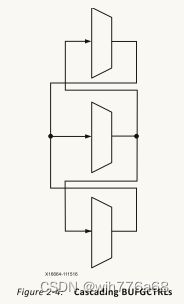

In the clocking architecture, BUFGCTRL multiplexers and all derivatives can be cascaded to adjacent clock buffers, effectively creating a ring of eight BUFGMUXes (BUFGCTRL multiplexers). Figure 2-4 shows a simplified diagram of cascading BUFGCTRLs.

在时钟架构中,BUFGCTRL 多路复用器和所有衍生原语都可以级联到相邻的时钟缓冲,从而有效地创建一个由八个 BUFGMUX(BUFGCTRL 多路复用器)组成的环。图 2-4 显示了级联 BUFGCTRL 的简化图。

The following subsections detail the various configurations, primitives, and use models of the clock buffers.

以下小节详细介绍了时钟缓冲区的各种配置、原语和使用模型。

BUFGCTRL 时钟缓冲器原语

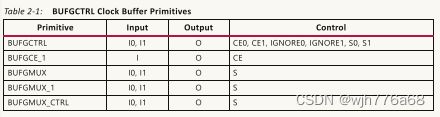

The primitives in Table 2-1 are different configurations of the clock BUFGCTRL buffers. The Vivado tools manage the configuration of all these primitives, and the Vivado Design Suite User Guide: Using Constraints (UG903) [Ref 4] describes the LOC constraint.

表 2-1 中的原语是时钟 BUFGCTRL 缓冲区的不同配置。 Vivado 工具管理所有这些原语的配置,《Vivado Design Suite 用户指南:使用约束》(UG903) [参考资料 4] 描述了 LOC 约束。

BUFGCTRL

The BUFGCTRL primitive shown in Figure 2-5 can switch between two asynchronous clocks. All other global clock buffer primitives are derived from certain configurations of BUFGCTRL.

图 2-5 所示的 BUFGCTRL 原语可以在两个异步时钟之间切换。所有其他全局时钟缓冲区原语均源自 BUFGCTRL 的某些配置。

BUFGCTRL has four select lines, S0, S1, CE0, and CE1. It also has two additional control lines, IGNORE0 and IGNORE1. These six control lines are used to control the inputs I0 and I1.

BUFGCTRL 有四个选择线:S0、S1、CE0 和 CE1。它还具有两个附加控制线:IGNORE0 和 IGNORE1。这六个控制线用于控制输入 I0 和 I1。

BUFGCTRL is designed to switch between two clock inputs without the possibility of a glitch. When the presently selected clock transitions from High to Low after S0 and S1 change, the output is kept Low until the other (to-be-selected) clock transitions from High to Low. Then, the new clock starts driving the output.The default configuration for BUFGCTRL is falling-edge sensitive and held at Low prior to the input switching. BUFGCTRL can also be rising-edge sensitive and held at High prior to the input switching by using the INIT_OUT attribute.

BUFGCTRL 旨在在两个时钟输入之间切换,而不会出现毛刺。当 S0 和 S1 改变后当前选择的时钟从高电平跳变到低电平时,输出保持低电平,直到另一个(待选择的)时钟从高电平跳变到低电平。然后,新时钟开始驱动输出。BUFGCTRL 的默认配置是下降沿敏感,并在输入切换之前保持在低电平。 BUFGCTRL 还可以是上升沿敏感的,并通过使用 INIT_OUT 属性在输入切换之前保持在高电平。

In some applications, the conditions previously described are not desirable. Asserting the IGNORE pins bypasses the BUFGCTRL from detecting the conditions for switching between two clock inputs. In other words, asserting IGNORE causes the MUX to switch the inputs at the instant the select pin changes. IGNORE0 causes the output to switch away from the I0 input immediately when the select pin changes, while IGNORE1 causes the output to switch away from the I1 input immediately when the select pin changes.

在一些应用中,先前描述的条件并不理想。置位 IGNORE 引脚会绕过 BUFGCTRL 检测两个时钟输入之间切换的条件。换句话说,置位 IGNORE 会导致 MUX 在选择引脚发生变化时切换输入。当选择引脚发生变化时,IGNORE0 会导致输出立即从 I0 输入切换,而当选择引脚发生变化时,IGNORE1 会导致输出立即从 I1 输入切换。

Selection of an input clock requires a “select” pair (S0 and CE0, or S1 and CE1) to be asserted High. If either S or clock enable (CE) is not asserted High, the desired input is not selected. In normal operation, both S and CE pairs (all four select lines) are not expected to be asserted High simultaneously. Typically, only one pin of a “select” pair is used as a select line, while the other pin is tied High. The truth table is shown in Table 2-2.

输入时钟的选择需要将“选择”对(S0 和 CE0,或 S1 和 CE1)置为高电平。如果 S 或时钟使能 (CE) 未置为高电平,则不会选择所需的输入。在正常操作中,S 和 CE 对(所有四个选择线)预计不会同时被置为高电平。通常,“选择”对中只有一个引脚用作选择线,而另一个引脚则连接为高电平。真值表如表2-2所示。

Although both S and CE are used to select a desired output, only S is suggested for glitch-free switching. This is because when using CE to switch clocks, the change in clock selection can be faster than when using S. A violation in the setup/hold time of the CE pins causes a glitch at the clock output. On the other hand, using the S pins allows the user to switch between the two clock inputs without regard to setup/hold times. As a result, using S to switch clocks does not result in a glitch. See BUFGMUX_CTRL, page 22.

尽管 S 和 CE 都用于选择所需的输出,但建议仅使用 S 来实现无干扰切换。这是因为当使用 CE 切换时钟时,时钟选择的变化可能比使用 S 时更快。CE 引脚的建立/保持时间的违规会导致时钟输出出现毛刺。另一方面,使用 S 引脚允许用户在两个时钟输入之间切换,而无需考虑建立/保持时间。因此,使用 S 切换时钟不会导致毛刺。请参见 BUFGMUX_CTRL,第 22 页。

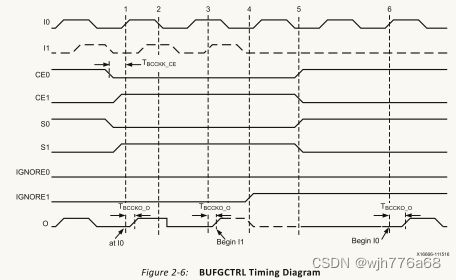

The timing diagram in Figure 2-6 illustrates various clock switching conditions using the BUFGCTRL primitives. Exact timing numbers are best found using the speed specification.

图 2-6 中的时序图说明了使用 BUFGCTRL 原语的各种时钟切换条件。准确的计时数字最好使用速度规范来找到。

-

Before time event 1, output O uses input I0.

-

在时间事件 1 之前,输出 O 使用输入 I0。

-

At time T B C C C K _ C E T_{BCCCK\_CE} TBCCCK_CE, before the rising edge at time event 1, both CE0 and S0 are deasserted Low. At about the same time, both CE1 and S1 are asserted High.

-

在时间 T B C C C K _ C E T_{BCCCK\_CE} TBCCCK_CE,在时间事件1 的上升沿之前,CE0 和S0 都被置为低电平。大约在同一时间,CE1 和 S1 均被置为高电平。

-

At time T B C C K O _ O T_{BCCKO\_O} TBCCKO_O, after time event 3, output O uses input I1. This occurs after a High-to-Low transition of I0 (event 2) followed by a High-to-Low transition of I1.

-

在时间事件3 之后的时间 T B C C K O _ O T_{BCCKO\_O} TBCCKO_O,输出O 使用输入I1。这发生在 I0 从高到低的转换(事件 2)之后,然后是 I1 从高到低的转换。

-

At time event 4, IGNORE1 is asserted.

-

在事件4 时,IGNORE1 被置位。

-

At time event 5, CE0 and S0 are asserted High while CE1 and S1 are deasserted Low. At T B C C K O _ O T_{BCCKO\_O} TBCCKO_O, after time event 6, output O has switched from I1 to I0 without requiring a High-to-Low transition of I1.

-

在事件5 时,CE0 和S0 被置为高电平,而CE1 和S1 被置为低电平。在时间事件 6 之后的 T B C C K O _ O T_{BCCKO\_O} TBCCKO_O 处,输出 O 已从 I1 切换到 I0,而不需要 I1 从高到低的转换。

Other capabilities of BUFGCTRL are:

BUFGCTRL 的其他功能包括:

-

Pre-selection of the I0 and I1 inputs are made after configuration but before device operation.

-

I0 和 I1 输入的预选是在配置之后、设备运行之前进行的。

-

The initial output after configuration can be selected as either High or Low.

-

配置后的初始输出可以选择为高或低。

-

Clock selection using CE0 and CE1 only (S0 and S1 tied High) can change the clock selection without waiting for a High-to-Low transition on the previously selected clock.

-

仅使用CE0 和CE1(S0 和S1 连接为高电平)的时钟选择可以更改时钟选择,而无需等待先前选择的时钟从高电平到低电平的转换。

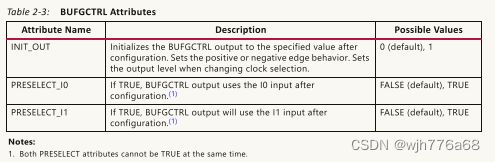

表2-3总结了BUFGCTRL原语的属性

| 属性名称 | 描述 | 可行值 |

|---|---|---|

| INIT_OUT | 配置后,将BUFGCTRL输出初始化为指定值。设置正边或负边的行为。设置更改时钟选择时的输出电平。 | 0, 1 |

| PRESELECT_I0 | 如果为TRUE,则BUFGCTRL输出在配置后使用I0输入。 | FALSE, TRUE |

| PRESELECT_I1 | 如果为TRUE,则BUFGCTRL输出在配置后使用I1输入。 | FALSE, TRUE |

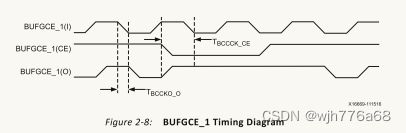

BUFGCE_1

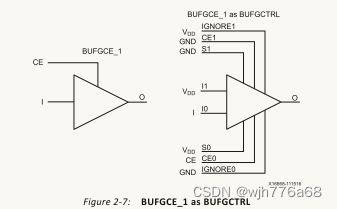

BUFGCE_1 is a clock buffer with one clock input, one clock output, and a clock enable line. This primitive is based on BUFGCTRL with some pins connected to logic High or Low. Figure 2-7 illustrates the relationship of BUFGCE_1 and BUFGCTRL. The LOC constraint is available for manually placing the BUFGCE_1 location. See the Vivado Design Suite User Guide: Using Constraints (UG903) [Ref 4] for more information.

BUFGCE_1是具有一个时钟输入、一个时钟输出和时钟使能线的时钟缓冲器。此基元基于BUFGCTRL,其中一些引脚连接到逻辑高或低。图2-7显示了BUFGCE_1和BUFGCTRL的关系。LOC约束可用于手动放置BUFGCE_1位置。有关更多信息,请参阅Vivado Design Suite用户指南:使用约束(UG903)[参考文献4]。

The switching condition for BUFGCE_1 is similar to BUFGCTRL with INIT_OUT set to 1. If the CE input is Low prior to the incoming falling clock edge, the following clock pulse does not pass through the clock buffer, and the output stays High. Any level change of CE during the incoming clock Low pulse has no effect until the clock transitions High. The output stays High when the clock is disabled. However, when the clock is being disabled, it completes the clock Low pulse.

BUFGCE_1的切换条件类似于INIT_OUT设置为1的BUFGCTRL。如果CE输入在进入的下降时钟沿之前为低,则随后的时钟脉冲不会通过时钟缓冲器,并且输出保持为高。在输入时钟低脉冲期间CE的任何电平变化都没有影响,直到时钟转变为高。时钟被禁用时,输出保持高电平。但是,当时钟被禁用时,它完成时钟低脉冲。

Because the clock enable line uses the CE pin of the BUFGCTRL, the select signal must meet the setup time requirement. Violating this setup time can result in a glitch.

因为时钟使能线使用BUFGCTRL的CE引脚,所以选择信号必须满足设置时间要求。违反此设置时间可能会导致毛刺。

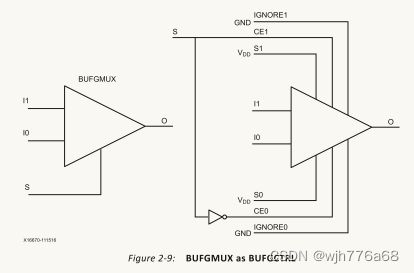

BUFGMUX和BUFGMUX_1

BUFGMUX is a clock buffer with two clock inputs, one clock output, and a select line. This primitive is based on BUFGCTRL with some pins connected to logic High or Low.

BUFFMUX是一个具有两个时钟输入、一个时钟输出和一条选择线的时钟缓冲器。此基元基于BUFGCTRL,其中一些引脚连接到逻辑高或低。

Figure 2-9 illustrates the relationship of BUFGMUX and BUFGCTRL. The LOC constraint is available for manually placing the BUFGMUX and BUFGCTRL locations. See the Vivado Design Suite User Guide: Using Constraints (UG903) [Ref 4] for more information.

图2-9说明了BUFGMUX和BUFGCTRL的关系。LOC约束可用于手动放置BUFGMUX和BUFGCTRL位置。有关更多信息,请参阅Vivado Design Suite用户指南:使用约束(UG903)[参考文献4]。

Because BUFGMUX uses the CE pins as select pins, when using the select, the setup time requirement must be met. Violating this setup time can result in a glitch.

因为BUFFMUX使用CE引脚作为选择引脚,所以在使用选择时,必须满足设置时间要求。违反此设置时间可能会导致毛刺。

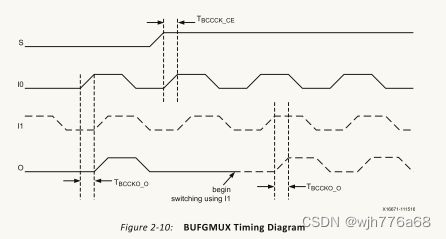

Switching conditions for BUFGMUX are the same as the CE pins on BUFGCTRL. Figure 2-10 illustrates the timing diagram for BUFGMUX.

BUFGMUX的开关条件与BUFGCTRL上的CE引脚相同。图2-10展示了BUFFMUX的时序图。

-

The current clock is I0.

-

S is activated High.

-

If I0 is currently High, the multiplexer waits for I0 to deassert Low.

-

After I0 is Low, the multiplexer output stays Low until I1 transitions from High to Low.

-

When I1 transitions from High to Low, the output switches to I1.

-

If setup/hold times are met, no glitches or short pulses can appear on the output.

-

当前时钟为I0。

-

S激活为高。

-

如果I0当前为高电平,多路复用器将等待I0去断言低电平。

-

在I0为低电平之后,多路复用器输出保持低电平,直到I1从高电平转换为低电平。

-

当I1从高电平转换到低电平时,输出切换到I1。

-

如果满足设置/保持时间,输出上不会出现毛刺或短脉冲。

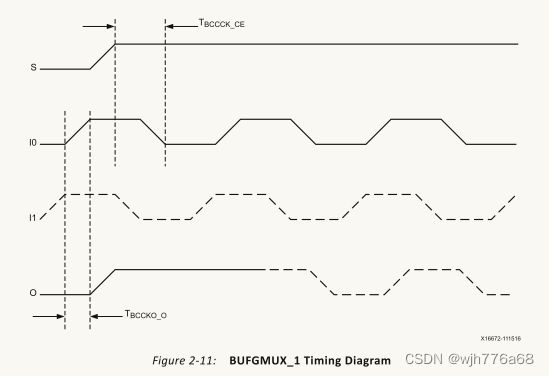

BUFGMUX_1 is rising-edge sensitive and held at High prior to input switch. Figure 2-11 illustrates the timing diagram for BUFGMUX_1. The LOC constraint is available for manually placing the BUFGMUX and BUFGMUX_1 locations. See the Vivado Design Suite User Guide: Using Constraints (UG903) [Ref 4] for more information.

BUFGMUX_1 对上升沿敏感,并在输入切换之前保持在高电平。图 2-11 给出了 BUFGMUX_1 的时序图。 LOC 约束可用于手动放置 BUFGMUX 和 BUFGMUX_1 位置。请参阅《Vivado Design Suite 用户指南:使用约束》(UG903) [参考资料 4] 了解更多信息。

在图2-11中:

-

The current clock is I0.

-

S is activated High.

-

If I0 is currently Low, the multiplexer waits for I0 to be asserted High.

-

After I0 is High, the multiplexer output stays High until I1 transitions from Low to High.

-

When I1 transitions from Low to High, the output switches to I1.

-

If setup/hold times are met, no glitches or short pulses can appear on the output.

-

当前时钟为I0。

-

S 被激活为高电平。

-

如果I0 当前为低电平,多路复用器将等待I0 被置为高电平。

-

I0 为高电平后,多路复用器输出保持高电平,直到I1 从低电平转换为高电平。

-

当I1 从低电平转换为高电平时,输出切换至I1。

-

如果满足建立/保持时间,则输出上不会出现毛刺或短脉冲。

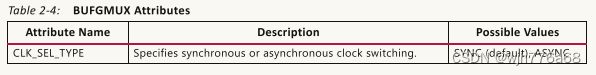

Table 2-4 summarizes the attributes for the BUFGMUX primitive.

表 2-4 总结了 BUFGMUX 原语的属性。

| 属性名称 | 描述 | 可行值 |

|---|---|---|

| CLK_SEL_TYPE | 指定同步或异步时钟切换。 | SYNC, ASYNC |

BUFGMUX_CTRL

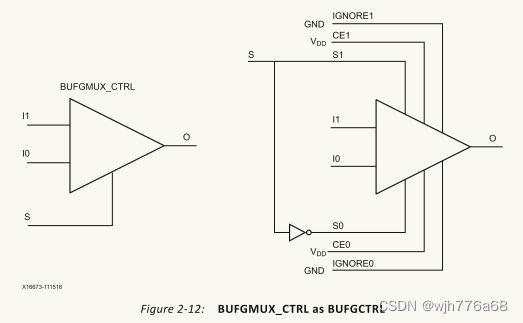

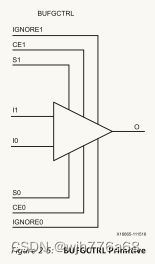

BUFGMUX_CTRL is a clock buffer with two clock inputs, one clock output, and a select line. This primitive is based on BUFGCTRL with some pins connected to logic High or Low. Figure 2-12 illustrates the relationship of BUFGMUX_CTRL and BUFGCTRL.

BUFGMUX_CTRL 是一个时钟缓冲器,具有两个时钟输入、一个时钟输出和一条选择线。该原语基于 BUFGCTRL,其中一些引脚连接到逻辑高电平或低电平。 BUFGMUX_CTRL 和 BUFGCTRL 的关系如图 2-12 所示。

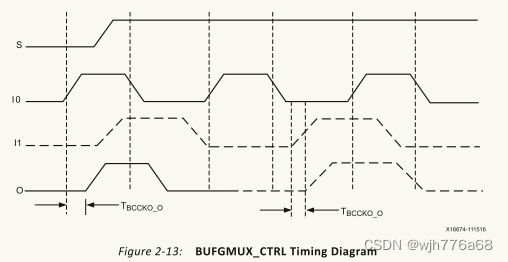

BUFGMUX_CTRL uses the S pins as select pins. S can switch anytime without causing a glitch. The setup/hold time on S is for determining whether the output passes an extra pulse of the previously selected clock before switching to the new clock. If S changes as shown in Figure 2-13 prior to the setup time TBCCCK_S and before I0 transitions from High to Low, the output does not pass an extra pulse of I0. If S changes following the hold time for S, the output passes an extra pulse. If S violates the setup/hold requirements, the output might pass the extra pulse but it will not glitch. In any case, the output changes to the new clock within three clock cycles of the slower clock.

BUFGMUX_CTRL 使用 S 引脚作为选择引脚。 S 可以随时切换而不会造成故障。 S 上的建立/保持时间用于确定在切换到新时钟之前输出是否通过先前选择的时钟的额外脉冲。如果 S 在建立时间 TBCCCK_S 之前以及 I0 从高电平转换为低电平之前发生如图 2-13 所示的变化,则输出不会传递 I0 的额外脉冲。如果 S 在 S 的保持时间之后发生变化,则输出会传递一个额外的脉冲。如果 S 违反建立/保持要求,输出可能会传递额外脉冲,但不会出现毛刺。在任何情况下,输出都会在较慢时钟的三个时钟周期内更改为新时钟。

The setup/hold requirements for S0 and S1 are with respect to the falling clock edge, not the rising edge as for CE0 and CE1.

S0 和 S1 的建立/保持要求是相对于时钟下降沿的,而不是 CE0 和 CE1 的上升沿。

Switching conditions for BUFGMUX_CTRL are the same as the S pin of BUFGCTRL.

Figure 2-13 illustrates the timing diagram for BUFGMUX_CTRL.

BUFGMUX_CTRL 的开关条件与 BUFGCTRL 的 S 引脚相同。图 2-13 说明了 BUFGMUX_CTRL 的时序图。

Other capabilities of the BUFGMUX_CTRL primitive are:

-

I0 and I1 inputs can be preselected after configuration.

-

Initial output can be selected as High or Low after configuration.

BUFGMUX_CTRL 原语的其他功能包括:

-

配置后可以预先选择 I0 和 I1 输入。

-

配置后,初始输出可以选择为高或低。