- 分布式学习笔记_04_复制模型

NzuCRAS

分布式学习笔记架构后端

常见复制模型使用复制的目的在分布式系统中,数据通常需要被分布在多台机器上,主要为了达到:拓展性:数据量因读写负载巨大,一台机器无法承载,数据分散在多台机器上仍然可以有效地进行负载均衡,达到灵活的横向拓展高容错&高可用:在分布式系统中单机故障是常态,在单机故障的情况下希望整体系统仍然能够正常工作,这时候就需要数据在多台机器上做冗余,在遇到单机故障时能够让其他机器接管统一的用户体验:如果系统客户端分布

- 《分片终章的哈希裂痕:藏在数据拼接里的隐形逻辑》

前端

在大文件分片传输里,有一个令人费解的现象:当所有分片的校验都显示正常,拼接后的整体文件却与源文件的哈希值不符,而问题往往精准地指向最后一片。这并非偶然的技术故障,而是数据传输链条中多重隐形逻辑交织的必然结果,如同钟表的齿轮在最后一圈突然出现难以察觉的错位。文件被切割成固定大小的分片时,最后一片往往是规则的例外。它如同拼图中形状特异的收尾piece,尺寸可能小于其他分片,却承担着衔接整体的关键作用。

- 基于开源AI智能名片链动2+1模式与S2B2C商城小程序的渠道选择策略研究

说私域

人工智能小程序

摘要:在数字化商业环境下,品牌与产品的渠道选择对其市场推广和运营成功至关重要。本文聚焦于如何依据自身品牌和产品特性,结合开源AI智能名片链动2+1模式与S2B2C商城小程序,运用科学的渠道选择方法,慎重挑选1-2个适宜平台,集中资源发力并取得成绩后再拓展其他渠道。通过理论分析与案例研究,探讨该策略的有效性和可行性,为企业渠道布局提供参考。关键词:渠道选择;开源AI智能名片;链动2+1模式;S2B2

- ssrf漏洞复现

ξ流ぁ星ぷ132

安全

目录基础环境查看phpinfo发现线索探测端口+gopher协议基础环境这里发现一些基础协议呗过滤掉了。但是有个提示的info,于是先看看查看phpinfo发现线索发现这台主机的地址了,于是猜测这个网段应该还有其他主机,试了一下172.21.0.1:80172.21.0.3:80果然如下(0.1是陷阱就不浪费时间了,)探测端口+gopher协议然后对这个172.21.0.3这个主机探测端口发现63

- 被动降噪的概念及编程实现

CodeByte

人工智能算法javascript编程

被动降噪是指通过编程技术和算法,对输入的数据进行处理,以减少或消除其中的噪声。噪声可以是各种形式的干扰,例如来自传感器、通信信号或其他外部源的干扰。在本文中,我们将探讨被动降噪的意义以及如何使用编程来实现这一目标。被动降噪的意义:噪声对数据的准确性和可靠性产生负面影响。在许多应用领域,例如图像处理、音频处理和信号处理中,噪声的存在可能导致数据质量下降,使得后续的分析和处理变得困难。因此,被动降噪技

- 音频被动降噪技术

悟空胆好小

音频相关音视频

音频被动降噪技术音频被动降噪技术是一种通过物理结构和材料设计来减少或隔离外部噪声的降噪方式,其核心原理是通过物理屏障或吸声材料来阻断或吸收声波,从而降低环境噪声对听觉体验的影响。以下将从技术原理、应用场景、优缺点及与其他降噪技术的对比等方面进行详细分析。一、被动降噪技术的原理被动降噪技术(PassiveNoiseCancellation,PNC)主要依赖于耳机的物理结构和材料设计,通过以下几种方式

- 【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(Advanced RAG[1])其他Query优化相关策略?

985小水博一枚呀

AI大模型学习路线人工智能学习langchain

【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(AdvancedRAG[1])其他Query优化相关策略?【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(AdvancedRAG[1])其他Query优化相关策略?文章目录【AI大模型学习路线】第三阶段之RAG与LangChain——第十六章(AdvancedRAG[1])其他Query优化相关策略?一

- redis集群之Sentinel哨兵高可用

会飞的爱迪生

redisredissentinelbootstrap

Sentinel是官网推荐的高可用(HA)解决方案,可以实现redis的高可用,即主挂了从代替主工作,在一台单独的服务器上运行多个sentinel,去监控其他服务器上的redismaster-slave状态(可以监控多个master-slave),当发现master宕机后sentinel会在slave中选举并启动新的master。至少需要3台redis才能建立起基于哨兵的reids集群。一、通过s

- QML与C++相互调用函数并获得返回值

cpp_learners

QMLc++QMLqt

这篇博客主要讲解在qml端如何直接调用c++的函数并获得返回值,在c++端如何直接调用qml的函数并获得返回值;主要以map或者jsonobject、list或者jsonarray为主!其他单个类型,常见的类型,例如QString、int等,就不演示了;一通百通。目录1准备工作1.1C++端1.2QML端2qml端直接调用c++端函数3c++端直接调用qml端函数3.1调用qml的qmlFuncO

- .NET 一款基于BGInfo的红队内网渗透工具

dot.Net安全矩阵

网络.net安全.netcoreweb安全矩阵

01阅读须知此文所提供的信息只为网络安全人员对自己所负责的网站、服务器等(包括但不限于)进行检测或维护参考,未经授权请勿利用文章中的技术资料对任何计算机系统进行入侵操作。利用此文所提供的信息而造成的直接或间接后果和损失,均由使用者本人负责。本文所提供的工具仅用于学习,禁止用于其他方面02基本介绍在内网渗透过程中,白名单绕过是红队常见的技术需求。Sharp4Bginfo.exe是一款基于微软签名工具

- iOS 多个线程对数组操作(遍历,插入,删除),实现一个线程安全的NSMutabeArray

//联系人:石虎QQ:1224614774昵称:嗡嘛呢叭咪哄一、概念1.含义:@synchronized(self){}//这个其实就是一个加锁。如果self其他线程访问,则会阻塞。这样做一般是用来对单2.重写构造方法@interfaceSHSafetyArray:NSObject{@privateNSMutableArray*_mutableArray;//声明数组}//遍历加锁-(void)m

- 【Android】安卓四大组件之广播接收器(Broadcast Receiver):从基础到进阶

m0_59734531

AndroidandroidjavaBoradcast安卓四大组件

在Android开发中,广播接收器(BroadcastReceiver)是一个非常重要的组件,它能帮助应用接收来自系统或其他应用的事件通知,实现跨组件、跨应用的通信。大家可以把广播接收器想象成一个“收音机”。它的作用是监听系统或应用发出的“广播消息”,并在收到消息后执行相应的操作。(一)基础概念BroadcastReceiver用于监听系统或应用发出的广播事件,实现跨组件通信。其特点是发送方无需关

- 【Android】安卓四大组件之内容提供者(ContentProvider):从基础到进阶

m0_59734531

AndroidandroidJavaContentProvider安卓四大组件

你手机里的通讯录,存储了所有联系人的信息。如果你想把这些联系人信息分享给其他App,就可以通过ContentProvider来实现。。一、什么是ContentProviderContentProvider是Android四大组件之一,负责实现跨应用程序的数据共享与访问,通过统一接口封装数据存储细节,提供标准化操作方式。其中主要功能包括:数据抽象层:将应用内部的数据(如SQLite数据库、文

- Ubuntu 服务器虚拟主机,ubuntu云服务器虚拟机

Gamer42

Ubuntu服务器虚拟主机

ubuntu云服务器虚拟机内容精选换一换通过云服务器或者外部镜像文件创建私有镜像时,如果云服务器或镜像文件所在虚拟机的网络配置是静态IP地址时,您需要修改网卡属性为DHCP,以使私有镜像发放的新云服务器可以动态获取IP地址。本节以WindowsServer2008R2操作系统为例。其他操作系统配置方法略有区别,请参考对应操作系统的相关资料进行操作,文档中不对此进行详细说明后端虚拟机绑定EIP。登录

- 《C++性能优化指南》 linux版代码及原理解读 第四章

v俊逸

C++性能优化指南性能优化C++性能优化指南性能优化

目录概述为什么字符串很麻烦字符串是动态分配的字符串赋值背后的操作如何面对字符串会进行大量复制写时复制COW(copyonwrite)尝试优化字符串避免临时字符串通过预留存储空间减少内存分配通过传递引用减少实参复制使用迭代器操作减少循环中的比较操作减少返回值的复制还没有结束,使用字符数组代替字符串再次优化字符串尝试其他的算法叠加以前的优化方式使用其他的编译器使用其他字符串的库功能丰富的字符串库使用s

- 如何在 Linux 上安装 RTX 5090 / 5080 /5070 Ti / 5070 驱动程序 — 详细指南

知识大胖

NVIDIAGPU和大语言模型开发教程linux运维服务器

简介为了获得最佳性能,您需要在Linux上运行5090/5080/5070Ti/5070或其他50系列GPU(或Windows上的WSL)。这篇文章将包含有关如何操作的详细指南。主线内核和驱动程序怪癖之旅Nvidia50系列GPU拥有最新的Nvidia技术。但是,新硬件需要一些新软件或更新,这需要一些耐心。如果您在这里,您可能会遇到Ubuntu默认设置的障碍。不要害怕!我最近自己摸索了这个迷宫,结

- AnythingLLM教程系列之 04 AnythingLLM 允许您以正确的格式导出聊天日志,以构建 GPT-3.5 和 OpenAI 上其他可用模型的微调模型(教程含安装步骤)

知识大胖

NVIDIAGPU和大语言模型开发教程llama3aianythinllmllama

什么是AnythingLLM?AnythingLLM是最易于使用的一体化AI应用程序,可以执行RAG、AI代理等操作,且无需任何代码或基础设施难题。您需要为您的企业或组织提供一款完全可定制、私有且一体化的AI应用程序,该应用程序基本上是一个具有许可的完整ChatGPT,但具有任何LLM、嵌入模型或矢量数据库。如何安装《无需任何代码构建自己的大模型知识库:AnythingLLM最易于使用的一体化AI

- 解决Linux绑定失败地址已使用(端口被占用)的问题

誰能久伴不乏

linux服务器网络

文章目录解决`bindfailed:Addressalreadyinuse`问题一、问题原因1.**端口已经被其他程序占用**2.**端口处于`TIME_WAIT`状态**3.**未正确关闭套接字**二、如何排查和解决问题1.**确认端口是否被占用**2.**查找并杀掉占用端口的进程**3.**等待端口释放(`TIME_WAIT`状态)**4.**强制重用端口**(仅限开发环境)5.**使用其他端

- 如何查看自己本地的公网IP地址?内网环境网络如何开通服务器公网ip提供互联网访问?

搬码临时工

网络tcp/ip服务器

查看公网IP和开启公网地址提供互联网服务是作为网络管理员的必修课。代替路由映射的端口映射应用使用最广泛的就是nat123。内网发布网站或其他应用到外网访问,且本地无公网IP,或80和443端口被屏蔽,对于这些环境,就需要利用端口映射应用网络辅助来实现。一、如何查看自己本地的公网IP?登录你的路由器,看拨号状态那的WAN口的IP地址;如果你是光纤猫拨号,就需要登录光纤猫,看拨号状态那WAN口的IP地

- 【亲测免费】 Mamba:快速跨平台的包管理器

林梦雅

Mamba:快速跨平台的包管理器项目基础介绍和主要编程语言Mamba是一个用C++重新实现的Conda包管理器。它旨在提供比传统Conda更快的包管理和依赖解析速度。Mamba的核心部分使用C++编写,以确保高效性和性能。同时,Mamba也使用了Python和其他一些辅助语言来实现其功能。项目核心功能Mamba的核心功能包括:快速依赖解析:利用libsolv库进行高效的依赖解析,这是RedHat、

- GPT实操——利用GPT创建一个应用

狗木马

深度学习gpt-3gpt

功能描述信息查询:用户可以询问各种问题,如天气、新闻、股票等,机器人会返回相关信息。任务执行:用户可以要求机器人执行一些简单的任务,如设置提醒、发送邮件等。情感支持:机器人可以与用户进行情感交流,提供安慰和支持。个性化设置:用户可以自定义机器人的回复风格和偏好。技术栈前端:React.js后端:Node.js+Express数据库:MongoDB自然语言处理:OpenAIGPT-3API其他工具:

- docker常见问题解决方法

小王聊技术

docker

目录迁移至其他服务器清理Docker占用的磁盘空间常见问题:迁移至其他服务器1.将docker容器导出dockerexport-o保存路径/xxx.tar容器id2.将容器tar远程拷贝到新的服务器(从新的服务器上向老服务器上请求复制)scproot@服务器地址:/data/xxx.tar/root3.将导入的tar包转为镜像dockerimport-cxxx.tarimage_name:tag

- 微软语音合成标记语言SSML文档结构和事件(详细文档和实例)

阿酷tony

AI数字人微信语音合成microsoft微软语音SSML文档结构SSML结构SSML语音合成

说明:MicrosoftAzure中国技术文档网站,请访问https://docs.azure.cn包含输入文本的语音合成标记语言(SSML)确定了文本转语音输出的结构、内容和其他特征。例如,可以使用SSML来定义段落、句子、中断/暂停或静音。可以使用事件标记(例如书签或视素)来包装文本,这些标记可以稍后由应用程序处理。有关如何在SSML文档中构建元素的详细信息,请参阅以下部分。备注某些语音不支持

- 【电脑】主板的基础知识

Mike_Wuzy

电脑

主板(Motherboard)是计算机的核心组件之一,它将所有其他硬件部件连接在一起并协调它们的工作。以下是关于主板的详细知识:1.架构组成一个典型的主板通常由以下几个主要部分构成:芯片组(Chipset):分为南桥和北桥两个部分。北桥(Northbridge):负责处理高速数据传输,如连接内存控制器、显示接口等。现代CPU集成了北桥的功能,因此许多主板上已经不再有独立的北桥芯片。南桥(South

- NumPy-@运算符详解

GG不是gg

numpynumpy

NumPy-@运算符详解一、@运算符的起源与设计目标1.从数学到代码:符号的统一2.设计目标二、@运算符的核心语法与运算规则1.基础用法:二维矩阵乘法2.一维向量的矩阵语义3.高维数组:批次矩阵运算4.广播机制:灵活的形状匹配三、@运算符与其他乘法方式的核心区别1.对比`np.dot()`2.对比元素级乘法`*`3.对比`np.matrix`的`*`运算符四、典型应用场景:从基础到高阶1.深度学习

- mac下java的安装地址linux /usr/libexec/解释

Alien.L

linux服务器运维

在Linux系统中,/usr/libexec/目录通常包含一些不应由用户直接运行的系统服务和工具,而是由其他系统进程调用。这些工具和服务是由操作系统和软件包开发人员创建的,通常不是用户直接运行的。例如,一些守护进程和系统服务可能位于/usr/libexec/目录下,它们被设计为在系统启动时自动启动,以便在后台运行以提供某些功能或服务。通常,用户应该避免直接在/usr/libexec/目录下创建或修

- mac全选文字的快捷键_MACBOOK最全快捷键指南

彼得威

mac全选文字的快捷键

官方最新出炉的快捷键大全:剪切、拷贝、粘贴和其他常用快捷键Command-X:剪切所选项并拷贝到剪贴板。Command-C:将所选项拷贝到剪贴板。Command-V:将剪贴板的內容粘贴到当前文稿或应用中。Command-Z:撤销前一个命令。随后您可以按Command-Shift-z来重做,从而反向执行撤销命令。Command-A:全选各项。Command-F:查找文稿中的项目或打开“查找”窗口。C

- 【前端】接口日志追踪

毕业茄

前端

1.问题描述场景:前端提交数据后,接口回调再次添加参数,但页面跳转/刷新导致之前的console.log数据丢失。影响:无法追踪完整的请求流程,调试困难。2.环境信息项目说明浏览器GoogleChrome120+开发者工具ChromeDevTools技术栈前端:Vue/React/其他接口类型RESTfulAPI/GraphQL3.解决方案3.1保留控制台日志(推荐)步骤:打开Chrome开发者工

- Mac上的java_home命令的作用

https://my.oschina.net/shishaomeng/blog/537444摘要:刚上手Mac还是有些别扭的,尤其安装个JDK都跟Windows不一样,而且是完全的不同本文仅针对macosx10.5+,其他版本有可能出现不适.JDK安装JDK1.6安装系统默认自带jdk1.6,如因意外被卸载,可从如下地址下载安装:https://support.apple.com/kb/DL157

- 虚拟环境已安装该包,且已激活,但报错

排查原因:是否存在这样的现象命令结果condalist显示的是base环境的包piplist显示的是你当前虚拟环境的包激活了Conda的base环境,但运行的Python实际来自其他路径(如virtualenv创建的虚拟环境或系统Python)Python路径与Conda环境不一致我主要在base的基础上激活了新的虚拟环境,导致环境不一致解决:退出所有环境,重新激活虚拟环境验证是否一致

- mondb入手

木zi_鸣

mongodb

windows 启动mongodb 编写bat文件,

mongod --dbpath D:\software\MongoDBDATA

mongod --help 查询各种配置

配置在mongob

打开批处理,即可启动,27017原生端口,shell操作监控端口 扩展28017,web端操作端口

启动配置文件配置,

数据更灵活

- 大型高并发高负载网站的系统架构

bijian1013

高并发负载均衡

扩展Web应用程序

一.概念

简单的来说,如果一个系统可扩展,那么你可以通过扩展来提供系统的性能。这代表着系统能够容纳更高的负载、更大的数据集,并且系统是可维护的。扩展和语言、某项具体的技术都是无关的。扩展可以分为两种:

1.

- DISPLAY变量和xhost(原创)

czmmiao

display

DISPLAY

在Linux/Unix类操作系统上, DISPLAY用来设置将图形显示到何处. 直接登陆图形界面或者登陆命令行界面后使用startx启动图形, DISPLAY环境变量将自动设置为:0:0, 此时可以打开终端, 输出图形程序的名称(比如xclock)来启动程序, 图形将显示在本地窗口上, 在终端上输入printenv查看当前环境变量, 输出结果中有如下内容:DISPLAY=:0.0

- 获取B/S客户端IP

周凡杨

java编程jspWeb浏览器

最近想写个B/S架构的聊天系统,因为以前做过C/S架构的QQ聊天系统,所以对于Socket通信编程只是一个巩固。对于C/S架构的聊天系统,由于存在客户端Java应用,所以直接在代码中获取客户端的IP,应用的方法为:

String ip = InetAddress.getLocalHost().getHostAddress();

然而对于WEB

- 浅谈类和对象

朱辉辉33

编程

类是对一类事物的总称,对象是描述一个物体的特征,类是对象的抽象。简单来说,类是抽象的,不占用内存,对象是具体的,

占用存储空间。

类是由属性和方法构成的,基本格式是public class 类名{

//定义属性

private/public 数据类型 属性名;

//定义方法

publ

- android activity与viewpager+fragment的生命周期问题

肆无忌惮_

viewpager

有一个Activity里面是ViewPager,ViewPager里面放了两个Fragment。

第一次进入这个Activity。开启了服务,并在onResume方法中绑定服务后,对Service进行了一定的初始化,其中调用了Fragment中的一个属性。

super.onResume();

bindService(intent, conn, BIND_AUTO_CREATE);

- base64Encode对图片进行编码

843977358

base64图片encoder

/**

* 对图片进行base64encoder编码

*

* @author mrZhang

* @param path

* @return

*/

public static String encodeImage(String path) {

BASE64Encoder encoder = null;

byte[] b = null;

I

- Request Header简介

aigo

servlet

当一个客户端(通常是浏览器)向Web服务器发送一个请求是,它要发送一个请求的命令行,一般是GET或POST命令,当发送POST命令时,它还必须向服务器发送一个叫“Content-Length”的请求头(Request Header) 用以指明请求数据的长度,除了Content-Length之外,它还可以向服务器发送其它一些Headers,如:

- HttpClient4.3 创建SSL协议的HttpClient对象

alleni123

httpclient爬虫ssl

public class HttpClientUtils

{

public static CloseableHttpClient createSSLClientDefault(CookieStore cookies){

SSLContext sslContext=null;

try

{

sslContext=new SSLContextBuilder().l

- java取反 -右移-左移-无符号右移的探讨

百合不是茶

位运算符 位移

取反:

在二进制中第一位,1表示符数,0表示正数

byte a = -1;

原码:10000001

反码:11111110

补码:11111111

//异或: 00000000

byte b = -2;

原码:10000010

反码:11111101

补码:11111110

//异或: 00000001

- java多线程join的作用与用法

bijian1013

java多线程

对于JAVA的join,JDK 是这样说的:join public final void join (long millis )throws InterruptedException Waits at most millis milliseconds for this thread to die. A timeout of 0 means t

- Java发送http请求(get 与post方法请求)

bijian1013

javaspring

PostRequest.java

package com.bijian.study;

import java.io.BufferedReader;

import java.io.DataOutputStream;

import java.io.IOException;

import java.io.InputStreamReader;

import java.net.HttpURL

- 【Struts2二】struts.xml中package下的action配置项默认值

bit1129

struts.xml

在第一部份,定义了struts.xml文件,如下所示:

<!DOCTYPE struts PUBLIC

"-//Apache Software Foundation//DTD Struts Configuration 2.3//EN"

"http://struts.apache.org/dtds/struts

- 【Kafka十三】Kafka Simple Consumer

bit1129

simple

代码中关于Host和Port是割裂开的,这会导致单机环境下的伪分布式Kafka集群环境下,这个例子没法运行。

实际情况是需要将host和port绑定到一起,

package kafka.examples.lowlevel;

import kafka.api.FetchRequest;

import kafka.api.FetchRequestBuilder;

impo

- nodejs学习api

ronin47

nodejs api

NodeJS基础 什么是NodeJS

JS是脚本语言,脚本语言都需要一个解析器才能运行。对于写在HTML页面里的JS,浏览器充当了解析器的角色。而对于需要独立运行的JS,NodeJS就是一个解析器。

每一种解析器都是一个运行环境,不但允许JS定义各种数据结构,进行各种计算,还允许JS使用运行环境提供的内置对象和方法做一些事情。例如运行在浏览器中的JS的用途是操作DOM,浏览器就提供了docum

- java-64.寻找第N个丑数

bylijinnan

java

public class UglyNumber {

/**

* 64.查找第N个丑数

具体思路可参考 [url] http://zhedahht.blog.163.com/blog/static/2541117420094245366965/[/url]

*

题目:我们把只包含因子

2、3和5的数称作丑数(Ugly Number)。例如6、8都是丑数,但14

- 二维数组(矩阵)对角线输出

bylijinnan

二维数组

/**

二维数组 对角线输出 两个方向

例如对于数组:

{ 1, 2, 3, 4 },

{ 5, 6, 7, 8 },

{ 9, 10, 11, 12 },

{ 13, 14, 15, 16 },

slash方向输出:

1

5 2

9 6 3

13 10 7 4

14 11 8

15 12

16

backslash输出:

4

3

- [JWFD开源工作流设计]工作流跳跃模式开发关键点(今日更新)

comsci

工作流

既然是做开源软件的,我们的宗旨就是给大家分享设计和代码,那么现在我就用很简单扼要的语言来透露这个跳跃模式的设计原理

大家如果用过JWFD的ARC-自动运行控制器,或者看过代码,应该知道在ARC算法模块中有一个函数叫做SAN(),这个函数就是ARC的核心控制器,要实现跳跃模式,在SAN函数中一定要对LN链表数据结构进行操作,首先写一段代码,把

- redis常见使用

cuityang

redis常见使用

redis 通常被认为是一个数据结构服务器,主要是因为其有着丰富的数据结构 strings、map、 list、sets、 sorted sets

引入jar包 jedis-2.1.0.jar (本文下方提供下载)

package redistest;

import redis.clients.jedis.Jedis;

public class Listtest

- 配置多个redis

dalan_123

redis

配置多个redis客户端

<?xml version="1.0" encoding="UTF-8"?><beans xmlns="http://www.springframework.org/schema/beans" xmlns:xsi=&quo

- attrib命令

dcj3sjt126com

attr

attrib指令用于修改文件的属性.文件的常见属性有:只读.存档.隐藏和系统.

只读属性是指文件只可以做读的操作.不能对文件进行写的操作.就是文件的写保护.

存档属性是用来标记文件改动的.即在上一次备份后文件有所改动.一些备份软件在备份的时候会只去备份带有存档属性的文件.

- Yii使用公共函数

dcj3sjt126com

yii

在网站项目中,没必要把公用的函数写成一个工具类,有时候面向过程其实更方便。 在入口文件index.php里添加 require_once('protected/function.php'); 即可对其引用,成为公用的函数集合。 function.php如下:

<?php /** * This is the shortcut to D

- linux 系统资源的查看(free、uname、uptime、netstat)

eksliang

netstatlinux unamelinux uptimelinux free

linux 系统资源的查看

转载请出自出处:http://eksliang.iteye.com/blog/2167081

http://eksliang.iteye.com 一、free查看内存的使用情况

语法如下:

free [-b][-k][-m][-g] [-t]

参数含义

-b:直接输入free时,显示的单位是kb我们可以使用b(bytes),m

- JAVA的位操作符

greemranqq

位运算JAVA位移<<>>>

最近几种进制,加上各种位操作符,发现都比较模糊,不能完全掌握,这里就再熟悉熟悉。

1.按位操作符 :

按位操作符是用来操作基本数据类型中的单个bit,即二进制位,会对两个参数执行布尔代数运算,获得结果。

与(&)运算:

1&1 = 1, 1&0 = 0, 0&0 &

- Web前段学习网站

ihuning

Web

Web前段学习网站

菜鸟学习:http://www.w3cschool.cc/

JQuery中文网:http://www.jquerycn.cn/

内存溢出:http://outofmemory.cn/#csdn.blog

http://www.icoolxue.com/

http://www.jikexue

- 强强联合:FluxBB 作者加盟 Flarum

justjavac

r

原文:FluxBB Joins Forces With Flarum作者:Toby Zerner译文:强强联合:FluxBB 作者加盟 Flarum译者:justjavac

FluxBB 是一个快速、轻量级论坛软件,它的开发者是一名德国的 PHP 天才 Franz Liedke。FluxBB 的下一个版本(2.0)将被完全重写,并已经开发了一段时间。FluxBB 看起来非常有前途的,

- java统计在线人数(session存储信息的)

macroli

javaWeb

这篇日志是我写的第三次了 前两次都发布失败!郁闷极了!

由于在web开发中常常用到这一部分所以在此记录一下,呵呵,就到备忘录了!

我对于登录信息时使用session存储的,所以我这里是通过实现HttpSessionAttributeListener这个接口完成的。

1、实现接口类,在web.xml文件中配置监听类,从而可以使该类完成其工作。

public class Ses

- bootstrp carousel初体验 快速构建图片播放

qiaolevip

每天进步一点点学习永无止境bootstrap纵观千象

img{

border: 1px solid white;

box-shadow: 2px 2px 12px #333;

_width: expression(this.width > 600 ? "600px" : this.width + "px");

_height: expression(this.width &

- SparkSQL读取HBase数据,通过自定义外部数据源

superlxw1234

sparksparksqlsparksql读取hbasesparksql外部数据源

关键字:SparkSQL读取HBase、SparkSQL自定义外部数据源

前面文章介绍了SparSQL通过Hive操作HBase表。

SparkSQL从1.2开始支持自定义外部数据源(External DataSource),这样就可以通过API接口来实现自己的外部数据源。这里基于Spark1.4.0,简单介绍SparkSQL自定义外部数据源,访

- Spring Boot 1.3.0.M1发布

wiselyman

spring boot

Spring Boot 1.3.0.M1于6.12日发布,现在可以从Spring milestone repository下载。这个版本是基于Spring Framework 4.2.0.RC1,并在Spring Boot 1.2之上提供了大量的新特性improvements and new features。主要包含以下:

1.提供一个新的sprin

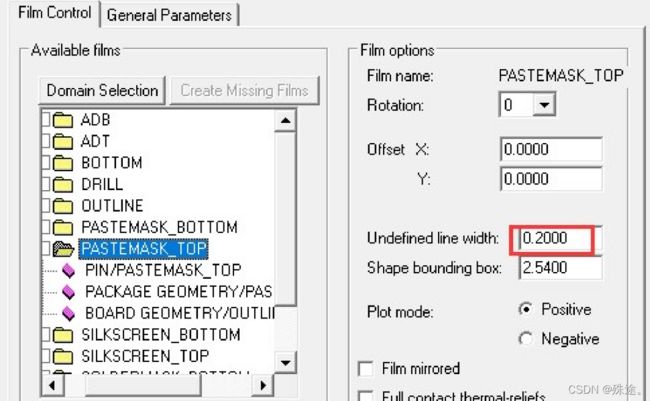

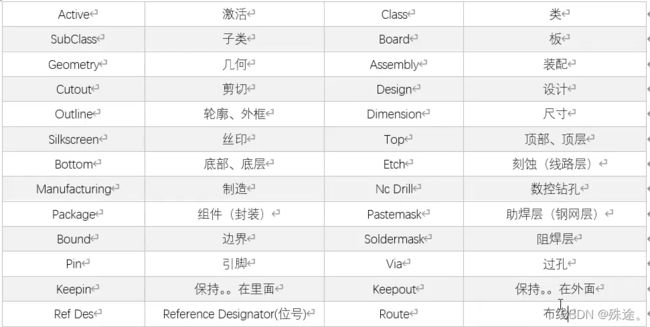

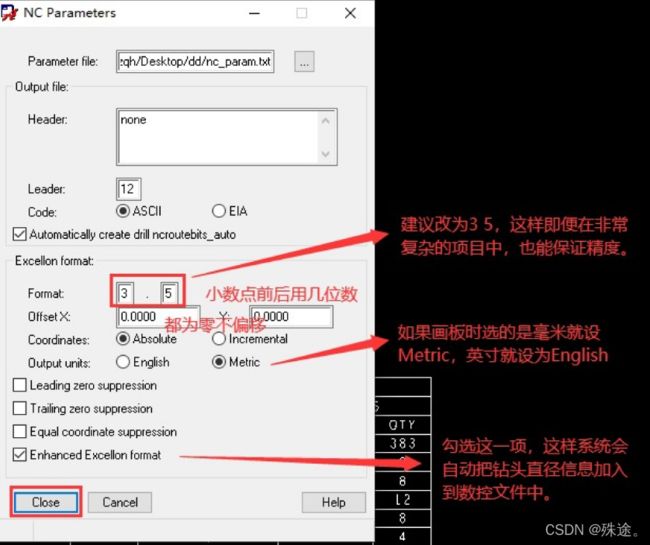

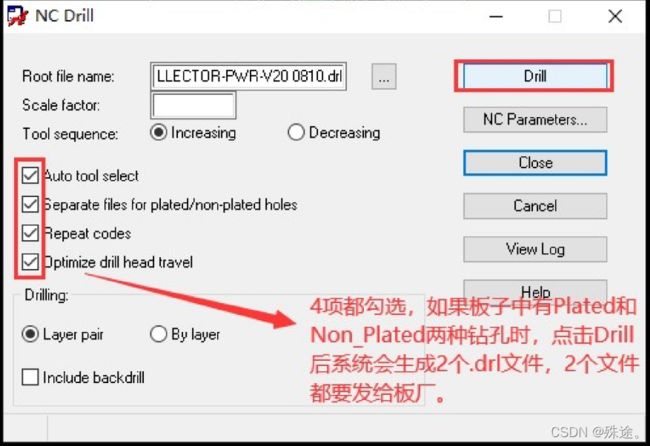

如果有盲埋孔则选择“By layer”否则选择“Layer pair”,其它的按默认选项。

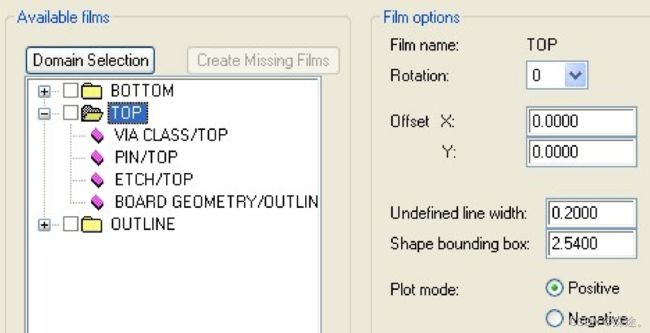

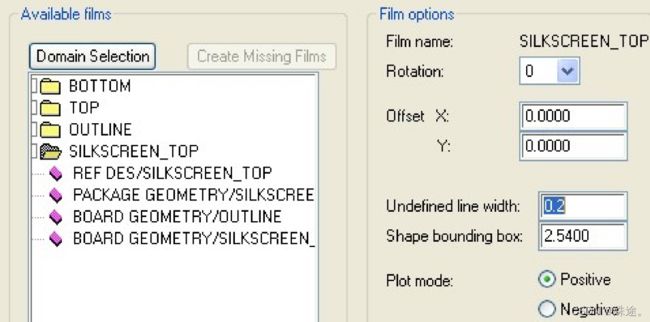

如果有盲埋孔则选择“By layer”否则选择“Layer pair”,其它的按默认选项。 SILKSCREEN_TOP/SILKSCREEN_BOTTOM

SILKSCREEN_TOP/SILKSCREEN_BOTTOM Soldermask_Top /Soldermask_BOTTOM

Soldermask_Top /Soldermask_BOTTOM 从上图可以看到Soldermask_Top 只勾选了pin,via 可选可不选;钻孔分为焊盘Pad 和过孔Via,一般情况下我们在做PCB 时,为了降低回流路径会放置很多过孔,以及线路换层时使用过孔连接不同层的内容,大多数情况对这种过孔盖绿油的(因此上述箭头处不勾选via,如果要不盖绿油,也可以勾选,看需求,像测试点的那种是要勾选的;有人会疑问,有的器件的过孔需要到时我焊接啊,盖了绿油怎么焊锡啊,出现这种疑问是没有搞明白Pad 和Via的区别,Pad 也可以钻孔的,Pad 组成了Pin,因此上图中方框勾选了,就不盖绿油了,到时钻孔后就可以正常焊接;而Via 就是纯的过孔,仅仅起到上下层的连通作用,不存在器件的焊接)

从上图可以看到Soldermask_Top 只勾选了pin,via 可选可不选;钻孔分为焊盘Pad 和过孔Via,一般情况下我们在做PCB 时,为了降低回流路径会放置很多过孔,以及线路换层时使用过孔连接不同层的内容,大多数情况对这种过孔盖绿油的(因此上述箭头处不勾选via,如果要不盖绿油,也可以勾选,看需求,像测试点的那种是要勾选的;有人会疑问,有的器件的过孔需要到时我焊接啊,盖了绿油怎么焊锡啊,出现这种疑问是没有搞明白Pad 和Via的区别,Pad 也可以钻孔的,Pad 组成了Pin,因此上图中方框勾选了,就不盖绿油了,到时钻孔后就可以正常焊接;而Via 就是纯的过孔,仅仅起到上下层的连通作用,不存在器件的焊接)