~Datasheet - Clock

==== 基本概念 ====

- 时钟电源管理模块 包含了 3部分:Clock 控制、USB 控制、POWER 控制。

- 时钟控制逻辑单元 能够产生 s3c2440需生要的时钟信号, 包括:

1)CPU使用的主频 FCLK;

2)AHB总线设备使用的 HCLK;

3)APB总线设备使用的 PCLK

锁相环:

2440内部有2个PLL(锁相环):

MPLL: 一个对应FCLK、HCLK、PCLK,

UPLL: 另外一个对应的是USB使用(48MHz)。

备注==>

----AHB总线----

AMBA 2.0规范包括四个部分:AHB、ASB、APB和Test Methodology。

AHB的相互连接采用了传统的带有主模块和从模块的共享总线,接口与互连功能分离,这对芯片上模块之间的互连具有重要意义。 AMBA已不仅是一种总线,更是一种带有接口模块的互连体系。

----APB总线----

APB主要用于低带宽的周边外设之间的连接,例如UART、1284等,它的总线架构不像AHB支持多个主模块,在APB里面唯一的主模块就是APB桥。其特性包括:

两个时钟周期传输;

无需等待周期和回应信号;

控制逻辑简单,只有四个控制信号。

补充1==>

7.1功能描述

7.1.1时钟结构

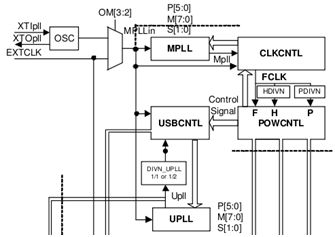

主时钟源来自 外部晶振(XTIPLL) 或者是 外部时钟(EXTCLK). 时钟生成器包含了一个振荡器(振荡放大器),其连接外部晶振,并且还有 2个 PLL,可以 产生满足 s3c2440所需的高频时钟。

1)FLCK、HCLK和PCLK的关系

S3C2440有三个时钟FLCK、HCLK和PCLK

s3c2440官方手册上说P7-8写到:

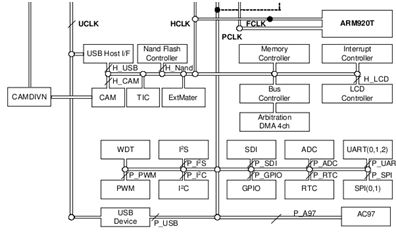

FCLK is used by ARM920T,内核时钟,主频。

HCLK is used for AHB bus, which is used by the ARM920T, the memory controller, the interrupt controller, the LCD controller, the DMA and USB host block.也就是总线时钟,包括USB时钟。

PCLK is used for APB bus, which is used by the peripherals such as WDT, IIS, I2C, PWM timer, MMC interface,ADC, UART, GPIO, RTC and SPI.即IO接口时钟,例如串口的时钟设置就是从PCLK来的;

那么这三个时钟是什么关系呢?

这三个时钟通常设置为1:4:8,1:3:6的分频关系,也就说如果主频FLCK是400MHz,按照1:4:8的设置,那么HLCK是100MHz,PLCK是50MHz

寄存器CLKDIVN表明并设置了这三个时钟的关系

如果CLKDIVN设置为0x5,那么比例即为1:4:8,前提是CAMDIVN[9]为0.

2)输入时钟FIN与主频FCLK的关系

现代的CPU基本上都使用了比主频低的多的时钟输入,在CPU内部使用锁相环进行倍频。

对于S3C2440,常用的输入时钟FIN有两种:12MHz 和 16.9344MHz,

那么CPU是如何将FIN倍频为FCLK的呢 ?

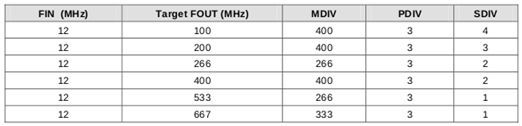

S3C2440使用了三个倍频因子: MDIV、PDIV和 SDIV来设置将FIN倍频为MPLL,也就是FCLK。

MPLL=(2*m*FIN)/(p*2^s) where m=(MDIV+8), p=(PDIV+2), s="SDIV"

寄存器MPLLCON就是用来设置倍频因子的。

理论上,你可以通过设置该寄存器来实现不同的频率,然而,由于实际存在的各种约束关系,设置一个适当的频率并不容易,手册上列出了一些常用频率的表格,

例如,假设输入时钟: FIN=16.9344M,MDIV=110, PDIV="3", SDIV="1", 利用上面的公式: FCLK=2*16.9344*(110+8)/((2+3)*2)=399.65

1、 虽然 MPLL在 reset以后就开始工作,但是 MPLL输出(Mpll)没有作为系统时钟来使用,直到软件对 MPLLCON寄存器写入有效设置。

有效设置前,来自外部晶振或外部时钟源的时钟将直接被当作系统时钟来使用。就算是用户不想改变 MPLLCON寄存器的默认值,用户应该再重新写入 MPLLCON寄存器一次相同的值。

2、 当 OM[1:0]=11时,OM[3:2]被用于决定 test 模式。

在设置P M S3个值后,需要设置CLKDIVN 寄存器的值。CLKDIVN 的值设置在PLL 锁定期后有效。这个值也对复位和改变电源管理模式也是可用的。 设置值在1.5HCLK 后有效,1 个HCLK 可以CLKDIVN 寄存器的值从默认(1:1:1)到其 他分频比(1:1:2,1:2:2,1:2:4)改变有效。

3)关于USB时钟

S3C2440有两个锁相环,

一个主锁相环MPLL提供给FCLK的,

UPLL是提供给USB时钟(48MHz)的,与MPLL一样,UPLL的产生也是通过UPLLCON寄存器设置分频因子得到,计算公式稍有不同:

UPLL=(m*FIN)/(p*2^s) where m=(MDIV+8), p=(PDIV+2), s="SDIV",

同样,可以通过查表得到一个合适的值。

最后值得一提的是,在CLKDIVN的第三位DIVN_UPLL用来设置USB时钟UCLK和UPLL的关系,如果UPLL已经是48Mhz了,那么这一位应该设置为0,表示1:1的关系,否则是1:2的关系。

http://student.csdn.net/space.php?uid=91306&do=blog&id=14643

补充2==>

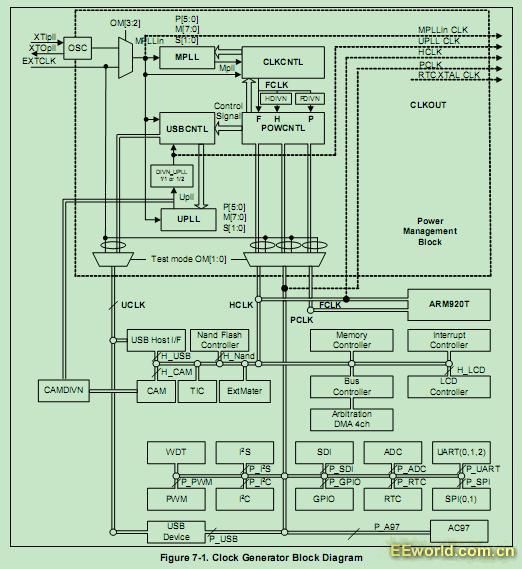

以上图时钟发生器模块图为主,讲解S3C2440时钟模块原理。

主时钟源来自外部晶振(XTIpll)或者外部时钟。

用芯片引脚OM[3:2]来选择,一般情况下,OM3和OM2接地,这样,主时钟源即为外部晶振(此 时USB时钟源也是外部晶振)。

集成电路MPLL产生一个在频率和相位上同步于参考输入信号的输出信号,计算公式为:

Mpll=(2*m*Fin)(p*2^s)m=M(分频系数M)+8, p=P(分频系数P)+2

集成电路UPLL的工作原理与MPLL相同。

M、P、S的值由PLL控制寄存器(MPLLCON和UPLLCON)来设置。

图中的CLKCNTL模块主要由时钟控制寄存器CLKCON和慢速时钟控制寄存器CLKSLOW两个寄存器组成,

一方面,它可以控制外围设备的时钟使能, 从而实现功耗控制;

另一方面,它还可以控制PLL(锁相环),使FCLK=Mpll或者FCLK=输入时钟(外部晶振或者外部时钟)的分频。

FCLK作为芯片核心ARM920T模块的时钟。

HCLK也可以为ARM920T提供时钟(当CAMERA时钟分频寄存器的DVS_EN位为1时,HCLK作为ARM核心时钟),HCLK也为内存控制器、中断控制器、LCD控制器、DMA和USB HOST模块提供时钟。

PCLK为WDT、IIS、IIC、PWM定时器、MMC接口、ADC、UART、GPIO、RTC和SPI提供时钟。

FCLK、HCLK和PCLK之间的关系由时钟分频控制寄存器CLKDIVN(包括HDIVN和PDIVN两个部分)来决定。

图中的USBCNTL模块主要是为USB host接口和USB设备接口提供正常工作需要的48MHz时钟,UCLK主要有4个状态:

1)刚刚复位时,UCLK为外部晶振或外部时钟。

2)配置UPLL结束后,在UPLL稳定时间内,UCLK为低电平,UPLL稳定时间结束,UCLK为48MHz。

3)CLKSLOW寄存器关闭UPLL,UCLK为外部晶振或者外部时钟。

4)CLKSLOW寄存器打开UPLL,UCLK为48MHz。 图中的POWERCNTL模块主要实现功耗控制的功能,此处不作详细解释。 PLL稳定时间由稳定时间寄存器LOCKTIME来控制,此寄存器一般设为0xFFFFFFFF。

http://home.eeworld.com.cn/my/space.php?uid=143675&do=blog&id=25098

- 电源管理:

时钟控制逻辑单元可以在不使用PLL情况下降低时钟 CLOCK的频率,并且可以通过软件来驱使时钟和各个模块的连接/断开,以减少电源消耗。 对于电源控制逻辑单元,2440有许多钟电源管理方案来针对所给的任务保持最优的电源消耗。

S3c2440中的电源管理模块对应 4种模式:NORMAL 模式、 SLOW 模式, IDLE 模式, SLEEP模式。

NORMAL 模式:这个模块给 CPU时钟以及 2440相应的外围设备提供时钟。这个模式下,当所有的外围设备都被打开,电源消耗被最大化。它允许用户通过软件来控制外部设备的操作。例如,如果一个定时器不需要时,那么用户可以通过 CLKCON寄存器来关闭时钟和定时器的连接,来降低电源消耗。 SLOW 模式:NON-PLL 模式,不同于 Normal模式,这个模式使用的一个外部时钟(XTlpll或 EXTCLK)来直接作为 2440的主频 FCLK,而没有使用 PLL。在这个模式下,电源的消耗仅依赖于外部时钟频率,电源同 PLL有关的消耗可以被排除。 IDLE 模式:这个模式下 CPU 的时钟 FCLK被断开,而还继续提供其他外围设备的时钟。因此空闲模式导致减少了 CPU核相应的电源消耗。任何中断请求都能够将 CPU唤醒。 Sleep 模式:这个模式断开了内部电源。因此在这个模式下CPU&内部的逻辑单元都没有电源消耗, 除了一个 wake-up逻辑单元。激活 sleep模式需要 2个独立的电源。一个给 wake-up逻辑模块提供电源,另外一个给内部逻辑包括 CPU提供电源,并且其是对于 poweron/off可控的。在 Sleep模式,提供给内部逻辑&CPU的电源模块将被关闭,而从 Sleep模式唤醒可以通过 EINT[15:0]&RTC中断来引发。

==== datasheet实战 ====

2440时钟:

- 时钟框架

The Clock & Power management block consists of three parts:

Clock control,

USB control,

Power control.

The Clock control logic in S3C2440A can generate the required clock signals including

FCLK for CPU,

HCLK for the AHB bus peripherals,

PCLK for the APB bus peripherals.

The S3C2440A has two Phase Locked Loops (PLLs):

one for FCLK, HCLK, and PCLK,

the other dedicated for USB block (48Mhz).

- 时钟分频:

FCLK is used by ARM920T.

HCLK is used for AHB bus, which is used by the ARM920T, the memory controller, the interrupt controller, the LCD controller, the DMA and USB host block.

PCLK is used for APB bus, which is used by the peripherals such as WDT, IIS, I2C, PWM timer, MMC interface, ADC, UART, GPIO, RTC and SPI.

- 电源管理:

The clock control logic can make slow clocks without PLL and connect/disconnect the clock to each peripheral block by software, which will reduce the power consumption.

For the power control logic, the S3C2440A has various power management schemes to keep optimal power consumption for a given task. The power management block in the S3C2440A can activate four modes:

NORMAL mode,

SLOW mode,

IDLE mode,

SLEEP mode.

NORMAL mode: The block supplies clocks to CPU as well as all peripherals in the S3C2440A. In this mode, the power consumption will be maximized when all peripherals are turned on. It allows the user to control the operation of peripherals by software. For example, if a timer is not needed, the user can disconnect the clock(CLKCON register) to the timer to reduce power consumption.

SLOW mode: Non-PLL mode. Unlike the Normal mode, the Slow mode uses an external clock (XTIpllor EXTCLK) directly as FCLK in the S3C2440A without PLL.In this mode, the power consumption depends on the frequency of the external clock only. The power consumption due to PLL is excluded.

IDLE mode: The block disconnects clocks (FCLK) only to the CPU core while it supplies clocks to all other peripherals. The IDLE mode results in reduced power consumption due to CPU core. Any interrupt request to CPU can be woken up from the Idle mode.

SLEEP mode: The block disconnects the internal power. So, there occurs no power consumption due to CPU and the internal logic except the wake-up logicin this mode.

Activating the SLEEP mode requires two independent power sources.

One of the two power sources supplies the power for the wake-up logic. The other one supplies other internal logics including CPU, and should be controlled for power on/off. In the SLEEP mode, the second power supply source for the CPU and internal logics will be turned off. The wakeup from SLEEP mode can be issued by the EINT[15:0] or by RTCalarm interrupt.

通过对设备频率的控制和一些引脚置为低电平以达到节能环保,呵呵~以上关于电源管理是一大块,需要另说。

再看下6410:

6410现在看来是arm入门级开发板,datasheet页数已上千,45个部分,与几年前的入门级2440相比复杂了许多。不过,读datasheet需要费脑么?谈不上智商比拼,更多是时间的消耗。

The System Controller consists of two parts:System Clock Control and System Power-management Control.

The System Clock Control logic in S3C6410X generates the required system clock signals,

ARMCLK for CPU,

HCLK for AXI/AHB-bus peripherals,

PCLK for the APB bus peripherals.

There are three PLLsin S3C6410X.

One is for ARMCLK only.

Second is for HCLK and PCLK.

The third thing is for peripheral, especially for audio related clocks.

The clock control logic generates slow-rate clock-signals for ARMCLK, HCLK and PCLK by bypassing externally supplied clock sources.

The clock signal to each peripheral block can be enabled or disabled by software control to reduce the power consumption.

FEATURES

The System Controller includes the following features:

• Three PLLs: ARM PLL, main PLL, extra PLL(for the modules those use special frequency)

• Five power-saving mode: NORMAL, IDLE, STOP, DEEP-STOP, and SLEEP

• Six controllable power domain: domain-G, domain-V, domain-I, domain-P, domain-F, domain-S

• Control operating clock

• Control bus priority

6410的特点看来主要体现在电源管理,将设备按模块分类(IP)。

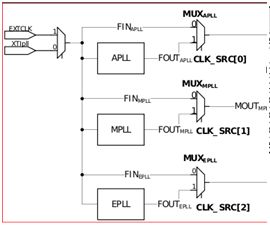

The clock source selects between an external crystal(XXTIpll) and external clock (XEXTCLK).

The clock generator consists of three PLLs (Phase Locked Loop) which generate high frequency clock signals up to 1.6GHz //677时是1.33G

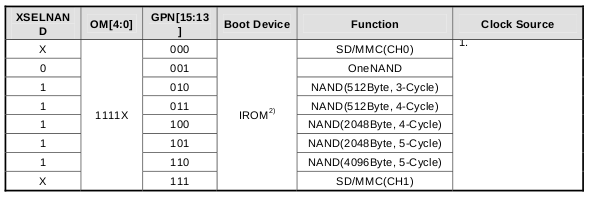

The OM[4:0]pins determines the operating modeof S3C6410X when the external reset signal is asserted. As described in the table, the OM[0] selects the external clock source, i.e., if the OM[0] is 0, the XXTIpll (external crystal) is selected. Otherwise, XEXTCLK is selected.

6410支持SD启动。

The operating mode is mainly classified into six categories according to the boot device. The boot device can be among SROM, NOR, OneNAND, MODEM and Internal ROM.

When NAND Flash device is used, XSELNAND pin must be 1, even if it is used as boot device or storage device.

When OneNAND Flash device is used, XSELNAND must be 0, even if it is used as boot device or storage device.

When NAND/OneNAND device is not used, XSELNAND can be 0 or 1.

- 时钟源(SLK_SRC)

The lowest three bits of CLK_SRC register control the source clocks of three groups. When the bit has 0, then the input clock is bypassed to the group. Otherwise, the PLL output will be applied to the group.

- 分频

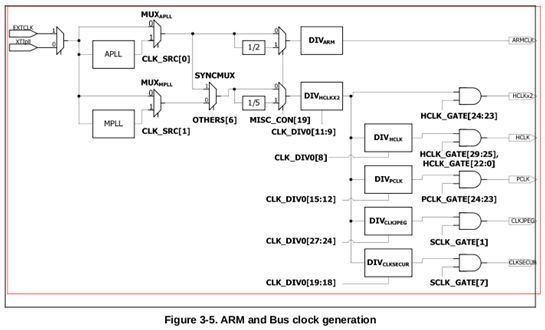

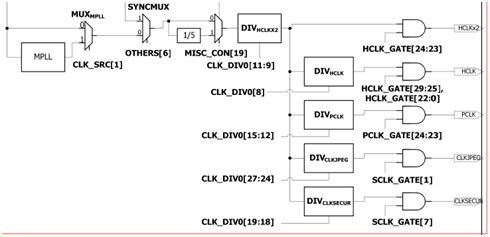

一个一目了然的图,涉及这么几个寄存器:

CLK_DIV0, HCLK_GATE, SCLK_GATE, PCLK_GATE...

ARM1176 processor of S3C6410X runs up to maximum 667MHz. The operating frequency can be controlled by the internal clock divider, DIVARM, without changing PLL frequency. The divider ratio varies from 1 to 16. ARM processor decreases the operating speed to reduce power dissipation.

When they are attached to AXI bus or AHB bus, the operating speed can be up to maximum 133MHz.

While they are attached to APB bus, the maximum operating speed can be up to 66MHz.

HCLKX2 clocks are supplied to two DDR controllers, DDR0 and DDR1, of S3C6410X. The operating speed can be up to maximum 266MHz to send and to receive data through DDR controllers. Each HCLKX2 clock can be masked independently to reduce redundant power dissipation on clock distribution network when the operation is not required.

All AHB bus clocks are generated from DIVHCLK clock divider. The generated clocks can be masked

independently to reduce redundant power dissipation. HCLK_GATE register controls the mask operation of HCLKX2 and HCLK.

Low-speed interconnection IPs transfer data through APB bus system. APB clocks of them are running at up to 66MHz as described in the above section and generated from DIVPCLK clock divider. They are also masked using PCLK_GATE register. As described, the frequency ratio between AHB clock and

一般使用的频率:

As illustrated in the above figures, HCLK_GATE, PCLK_GATE, and SCLK_GATE control the clock operation. If a bit is set, the corresponding clock will be supplied through each clock divider. Otherwise, it will be masked.

HCLK_GATE controls HCLK for each IPs. The AHB interface logic of each IP is masked independently to reduce dynamic power consumption.

PCLK_GATE controls PCLK for each IPs. Certain IPs requires special clocks to operate correctly. The clocks are controlled by SCLK_GATE.

提升到667M看来不是改几个数字那么简单:

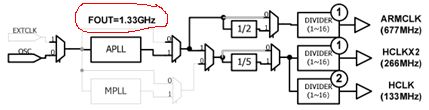

SYNCHRONOUS 667MHZ OPERATING MODE

The clock ratio between ARMCLK and HCLK must be integerto use synchronous interface between ARM core and AXI bus interface.

S3C6410X does not have any limitation up to 533MHz synchronous interface, i.e.,

ARMCLK = 533MHz, HCLKX2= 266MHz, HCLK = 133MHz.

However, there is some constraints over 533MHz, typically 667MHz interface.

The supported clock ratio is only 1:2.5:5 (ARMCLK = 667MHz, HCLKX2=266MHz, HCLK = 133MHz).

S3C6410X can be use synchronous 667MHz operating mode through the following 5 steps.

1. STEP1-Normal operating mode: SYNC667 field is cleared and there is no limitation for clock dividers. Typical clock divider ratio will be 1:2:4. (ARMCLK = 533MHz, HCLKX2 = 266MHz, HCLK = 133MHz)

2. STEP2-OSC mode: before set SYNC_667MHZ field, the operating clock of S3C6410X must be external oscillator. (set APLL_SEL of CLK_SRC as ‘0’) Clock divider ratio is unchanged, but the operating frequencies are 12MHz, 6MHz, and 3MHz.

3. STEP3-DIV112 mode: in this step, clock divider ratio must be set as 1:1:2 from 1:2:4.

4. STEP4-SYNC667 low frequency mode: set SYNC_667MHZ field. Now, overall clock divider ratio will be 2:5:10. If input oscillator is 12MHz, then ARMCLK, HCLKX2, and HCLK will be 6MHz, 2.4MHz, and 1.2MHz (2:5:10), respectively.

5. STEP5-SYNC667 mode: if FOUT of APLL is 1.33GHz, then the output will be 667MHz, 266MHz, and 133MHz. S3C6410X runs at 667MHz synchronous interface mode.

When exiting from SYNC667 mode, the sequence is reverse order (from STEP5 to STEP1).

Limitation of synchronous 667MHz operating mode

There are some limitations as follows when S3C6410X runs at SYNC667 mode.

• Cannot use other clock divider ratio at SYNC667 mode. The fields, ARM_RATIO, HCLKX2_RATIO, and HCLK_RATIOof CLK_DIV0 must be 0x0, 0x0, and 0x1, respectively.

• Use asynchronous interface mode at SYNC667 mode if ARM_RATIO, HCLKX2_RATIO, and HCLK_RATIO of CLK_DIV0 are different values from 0x0, 0x0, and 0x1.

• Cannot use DVFS(Dynamic Voltage Frequency Scale) at synchronous interface mode. As described the above, SYNC667 mode does not support dynamic clock ratio change.Interface mode must be asynchronous interface mode before changing clock divider ratio. 异步状态才能改ratio

• Cannot enter into STOP/D-STOP/SLEEP mode. The SYNC667 mode must be cleared before entering into STOP/D-STOP/SLEEP mode.

实例,时钟配置 ==>

/* LOCK_TIME,一般保持默认值0xffff即可,宁可大,不宜小*/ ldr r0, =ELFIN_CLOCK_POWER_BASE @0x7e00f000 ldr r1, =#0x0000ffff str r1, [r0, #APLL_LOCK_OFFSET] /* APLL_LOCK */ str r1, [r0, #MPLL_LOCK_OFFSET] /* MPLL_LOCK */ str r1, [r0, #EPLL_LOCK_OFFSET] /* EPLL_LOCK */ @ set async mode /* 当CPU时钟!= HCLK时,设为异步模式*/ ldr r1, [r0, #OTHERS_OFFSET] @0x7e00f900 bic r1, r1, #0xC0 str r1, [r0, #OTHERS_OFFSET] wait_for_async: /* 等待,直到CPU进入异步模式*/ ldr r1, [r0, #OTHERS_OFFSET] and r1, r1, #0xf00 cmp r1, #0x0bne wait_for_async

- 配置APLL:

/* 配置APLL */ #define APLL_CON_VAL ((1<<31) | (266 << 16) | (3 << 8) | (1)) ldr r0, =0x7E00F00C @APLL_CON ldr r1, =APLL_CON_VAL str r1, [r0] /* APLL_CON, FOUTAPLL= MDIV * Fin / (PDIV*2^SDIV) = 266*12/(3*2^1) = 532MHz */

根据datasheet的配置推荐,以下是u-boot的几种配置方案:include/configs/mini6410.h

#define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv) #if defined(CONFIG_CLK_666_133_66) /* FIN 12MHz, Fout 666MHz */ #define APLL_MDIV 333 #define APLL_PDIV 3 #define APLL_SDIV 1 #undef CONFIG_SYNC_MODE /* ASYNC MODE */ #elif defined(CONFIG_CLK_532_133_66) /* FIN 12MHz, Fout 532MHz */ #define APLL_MDIV 266 #define APLL_PDIV 3 #define APLL_SDIV 1 #define CONFIG_SYNC_MODE #elif defined(CONFIG_CLK_400_133_66) || defined(CONFIG_CLK_800_133_66) /* FIN 12MHz, Fout 800MHz */ #define APLL_MDIV 400 #define APLL_PDIV 3 #define APLL_SDIV 1 #define CONFIG_SYNC_MODE #elif defined(CONFIG_CLK_400_100_50) /* FIN 12MHz, Fout 400MHz */ #define APLL_MDIV 400 #define APLL_PDIV 3 #define APLL_SDIV 2 #define CONFIG_SYNC_MODE #elif defined(CONFIG_CLK_OTHERS) /*If you have to use another value, please define pll value here*/ /* FIN 12MHz, Fout 532MHz */ #define APLL_MDIV 266 #define APLL_PDIV 3 #define APLL_SDIV 1 #define CONFIG_SYNC_MODE

- 配置MPLL:

/* 配置MPLL */ #define MPLL_CON_VAL ((1<<31) | (266 << 16) | (3 << 8) | (1)) ldr r0, =0x7E00F010 ldr r1, =MPLL_CON_VAL str r1, [r0] /* MPLL_CON, FOUTMPLL = MDIV * Fin / (PDIV*2^SDIV) = 266*12/(3*2^1) = 532MHz */

- 时钟源

/* 选择PLL的输出作为时钟源*/ ldr r0, =0x7E00F01C ldr r1, =0x03 str r1, [r0]

- 分频

/*Set Clock Divider*/ #define ARM_RATIO 0 /* ARMCLK = DOUTAPLL / (ARM_RATIO + 1) */ #define HCLKX2_RATIO 1 /* HCLKX2 = HCLKX2IN / (HCLKX2_RATIO + 1) */ #define HCLK_RATIO 1 /* HCLK = HCLKX2 / (HCLK_RATIO + 1) */ #define PCLK_RATIO 3 /* PCLK = HCLKX2 / (PCLK_RATIO + 1) */ #define MPLL_RATIO 0 /* DOUTMPLL = MOUTMPLL / (MPLL_RATIO + 1) */ ldr r0, =0x7E00F020 /* CLK_DIV0 */ ldr r1, =(ARM_RATIO) | (MPLL_RATIO << 4) | (HCLK_RATIO << 8) | (HCLKX2_RATIO << 9) | (PCLK_RATIO << 12) str r1, [r0] mov pc, lr

NOTE:

/* CLKUART(=66.5Mhz) = CLKUART_input(532/2=266Mhz) / (UART_RATIO(3)+1) */

/* CLKUART(=50Mhz) = CLKUART_input(400/2=200Mhz) / (UART_RATIO(3)+1) */

/* Now, When you use UART CLK SRC by EXT_UCLK1, We support 532MHz & 400MHz value */

这处注解说明,改变时钟频率会影响到串口。

说到最后,发觉这张图对时钟配置与寄存器的关系表述的尤其明了。