FPGA时钟域处理

FPGA时钟域处理

文章目录

- FPGA时钟域处理

- 前言

- 一、时钟域的管理

-

- 1 时钟资源

- 二、跨时钟域设计

-

- 1.1 单bit信号跨时钟域

-

- 1.1.1 慢到快

- 1.1.2 快到慢

- 1.1.3 慢到快

- 1.2 多bit(这里指简单的多个控制信号)

- 三、时钟域区域划分

- 四 使用衍生时钟的注意事项

-

- 4.1 原则1

- 4.2原则2

- 4.3 原则3

- 总结

前言

FPGA在代码设计的时候要考虑不同功能会有不同的时钟域,在设计构思的时候就要考虑到框图中的时钟域划分。一般都是多时钟域设计

一、时钟域的管理

一般外部时钟从FPGA的专用时钟引脚引入后都会做PLL处理。

- 方便静态时序分析

- 会自动生成衍生时钟约束

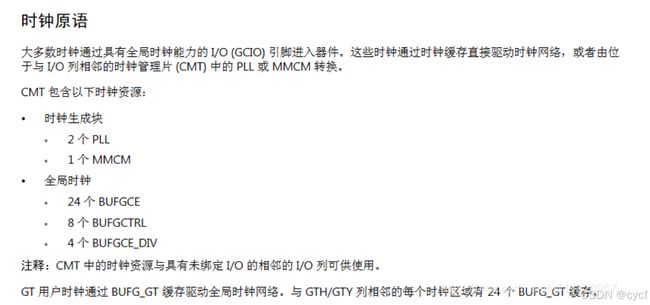

1 时钟资源

包含以下资源:

时钟生成块:可以用这个来生成不同的时钟。

全局时钟(使用的时候用原语):用这个来将外部输入的时钟进行原语处理,时钟缓存来驱动全局时钟网络。全局时钟(BUFG)和区域时钟(BUFR)的区别 : 全局可以对所有IO口提供驱动时钟,区域只能对一片区域提共时钟。

如果需要一个时钟信号被广泛分配到FPGA内多个地方,BUFG是最佳选择,因为它能够最小化时钟偏斜并保持时钟信号的稳定。而当设计可以局部化到FPGA的特定区域,且该区域需要独立的时钟信号时,BUFR或BUFH(另一种区域时钟缓冲器)是合适的选择。BUFR特别适用于需要在较宽区域内但不是全芯片范围内分配时钟的情况,尤其是当需要对时钟信号进行分频时。BUFR非常适合需要时钟域交叉或串并转换的源同步应用,并且相比BUFG,BUFR在skew和功耗方面更小,这在源同步设计中非常关键

以下说明PLL和MMCM的区别:

时钟使用的选择:

PLL和MMCM的区别:MMCM精确的相位可调;但是PLL使用面积小

(后期再专门出一期怎么使用)

二、跨时钟域设计

1.1 单bit信号跨时钟域

1.1.1 慢到快

如果存在异步可能会导致采样数据出错。打两拍处理。

需要注意:

- 发送端和第一拍之间不能有组合逻辑:因为组合逻辑是毛刺产生的关键,如果产生毛刺会直接传递给同步器。

- 同步器中的寄存器之间(除了第二拍的寄存器输出)只能有一个扇出。(只要同步器之间处于相同时钟域,那么两者之间是可以有组合逻辑的,这里要区别与发送和接受之间,同步器内寄存器之间)

延迟打拍法:

module delay_clap(

input clk1, //异步慢时钟

input sig1, //异步信号

input rstn, //复位信号

input clk2, //目的快时钟域市政

output sig2); //快时钟域同步后的信号

reg [2:0] sig2_r ; //3级缓存,前两级用于同步,后两节用于边沿检测

always @(posedge clk2 or negedge rstn) begin

if (!rstn) sig2_r <= 3'b0 ;

else sig2_r <= {sig2_r[1:0], sig1} ; //缓存

end

assign sig2 = sig2_r[1] && !sig2_r[2] ; //上升沿检测

延迟采样法

即当有使能信号(使能信号一直为高或者没有使能信号),可以采用检测使能信号的上升沿,当检测到了,再去采集数据,并将使能信号和数据进行时钟对齐。(这里为什么要用单bit的使能信号,因为多bit同步可能会出现时序不对齐的问题。)

//同步模块工作时钟为 100MHz 的模块

//异步数据对来自工作时钟为 20MHz 的模块

module delay_sample(

input rstn,

input clk1,

input [31:0] din,

input din_en,

input clk2,

output [31:0] dout,

output dout_en);

//sync din_en

reg [2:0] din_en_r ;

always @(posedge clk2 or negedge rstn) begin

if (!rstn) din_en_r <= 3'b0 ;

else din_en_r <= {din_en_r[1:0], din_en} ;

end

wire din_en_pos = din_en_r[1] && !din_en_r[2] ;

//sync data

reg [31:0] dout_r ;

reg dout_en_r ;

always @(posedge clk2 or negedge rstn) begin

if (!rstn)

dout_r <= 'b0 ;

else if (din_en_pos)

dout_r <= din ;

end

//dout_en delay

always @(posedge clk2 or negedge rstn) begin

if (!rstn) dout_en_r <= 1'b0 ;

else dout_en_r <= din_en_pos ;

end

assign dout = dout_r ;

assign dout_en = dout_en_r ;

endmodule

如果没有使能信号或者使能一直为1,那么就用计数器的方式去采集中间时刻的数据。方法就是边沿检测clk1,然后计数器计数,知道中间时刻,然后采集数据

//同步模块工作时钟为 100MHz 的模块

//异步数据对来自工作时钟为 999KHz 的模块

module delay_cnt_sample(

input rstn,

input clk1,

input [31:0] din,

input din_en,

input clk2,

output [31:0] dout,

output dout_en);

//4级缓存:3级用于打拍同步,一级用于边沿检测

reg [3:0] edge_r ;

always @(posedge clk2 or negedge rstn) begin

if (!rstn) edge_r <= 3'b0 ;

else edge_r <= {edge_r[3:0], clk1} ;

end

wire edge_pos = edge_r[2] && !edge_r[3] ;

//延迟计数器,检测到慢时钟上升沿时开始计数

reg [5:0] cnt ;

always @(posedge clk2 or negedge rstn) begin

if (!rstn) cnt <= 6'h3f ;

else if (edge_pos && din_en)

cnt <= 6'h0 ;

else if (cnt != 6'h3f) cnt <= cnt + 1'b1 ;

end

//数据同步

reg [31:0] dout_r ;

reg dout_en_r ;

always @(posedge clk2 or negedge rstn) begin

if (!rstn)

dout_r <= 'b0 ;

else if (din_en && cnt == 47) //大约在慢时钟周期中间时刻采样

dout_r <= din ;

end

//数据使能信号较数据采样时刻延迟一个周期输出

always @(posedge clk2 or negedge rstn) begin

if (!rstn) dout_en_r <= 1'b0 ;

else if (din_en && cnt==48)

dout_en_r <= 1'b1 ;

else dout_en_r <= 1'b0 ;

end

assign dout = dout_r ;

assign dout_en = dout_en_r ;

endmodule

1.1.2 快到慢

信号展宽1.5倍或者两倍以上。如果是快速变化的单bit,则会有问题

1.1.3 慢到快

边沿检测

1.2 多bit(这里指简单的多个控制信号)

多bit 融合:

分为两种多比特融合:

同步有效:则多比特融合成1bit,再用1bit来跨时钟域

有流水:先多比特融合,再根据时序来调整同步后的输出(如加一个寄存器缓存输出)

多周期路径:

再发送数据的时候,配上一个同步的控制信号,数据和控制信号同时发送,同步控制信号再经过同步器同步之后,使用这个控制信号来加载数据。

FIFO

三、时钟域区域划分

最好的是一个模块中只有一个时钟域,模块之间用同步器隔离开。那么只需要在外部去设定伪路径,这样就很简单了。

四 使用衍生时钟的注意事项

在使用衍生时钟或者对衍生时钟进行处理的时候需要注意以下几点。

4.1 原则1

不要使用行波和门控时钟,要使用时钟使能或PLL

时钟使能的n分频,使能还是有原始时钟来驱动。PLL的输出是由限制的,如果使用时钟使能,将随意分频,因为其本身还是有原始时钟驱动,所以不会有任何其他毛病。

4.2原则2

跨时钟域都设置为伪路径

4.3 原则3

使用使用控制模块(函数)来进行时钟管理,不要使用组合逻辑。

因为组合逻辑容易产生毛刺。如果要进行时钟管理,使用的组合逻辑超过一个LUT,那么就可能产生毛刺。

但是,只使用一个LUT进行时钟操作,比如只对衍射时钟进行一个反转,就可以用一个LUT实现,就不会有毛刺

此外,对于使用一个LUT的情况,也需要注意,如果这个LUT是多输入的,如果两个都在变,也会有毛刺,那么需要将其中一个输入保持不变。

总结

总体起来说需要考虑两个方面的知识点,时钟资源有哪些,跨时钟域的处理。另外就是需要考虑对时钟本身的处理需要考虑的处理技巧,如分频,时钟的反转或者倍频调整(尽量还是用pll吧)