【原】DM9000X以太网控制器操作原理

DM9000X以太网控制器操作原理

我第一次接触DM9000A以太网控制器是在今年十月份,当初想在ATMEL的AT91SAM9G20开发板上移植网卡的驱动程序。该板子有自带Code,所以我就从原理开始,一点一点啃开发板的硬件接口。也在网上搜罗了很多资料,现在把对自己理解有帮助的一些内容发出来,后面倘若有新的理解,也会随后加之。

DM9000AEP硬件特点

DM9000A具有一个通用的微处理器接口,内部集成了16kB SRAM(其中13kB用作接收缓冲区,3kB作为发送缓冲区),对内部存储器访问支持8位和16位数据接口以适用于不同的微处理器;内部集成了一个 10/100M自适应PHY,可以连接到3类、4类、5类的10M无屏蔽双绞线和5类的100M无屏蔽双绞线。

DM9000和DM9000A,两者的驱动程序我没具体区分过,但网友所说其驱动相同我也没什么异议,至少现在是这样。不过在硬件引脚数量上,两者稍微有些区别。D9000是100Pin的,而DM9000A是48Pin;从总线位宽上,DM9000A支持byte/word IO 操作, DM9000支持byte/word/dword IO 操作;GPIO Pin,DM9000A 没有,DM9000 有4个 GPIO Pin。48引脚的DM9000A,同微处理器衔接设计网络接口时,有利于缩小PCB面积,节约板上空间资源。

DM9000A软件编程特点

基本的读写操作

要清楚DM9000A的编程特点,需要先看看DM9000A和AT91SAM9G20之间的接口连接,我觉得从实际例子出发对于了解理论上的功能要有帮助的多。

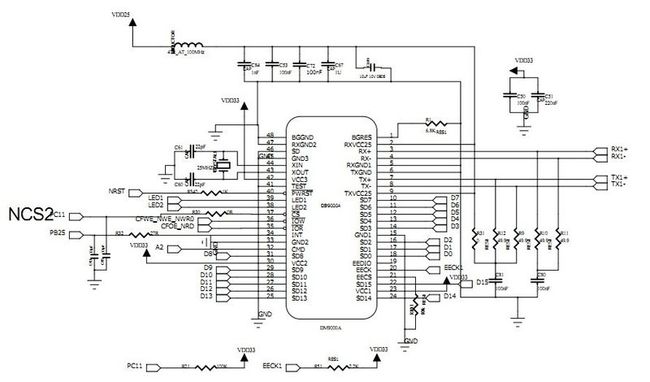

9G20的DM9000A 与CPU的管脚连接示意图

DM9000A的读信号线IOR、写信号线IOW分别与AT91SAM9G20的读信号线RD、写信号线WR相连;片选信号CS与处理器的Bank2片选信号NCS2相连,因此网络控制器的端口地址IOAddr为0x20000000。读写信号与片选信号都是保持默认设置的低电平有效。

在DM9000A中只有INDEX端口与DATA端口两个寄存器可以直接被CPU直接访问,其它所有内部控制和状态寄存器都是通过这两个端口寄存器间接访问的。网络控制器CMD引脚决定了处理器访问的是哪个端口寄存器:当CMD=0时,主机访问的是INDEX端口寄存器;当CMD=1时,访问的是DATA端口寄存器。设计中将CMD引脚与处理器的地址线A2相连,则DM9000A的2个外部接口端口地址分别为:

1 INDEX端口地址 = IOAddr + 0x00 2 DATA端口地址 = IOAddr + 0x04 3 0x04是因为DM9000A的CMD引脚连在了AT91SAM9G20的A2地址线上,这样既可以选择访问不同的端口,同时也能将端口数据写在两块不同的存储空间

实际中INDEX端口寄存器保存的是访问DATA端口寄存器的内部寄存器的地址,因此对DM9000A控制或状态寄存器访问的命令顺序是:

A:从INDEX端口写入要访问的内部寄存器地址

B:从DATA端口读出/写入Value

那么到底是读内部寄存器还是写内部寄存器,就看程序中有没有读总线或者写总线的操作,这里是由总线控制器自动判断读写命令。

如果程序中使用“读”命令(一般是一个return(*DATA)),这样一条指令,那么总线控制器会自动将RD引脚置低电平,从而告知DM9000A,现在需要读INDEX标识的寄存器的内容,取出值后将其写入DATA指向的内存空间;如果程序中使用“写”命令(一般是一条赋值语句 *DATA=0xXXXX),同样,总线控制器会将WR引脚置低电平,告知DM9000A,现在要向INDEX标识的寄存器里写入DATA空间的内容。这样就完成了一个读写周期。

读写缓冲区的分配

前面说过,DM9000A内部集成了16kBSRAM,低3kB作为发送缓冲区,高13kB用作接收缓冲区。写发送包存储区的时候,如果存储器地址越界,则将IMR高7位置位,SRAM的读写指针自动跳回0地址;读接收存储器的时候,读指针发生越界,则自动跳回接收缓冲的起始地址0x0C00(低3KB的结束,高13KB的开始)。

初始化过程

初始化过程相对较简单:启动内部PHY,配置网卡工作模式,设置网卡MAC地址,启用收发缓冲指针返回功能,清除数据发送中断,使能数据收发中断,最后使能数据自动接收功能。

数据包接收

数据包发送