串行通信技术SERDES

串行通信技术SERDES

随着对信息流量需求的不断增长,传统并行接口技术成为进一步提高数据传输速率的瓶颈。过去主要用于光纤通信的串行通信技术——SERDES正在取代传统并行总线而成为高速接口技术的主流。本文阐述了介绍SERDES收发机的组成和设计,并展望了这种高速串行通信技术的广阔应用前景。

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。它是一种时分多路复用(TDM)、点对点的通信技术,即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,从而大大降低通信成本。

SERDES技术最早应用于广域网(WAN)通信。国际上存在两种广域网标准:一种是SONET,主要通行于北美;另一种是SDH,主要通行于欧洲。这两种广域网标准制订了不同层次的传输速率。目前万兆(OC-192)广域网已在欧美开始实行,中国大陆已升级到2.5千兆(OC-48)水平。SERDES技术支持的广域网构成了国际互联网络的骨干网。

SERDES技术同样应用于局域网(LAN)通信。因为SERDES技术主要用来实现ISO模型的物理层,SERDES通常被称之为物理层(PHY)器件。以太网是世界上最流行的局域网,其数据传输速率不断演变。IEEE在2002年通过的万兆以太网标准,把局域网传输速率提高到了广域网的水平,并特意制订了提供局域网和广域网无缝联接的串行WAN PHY。与此同时,SERDES技术也广泛应用于不断升级的存储区域网(SAN),例如光纤信道。

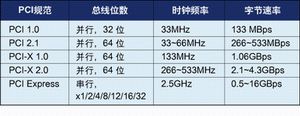

随着半导体技术的迅速发展,计算机的性能和应用取得了长足进步。可是,传统并行总线技术——PCI却跟不上处理器和存储器的进步而成为提高数据传输速率的瓶颈。新一代PCI标准PCI Express正是为解决计算机IO瓶颈而提出的(见表1)。PCI Express是一种基于SERDES的串行双向通信技术,数据传输速率为2.5G/通道,可多达32通道,支持芯片与芯片和背板与背板之间的通信。国际互联网络和信息技术的兴起促成了计算机和通信技术的交汇,而SERDES串行通信技术逐步取代传统并行总线正是这一交汇的具体体现。

SERDES系统的组成和设计

基于SERDES的高速串行接口采用以下措施突破了传统并行I/O接口的数据传输瓶颈:一是采用差分信号传输代替单端信号传输,从而增强了抗噪声、抗干扰能力;二是采用时钟和数据恢复技术代替同时传输数据和时钟,从而解决了限制数据传输速率的信号时钟偏移问题。

<!--[if gte vml 1]><v:shapetype id="_x0000_t75" coordsize="21600,21600" o:spt="75" o:preferrelative="t" path="m@4@5l@4@11@9@11@9@5xe" filled="f" stroked="f"> <v:stroke joinstyle="miter" /> <v:formulas> <v:f eqn="if lineDrawn pixelLineWidth 0" /> <v:f eqn="sum @0 1 0" /> <v:f eqn="sum 0 0 @1" /> <v:f eqn="prod @2 1 2" /> <v:f eqn="prod @3 21600 pixelWidth" /> <v:f eqn="prod @3 21600 pixelHeight" /> <v:f eqn="sum @0 0 1" /> <v:f eqn="prod @6 1 2" /> <v:f eqn="prod @7 21600 pixelWidth" /> <v:f eqn="sum @8 21600 0" /> <v:f eqn="prod @7 21600 pixelHeight" /> <v:f eqn="sum @10 21600 0" /> </v:formulas> <v:path o:extrusionok="f" gradientshapeok="t" o:connecttype="rect" /> <o:lock v:ext="edit" aspectratio="t" /> </v:shapetype><v:shape id="_x0000_i1025" type="#_x0000_t75" alt="图1: SERDES收发机的组成模块。" style='width:225pt;height:117pt'> <v:imagedata src="file:///C:\DOCUME~1\ADMINI~1\LOCALS~1\Temp\msohtml1\01\clip_image001.gif" mce_src="file:///C:\DOCUME~1\ADMINI~1\LOCALS~1\Temp\msohtml1\01\clip_image001.gif" o:href="http://www.cndzz.com/tech/Article/UploadFiles/200604/20064804721882.GIF" /> </v:shape><![endif]-->

一个典型SERDES收发机由发送通道和接收通道组成(见图1):编码器、串行器、发送器以及时钟产生电路组成发送通道;解码器、解串器、接收器以及时钟恢复电路组成接收通道。顾名思义,编码器和解码器完成编码和解码功能,其中8B/10B、64B/66B和不规则编码(scrambling)是最常用的编码方案。串行器和解串器负责从并行到串行和从串行到并行的转换。串行器需要时钟产生电路,时钟发生电路通常由锁相环(PLL)来实现。解串器需要时钟和数据恢复电路(CDR),时钟恢复电路通常也由锁相环来实现,但有多种实现形式如相位插植、过剩抽样等。发送器和接收器完成差分信号的发送和接收,其中LVDS和CML是最常用的两种差分信号标准。另外还有一些辅助电路也是必不可少的,例如环路(loopback)测试、内置误码率测试等等。

通信标准制订了严格的性能指标以确保系统的可靠性和互用性。SERDES芯片的主要性能指标包括抖动产生、抖动容忍、抖动转移以及系统误码率(BER)等。抖动产生取决于时钟发生电路特别是压控振荡器(VCO)的相位噪声;抖动容忍取决于时钟恢复电路容忍抖动的能力,而抖动转移是在用作中继器时必须满足的指标,同时取决于时钟发生和时钟恢复电路的性能。系统误码率(通常要求低于10-12)由时钟抖动性能、发送器信号幅度、接收器灵敏度以及链路信道特性共同决定。对于普通FR4印刷电路板而言,趋肤效应和介质损耗导致的码间(intersymbol)干扰是限制背板传输速率和距离的最主要因素。因此,信号均衡甚至自适应均衡技术正在成为SERDES芯片的核心技术。信号均衡技术可以在发送端实现,称之为预加重(pre-emphasis),也可以在接收端实现,例如判决反馈均衡。目前采用先进的均衡技术可以实现40英寸(1米)距离的10G背板传输。

SERDES芯片的设计需要模拟和数字两方面即混合信号的设计经验。例如锁相环的设计,其中压控振荡器属于模拟电路,而检相器和分频器属于数字电路。SERDES芯片普遍采用低成本、低功耗的CMOS工艺,但CMOS工艺往往达不到高速混合信号的速度要求。因此设计人员必须采用特殊的高频宽带电路设计技术,例如螺旋电感可以用来提高电路速度和带宽。另外,模拟和数字电路共存于同一硅片上,容易产生电源同步噪声(SSN)和地反弹以及信号串扰。因此保持信号的完整性是混合信号设计人员面临的一项挑战。与此同时,芯片封装和印刷电路板的设计与仿真也是SERDES设计不可或缺的一环。当前SERDES设计逐渐IP(知识产权)化,即SERDES收发器作为商业化IP模块而嵌入到需要高速I/O接口的大规模集成电路中。

SERDES技术的应用

最早用于光纤通信的SERDES技术会继续在信息高速公路的建设中发挥主导作用。而计算机和通信的融合为SERDES技术开辟了更为广阔的应用前景。基于SERDES技术的高速串行接口正在成为一种通用的IO接口标准。近年来世界上有多个标准组织已经或正在制订从1G到10G的高速串行接口标准(见表2)。1~6G+SERDES产品为当前高速串行接口标准的主流,其中2.5G/3.125G为第一代产品,5G/6.25G为第二代产品。这些芯片采用0.18微米的CMOS工艺就可以实现。

信息高速公路主要由以光纤作为传输媒体的广域网(SONET)和局域网(以太网)组成。广域网和局域网分别向近距离和远距离渗透,在城域网(MAN)交汇。而且,在广域网上传输以太网数据包的协议(Ethernet over SONET)使得广域网和局域网的界限更为模糊。随着互联网络信息流量的增长,对信息存储容量的需求也大大增长。目前有三种常用的信息存储方式:直接连接存储(DAS)、网络连接存储(NAS)和专用存储区域网(SAN)。最简单的直接连接存储是通过小型计算机系统接口(SCSI)把磁盘驱动器直接连接到服务器上。网络连接存储是把存储设备连接到局域网而存储信息的传输需要通过局域网进行。SAN采用光纤信道技术,是连接服务器和存储设备的专用网络。

<!--[if gte vml 1]><v:shape id="_x0000_i1027" type="#_x0000_t75" alt="表2: 高速串行接口标准一览" style='width:262.5pt; height:236.25pt'> <v:imagedata src="file:///C:\DOCUME~1\ADMINI~1\LOCALS~1\Temp\msohtml1\01\clip_image003.gif" mce_src="file:///C:\DOCUME~1\ADMINI~1\LOCALS~1\Temp\msohtml1\01\clip_image003.gif" o:href="http://www.cndzz.com/tech/Article/UploadFiles/200604/20064804723686.GIF" /> </v:shape><![endif]-->

SERDES技术的应用从光纤通信发展到计算机通用I/O接口,其传输媒体也由光纤发展到铜线或背板。InfiniBand是一种采用电缆或背板作为传输媒体的高速串行接口,主要用于数据中心服务器和存储设备之间的通信。RapidIO是一种面向嵌入式系统的总线结构,有并行和串行两种规范,主要用于嵌入系统的处理器总线,局部I/O总线及背板。光互联论坛(OIF)制订了多种光纤通信芯片之间的接口标准,其中公共电气接口(CEI)把背板通信速率提高到6G和11G的水平。作为计算机接口技术从并行向串行的标志性转变,PCI Express将会取代PCI和PCI-X而成为外围设备(网络、存储和视频)的通用高速接口标准。在此转变过程中,提供向下兼容的 “桥接器件”会率先推向市场,随后是完全基于PCI Express的外围设备板卡。与此同时,PCI Express的应用也向通信领域拓展,基于PCI Express架构的“先进交换”就是面向通信而提出的。PCI工业计算机制造商协会(PICMG)正在制订一系列称之为先进电信计算架构(AdvancedTCA)的规范,包括对背板、电源、散热、机械和系统管理等方面的要求,旨在为下一代电信设备提供标准化的通用平台。

作者:王守军,Email: [email protected],Altera公司