head.s分析(5):关闭串口

快乐虾

http://blog.csdn.net/lights_joy/

本文适用于

ADI bf561 DSP

uclinux-2008r1.5-rc3 (移植到vdsp5)

Visual DSP++ 5.0(update 5)

欢迎转载,但请保留作者信息

/* Initialise UART - when booting from u-boot, the UART is not disabled

* so if we dont initalize here, our serial console gets hosed */

p0.h = hi(UART_LCR);

p0.l = lo(UART_LCR);

r0 = 0x0(Z);

w[p0] = r0.L; /* To enable DLL writes */

ssync;

p0.h = hi(UART_DLL);

p0.l = lo(UART_DLL);

r0 = 0x0(Z);

w[p0] = r0.L;

ssync;

p0.h = hi(UART_DLH);

p0.l = lo(UART_DLH);

r0 = 0x00(Z);

w[p0] = r0.L;

ssync;

p0.h = hi(UART_GCTL);

p0.l = lo(UART_GCTL);

r0 = 0x0(Z);

w[p0] = r0.L; /* To enable UART clock */

ssync;

这段代码用于关闭串串口,但是这里有个问题,在设置UART_DLL和UART_DLH时必须将UART_LCR的最高位设置为1,但是原始代码中却未设置,这样就造成了设置UART_DLL和UART_DLH必然失败。所以

r0 = 0x0(Z);

应该改为

r0 = 0x80(Z);

下面的说明来自于vdsp文档:

The UART_DLL register is mapped to the same address as the UART_THR and UART_RBR registers. The UART_DLH register is mapped to the same address as the Interrupt Enable register (UART_IER). The DLAB bit in UART_LCR must be set before the UART Divisor Latch registers can be accessed.

在将UART_DLH和UART_DLL置0后,它的Divisor将变成65536。

这一句

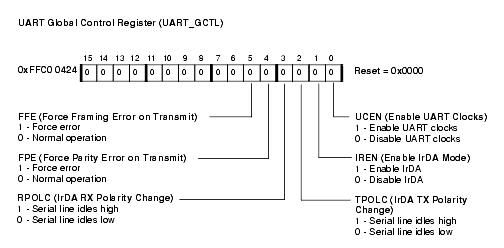

w[p0] = r0.L; /* To enable UART clock */

也相当奇怪,如果按照注释的说法是要启用UART clock,但是将UART_GCTL的值设置为0却明显是关闭clock。

1 参考资料

head.s分析(1):保存u-boot传递过来的指针(2009-1-19)

head.s分析(2):SYSCFG配置(2009-1-19)

head.s分析(3):数据及指针寄存器清0(2009-1-19)

head.s分析(4):关闭CACHE(2009-01-19)