Super Nintendo Entertainment System technical spec

The Super Nintendo Entertainment System technical specifications describe the various components of the Super Nintendo Entertainment System video game console.

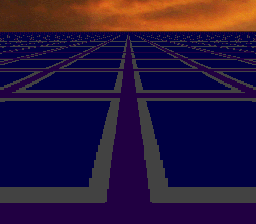

The design of the Super NES incorporates powerful graphics and sound co-processors that allowed tiling and Mode 7 effects, many times more colors, and audio quality that represented a leap over the competition.[1] Individual game cartridges can supply further custom chips as needed.

Contents

[hide]- 1 Central processing unit

- 2 Video

- 3 Audio

- 4 Onboard RAM

- 5 Notes

- 6 References

Central processing unit[edit]

| CPU reference | |

|---|---|

| Processor | Ricoh 5A22, based on a 16-bit 65c816 core |

| Clock rates(NTSC) | Input: 21.47727 MHz Bus: 3.58 MHz, 2.68 MHz, or 1.79 MHz |

| Clock rates(PAL) | Input: 21.28137 MHz Bus: 3.55 MHz, 2.66 MHz, or 1.77 MHz |

| Buses | 24-bit and 8-bit address buses, 8-bit data bus |

| Additional features |

|

The CPU is a Nintendo-custom 5A22 processor, based on a 16-bit 65c816 core. The CPU employs a variable bus speed depending on the memory region being accessed for each instruction cycle: the input clock is divided by 6, 8, or 12 to obtain the bus clock rate.[jargon]Non-access cycles, most register accesses, and some general accesses use the divisor of 6. WRAM accesses and other general accesses use the divisor of 8. Only the controller port serial-access registers use the divisor of 12.[2]

The chip has an 8-bit data bus, controlled by two address buses.[jargon] The 24-bit "Bus A" is used for general accesses, while the 8-bit "Bus B" is used for support chip registers (mainly the video and audio processors).[2] Normally only one bus is used at a time; however, the built-in direct memory access (DMA) unit places a read signal on one bus and a write signal on the other to achieve block transfer speeds of up to 2.68 MB/s.[a][3]

The DMA unit has 8 independent channels, each of which can be used in two modes. General DMA transfers up to 64 kB[b] in one shot, while H-blank DMA (HDMA) transfers 1–4 bytes at the end of each video scanline. HDMA is typically used to change video parameters to achieve effects such as perspective, split-screen, and non-rectangular windowing without tying up the main CPU.[3]

The 5A22 also contains an 8-bit parallel I/O port (which was mostly unused in the SNES); controller port interface circuits, including bothserial and parallel access to controller data; a 16-bit multiplication and division unit; and circuitry for generating non-maskable interrupts onV-blank and IRQ interrupts on calculated screen positions.[3]

Video[edit]

| Video reference | |

|---|---|

| Resolutions | Progressive: 256 × 224, 512 × 224, 256 × 239, 512 × 239 Interlaced: 512 × 448, 512 × 478 |

| Pixel depth | 2, 4, 7, or 8 bpp indexed; 8 or 11 bpp direct |

| Total colors | 32768 (15-bit) |

| Sprites | 128, 32 max per line; up to 64 × 64 pixels |

| Backgrounds | Up to 4 planes; each up to 1024 × 1024 pixels |

| Effects |

|

The picture processing unit (PPU) consists of two separate but closely tied IC packages, which may be considered as a single entity. It also contains 64 kB[b] of SRAM for storing video data (VRAM), 544 bytes of object attribute memory (OAM) for storing sprite data, and 256 × 15 bits of color generator RAM (CGRAM) for storing palette data. The PPU is clocked by the same signal as the CPU, and generates a pixel every two or four cycles. Both NTSC and PAL systems use the same PPU chips, with one pin per chip selecting NTSC or PAL operation.[3]

Images may be output at 256 or 512 pixels horizontal resolution and 224, 239, 448, or 478 pixels vertically. Vertical resolutions of 224 or 239 are usually output in progressive scan, while 448 and 478 resolutions are interlaced. Colors are chosen from the 15-bit RGB color space, for a total of 32,768 possible colors. Graphics consist of up to 128 sprites and up to 4 background layers, all made up of combinations of 8×8 pixel tiles. Most graphics use palettes stored in CGRAM, with color 0 of any palette representing transparency.[3]

Sprites can be 8 × 8, 16 × 16, 32 × 32, or 64 × 64 pixels, each using one of eight 16-color palettes and tiles from one of two blocks of 256 in VRAM. Sprites may be flipped horizontally and vertically as a whole. Up to 32 sprites and 34 8 × 8 sprite tiles may appear on any one line; excess sprites or tiles would be dropped. Each sprite lies on one of 4 planes, however a lower-numbered sprite will always cover a higher-numbered sprite even if the latter is on a higher priority plane. This quirk is often used for complex clipping effects.[3]

Background layers in most modes range from 32 × 32 to 128 × 128 tiles, with each tile on one of two planes ("foreground" and "background") and using one of 8 palettes. Tiles are taken from a per-layer set of up to 1024 (as VRAM permits) and can be flipped horizontally and vertically. Each layer may be scrolled both horizontally and vertically. The number of background layers and the size of the palettes depends on the mode:[3]

- Mode 0: 4 layers, all using 4-color palettes. Each BG uses its own section of the SNES palette.

- Mode 1: 3 layers, two using 16-color palettes and one using 4-color palettes.

- Mode 2: 2 layers, both using 16-color palettes. Each tile can be individually scrolled.

- Mode 3: 2 layers, one using the full 256-color palette and one using 16-color palettes. The 256-color layer can also directly specify colors from an 11-bit (RGB443) colorspace.

- Mode 4: 2 layers, one using the full 256-color palette and one using 4-color palettes. The 256-color layer can directly specify colors, and each tile can be individually scrolled.

- Mode 5: 2 layers, one using 16-color palettes and one using 4-color palettes. Tile decoding is altered to facilitate use of the 512-width and interlaced resolutions.

- Mode 6: 1 layer, using 16-color palettes. Tile decoding is as in Mode 5, and each tile can be individually scrolled.

- Mode 7: 1 layer of 128×128 tiles from a set of 256, which may be interpreted as a 256-color one-plane layer or a 128-color two-plane layer. The layer may be rotated and scaled using matrix transformations. HDMA is often used to change the matrix parameters for each scanline to generate perspective effects.

Background layers may be individually pixelized, and layers and sprites can be individually clipped and combined by color addition or subtraction to generate more complex effects and greater color depths than can be specified directly.[3]

The PPU may be instructed to latch the current pixel position at any time during image output, both by game software and by the device attached to controller port 2. The game software may then read back this latched position. The PPU may also be used for fast 16-bit by 8-bit signed multiplication.[3]

Audio[edit]

| Audio reference | |

|---|---|

| Processors | Sony SPC700, Sony DSP |

| Clock rates | Input: 24.576 MHz SPC700: 1.024 MHz |

| Format | 16-bit ADPCM, 8 channels |

| Output | 32 kHz 16-bit stereo |

| Effects |

|

The audio subsystem consists of an 8-bit Sony SPC700, a 16-bit DSP, 64 kB[b] of SRAM shared by the two chips, and a 64 byte boot ROM. The audio subsystem is almost completely independent from the rest of the system: it is clocked at a nominal 24.576 MHz in both NTSC and PAL systems, and can only communicate with the CPU via 4 registers on Bus B.[4][5]

RAM is accessed at 3.072 MHz, with accesses multiplexed between the SPC700 (⅓) and the DSP (⅔). This RAM is used to store the SPC700 program and stack, the audio sample data and pointer table, and the DSP's echo buffer.[4]

The SPC700 runs programs (uploaded using the boot ROM program) to accept instructions and data from the CPU and to manipulate the DSP registers to generate the appropriate music and sound effects. The DSP generates a 16-bit waveform at 32 kHz by mixing input from 8 independent voices and an 8-tap FIR filter typically used for reverberation. Each voice can play its sample at a variable rate, withGaussian interpolation, stereo panning, and ADSR, linear, non-linear, or direct volume envelope adjustment. The voice and FIR filter outputs are mixed both for direct output and for future input into the FIR filter. All audio samples are compressed using ADPCM and alinear predictive coding, a method dubbed BRR.[4]

Hardware on the cartridge, expansion port, or both can provide stereo audio data for mixing into the DSP's analog audio output before it leaves the console.[6]

Since the audio subsystem is mostly self-contained, the state of the audio subsystem can be saved as an .SPC file, and the subsystem can be emulated in a stand-alone manner to play back all game music (except for a few games that constantly stream their samples from ROM). Custom cartridges or PC interfaces can be used to load .SPC files onto a real SNES SPC700 and DSP.

Onboard RAM[edit]

| Memory reference | |

|---|---|

| Main RAM | 128 kB[b] |

| Video RAM | 64 kB main RAM 512 + 32 bytes sprite RAM 256 × 15 bits palette RAM |

| Audio RAM | 64 kB |

The console contains 128 kB[b] of DRAM. This is mapped to various segments of Bus A, and can also be accessed in a serial fashion via registers on Bus B. The video and audio subsystems contain additional RAM reserved for use by those processors.[3]

Notes[edit]

- Jump up^ This quantity uses the standard decimal meaning of megabyte: 1,000,000 bytes.

- ^ Jump up to:a b c d e Unless otherwise specified, kilobyte (kB), megabyte (MB), and megabit (Mbit) are used in the binary sense in this article, referring to quantities of 1024 or 1,048,576.

References[edit]

- Jump up^ Jeremy Parish (2005-09-06). "PS1 10th Anniversary retrospective". 1UP.com. Retrieved 2007-05-27.

- ^ Jump up to:a b anomie. "Anomie's SNES Memory Mapping Doc" (text). Romhacking.net. Retrieved 2009-02-12.

- ^ Jump up to:a b c d e f g h i j anomie. "Anomie's Register Doc" (text). Romhacking.net. Retrieved 2007-04-21.

- ^ Jump up to:a b c anomie. "Anomie's S-DSP Doc" (text). Romhacking.net. Retrieved 2007-04-21.

- Jump up^ anomie. "Anomie's SPC700 Doc" (text). Romhacking.net. Retrieved 2007-04-21.

- Jump up^ anomie. "Anomie's SNES Port Doc" (text). Romhacking.net. Retrieved 2007-07-13.