OpenRisc-63-OpenRISC开发板O_board的设计,实现,调试与验证

引言

“书上学来终觉浅,绝知此事要躬行”,“百闻不如一练”。

无论是研究什么东西,学习和观摩是一回事,动手操作又是另外一回事。玩OpenRISC也是这样,只分析RTL,做一下仿真,对其感觉只能停留在‘纸上’,要想进一步加深对OpenRISC的理解,加深对CPU设计技术的掌握。除了分析RTL和仿真之外,还需要做很多基于OpenRISC的实验或者实际的项目才行。

要做实验就需要对应的开发板,目前国内的FPGA开发板种类很多,但没有一款是专门针对OpenRISC的,要想用目前市场上的开发板,主要面临两个问题,首先,大多数普通大众的开发板大多逻辑资源不足,无法运行ORPSoC;另外一个问题是,即使有高端的FPGA开发板,资源也够用,一般价格昂贵,此外还需要大量的RTL移植工作,bootloader移植工作和linux移植工作。这些移植工作需要的知识面很广,并且非常耗时。

我从2012年下半年开始接触OpenRISC,并购买了官方的ORDB2A开发板,价格适中,资源丰富,而且免去了大量的移植工作。

后来,随着研究的深入,我在CSDN建立的openrisc专栏(http://blog.csdn.net/column/details/openrisc.html),从那以后,越来越多的人参与进来,大家一起讨论问题,解决bug。其中深深体会到,很多问题重复的问题出现,此外还有很多问题根本不知道怎么描述,其中一个很重要的原因是大家没有一致的开发板,于是我建议大家购买官方的开发板,但是很快发现,官方的板子“Out-Of-Stock”了,没货了!

怎么办?当时有很多人“怂恿”我,让我仿照官方的板子,做一块一模一样的!!!

我当时考虑到这个板子既能用来学习嵌入式,又能学习FPGA和RTL,还能了解CPU设计技术,一举三得,所以就毫不犹豫就答应了,于是,从那时起,我就陷入了“苦海”。

从2013年9月初,开始画原理图,到现在(2014年1月5日)可以在板子上跑linux。前后四个多月的时间里,一波三折,五味杂陈。

本小节就回顾一下这四个月里做OpenRISC开发板--O_board 的酸甜苦辣。

1,O_board的logo

下面就是我用5分钟设计的logo。

2,原理图

O_board原理图,以opencores的ORDB2A的原理图为参考,重新用altium designer修正原图中的几个错误,并重画了一遍。

原理图,我已传到了QQ群的共享文件里(群号:277505520),有需要可加入此群之后下载。

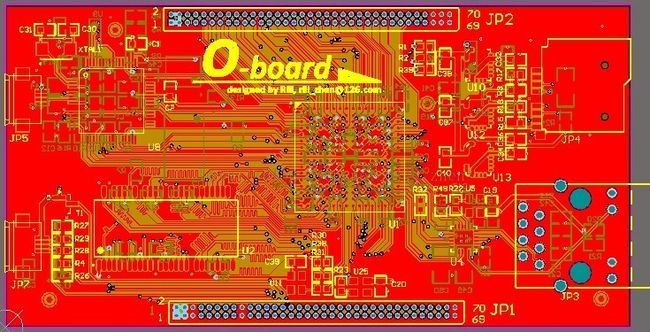

3,布局布线

如果说原理图是参考ORDB2A的话,那PCB的布局和布线就完全是原创了。O_board为了降低制版费用,决定采用4层板布线,要知道FBGA封装的FPGA芯片的256个引脚通过4层板全部扇出,对我这种菜鸟来说,确实有很大挑战。

下面是用altium designer完成P&R之后的样子。

4,制版

在布完线之后,检查一遍又一遍。然后就是找制版厂拿去制版了,由于比较关心制版质量,再加上制版工艺要求较高,所以我并没有找深圳那边的厂子,而是找了长沙的一个制版厂,并且采用沉金工艺。

把PCB文件扔出去之后,经过一周的等待,2013年12月10日,终于制版回来了。

5,采购物料

板子回来之后,下一步就是根据BOM,采购物料了。麻雀虽小五脏俱全。板子不大,但是芯片,电容,电阻,晶振,各种接插件,一样也不少。

由于官网的板子是欧洲生产的,所以O_board的很多物料,在国内都很难买到。

在我跑过无数次中发,搜遍淘宝之后,总算把所有的物料的买全了。由于买的量太少,我本人之前也从来没干过采购的活儿,为了买到原装正品的芯片和接插件,买了退,退了买,折腾了近半个月之后,总算搞定了。

6,焊接

制版也好了,物料也全了。下一步就是焊接了。

我是做软件出道的,半路转的硬件。虽说是硬件,但主要还是RTL,真正和PCB级别的打交道还是很少的。焊工就不用提了,那叫一个差啊。

于是我整理好物料,光板,焊接说明书之后,交给了北京的一家专业焊接厂。

三天之后,板子焊完回来了。

7,硬件调试

焊接完之后,我刚拿到板子,就发现有好几个地方焊的都不对,有的电阻不让焊,结果给焊上了;有的电阻漏焊了;有的芯片引脚焊错了;有的芯片引脚焊锡太多造成短路了。

总之,上电之后,电源灯根本不亮。

后来检查发现是电源芯片的几个引脚给焊短路了,有另外一个电源芯片的引脚虚焊了。

修改之后,发现板子发热很厉害,不到一分钟时间,板子就特别烫手,5V输入也被拉低到了4.6V。

gdb可以下载程序,但不能读写SDRAM。。。。。。。。

调试or_debug_proxy。。。。。。

调试adv_jtag_bridge。。。。。。

后来检查发现是晶振的引脚给焊错了。

。。。。。。

经过四五次修改,供电部分和晶振总算正常了。

下面是我晚上熬夜调试的情景。

需要说明的是,白天还要正常工作哦,毕竟公司给安排的工作是第一位的。

8,RTL的调试

由于主芯片EP4CE22F17C6N,在国内一直买不到原装正品,所以就采用了功能,逻辑资源,封装完全一致,但速度略低的EP4CE22F17C8N。

将ORPSoC中的PLL的频率降低之后(从50M降到20M),发现时序分析时出现错误,修改SDC文件,OK。

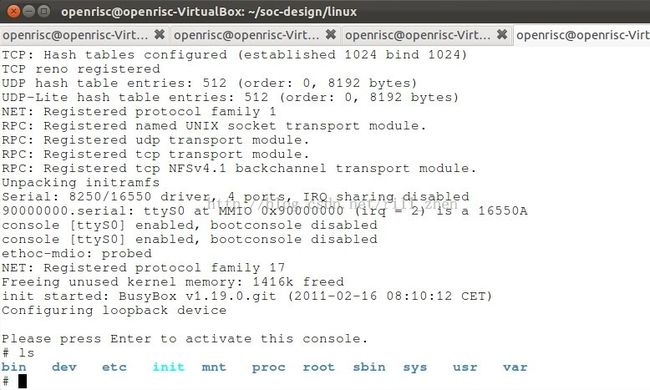

9,软件的调试

这里主要包括orpmon和linux。

同样是修改频率,之前移植到ML501时有过介绍,这里不再赘述。

10,验证

经过千难万险,总算可以跑软件了。

具体的操作步骤,之前已经介绍过了,如有疑问,请参考。

O_board 跑orpmon:

O_board跑linux:

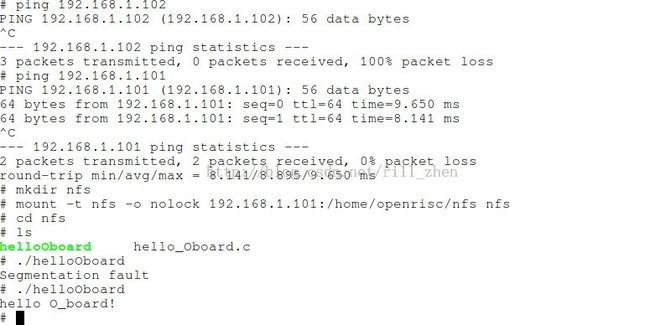

O_board起来linux之后,挂在PC机上的NFS,并运行“hello O_board”程序:

注意:出现Segmentation fault是因为我用or32-elf-gcc编译的,改用or32-linux-gcc之后,OK。

通过上面的测试,说明O_board的JTAG,串口,ORPSoC,SDRAM,ETH等模块完全工作正常!

11,上市

原理图经过6次改版,PCB经过3次改版,制版厂经过两次改版,现在板子的所有功能都没有问题了。

板子调试成功之后,就有好多人跟我说想要,在我免费送出去两块光板之后,发现这样下去不行,光快递费我都付不起。于是就有人建议我弄个网店什么的。于是就弄了一个淘宝小店,感兴趣的兄弟可以参考:

http://shop108365914.taobao.com/

需要注意的是,除了板子之外,还会提供全套的学习资料,包括已经搭建好的开发环境,还有很多实验例子。

附录:O_board feather

-ALTERA Cyclone IV E, 22K LUT (EP4CE22F17)

-SDRAM 32 Mbyte

-SPI FLASH, 1 Mbyte

-SDIO micro connector

-Fast Ethernet

-USB "on-the-go" HOST/SLAVE

-USB power, configuration, UARTs

-Expansion connectors

-Supply via USB

此外还会提供全套的学习资料,包括已经搭建好的开发环境,还有很多实验例子。

E-mail: [email protected]

小结

这次可真是体验了一下从画原理图,PCB的布局布线,再到制版,采购元器件,焊接,调试,FPGA开发,CPU设计,SoC开发,linux开发的全套流程啊,最后甚至还体会了一下销售+客服,感慨万千,收获颇多啊。