数字集成电路设计-2-除法器的verilog简单实现

引言

除法器在FPGA里怎么实现呢?当然不是让用“/”和“%”实现。

在Verilog HDL语言中虽然有除的运算指令,但是除运算符中的除数必须是2的幂,因此无法实现除数为任意整数的除法,很大程度上限制了它的使用领域。并且多数综合工具对于除运算指令不能综合出令人满意的结果,有些甚至不能给予综合。即使可以综合,也需要比较多的资源。对于这种情况,一般使用相应的算法来实现除法,分为两类,基于减法操作和基于乘法操作的算法。

2.1 实现算法

基于减法的除法器的算法:

对于32的无符号除法,被除数a除以除数b,他们的商和余数一定不会超过32位。首先将a转换成高32位为0,低32位为a的temp_a。把b转换成高32位为b,低32位为0的temp_b。在每个周期开始时,先将temp_a左移一位,末尾补0,然后与b比较,是否大于b,是则temp_a减去temp_b将且加上1,否则继续往下执行。上面的移位、比较和减法(视具体情况而定)要执行32次,执行结束后temp_a的高32位即为余数,低32位即为商。

2.2 verilog HDL代码

/*

* module:div_rill

* file name:div_rill.v

* syn:yes

* author:network

* modify:rill

* date:2012-09-07

*/

module div_rill

(

input[31:0] a,

input[31:0] b,

output reg [31:0] yshang,

output reg [31:0] yyushu

);

reg[31:0] tempa;

reg[31:0] tempb;

reg[63:0] temp_a;

reg[63:0] temp_b;

integer i;

always @(a or b)

begin

tempa <= a;

tempb <= b;

end

always @(tempa or tempb)

begin

temp_a = {32'h00000000,tempa};

temp_b = {tempb,32'h00000000};

for(i = 0;i < 32;i = i + 1)

begin

temp_a = {temp_a[62:0],1'b0};

if(temp_a[63:32] >= tempb)

temp_a = temp_a - temp_b + 1'b1;

else

temp_a = temp_a;

end

yshang <= temp_a[31:0];

yyushu <= temp_a[63:32];

end

endmodule

/*************** EOF ******************/

/* * module:div_rill_tb * file name:div_rill_tb.v * syn:no * author:rill * date:2012-09-07 */ `timescale 1ns/1ns module div_rill_tb; reg [31:0] a; reg [31:0] b; wire [31:0] yshang; wire [31:0] yyushu; initial begin #10 a = $random()%10000; b = $random()%1000; #100 a = $random()%1000; b = $random()%100; #100 a = $random()%100; b = $random()%10; #1000 $stop; end div_rill DIV_RILL ( .a (a), .b (b), .yshang (yshang), .yyushu (yyushu) ); endmodule /******** EOF ******************/

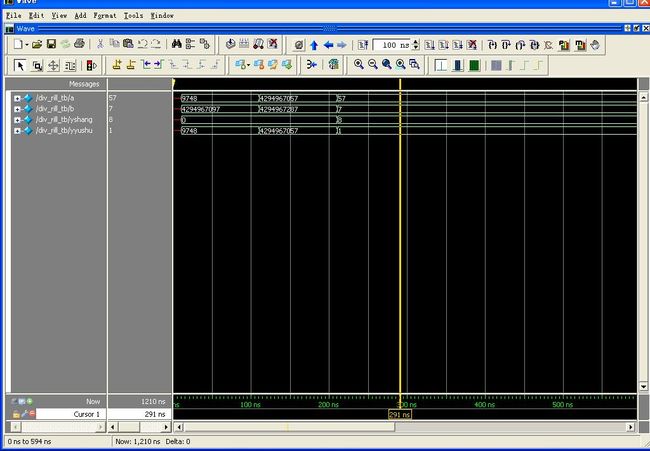

2.4 仿真结果

2.5 改进

1,将组合逻辑改成时序逻辑,用32个clk实现计算。

2,计算位宽可以配置,具有扩展性。

附录:算法推倒(非原创):

假设4bit的两数相除 a/b,商和余数最多只有4位 (假设1101/0010也就是13除以2得6余1)

我们先自己做二进制除法,则首先看a的MSB,若比除数小则看前两位,大则减除数,然后看余数,以此类推直到最后看到LSB;而上述算法道理一样,a左移进前四位目的就在于从a本身的MSB开始看起,移4次则是看到LSB为止,期间若比除数大,则减去除数,注意减完以后正是此时所剩的余数。而商呢则加到了这个数的末尾,因为只要比除数大,商就是1,而商0则是直接左移了,因为会自动补0。这里比较巧因为商可以随此时的a继续左移,然后新的商会继续加到末尾。经过比对会发现移4位后左右两边分别就是余数和商。

画个简单的图: