[signed][input]Verilog的有符号数输入测试

git://github.com/adream307/signedTest.git

一直错误得以为Verilog中的数据是无符号的。

测试脚本,在QuartusII中成功编译,且下载在硬件上运行。

//SIG.v module SIG( iCLK, oSY, oUY ); input iCLK; output [7:0] oSY; output [7:0] oUY; reg [7:0] x; wire [3:0] x1 = x[3:0]; wire [3:0] x2 = x[7:4]; wire [7:0] sy; wire [7:0] uy; assign oSY = sy; assign oUY = uy; always@(negedge iCLK) begin x<=x+8'd1; end SIGNED SIG_1( .iX1(x1), .iX2(x2), .oY(sy) ); UNSIGNED USIG_1( .iX1(x1), .iX2(x2), .oY(uy) ); endmodule

//SIGNED.v module SIGNED( iX1, iX2, oY ); input signed [3:0] iX1; input signed [3:0] iX2; output signed [7:0] oY; assign oY = iX1*iX2; endmodule

//UNSIGNED.v module UNSIGNED( iX1, iX2, oY ); input [3:0] iX1; input [3:0] iX2; output [7:0] oY; assign oY = iX1*iX2; endmodule

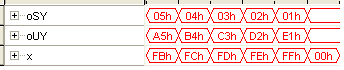

上图为SignalTapII的运行截图,可以发现当x=0xFF时,此时x1=0xF,x2=0xF。

对于SIGNED,有符号运算,x1=-1,x2=-1,所以结果为1。

而对于UNSIGNED,无符号运算,x1=15,x2=15,所以结果为225,即0xE1。