深入浅出FPGA-15-xilinx_zynq7000_EPP上一个简单实验(PL)

引言

之前用的都是alter的东西,xilinx的没实际做过,但大同小异,下面就以一个简单的例子来熟悉一下这个板子吧。

15.1 实验目的

1》 熟悉zynq7000 EPP资源和design suite。

15.2 实验环境

Board :ZYNQ7000 EPP

Device:XC7Z020CLG484ACX1221

Design suite:14.1 (ISE design tools)

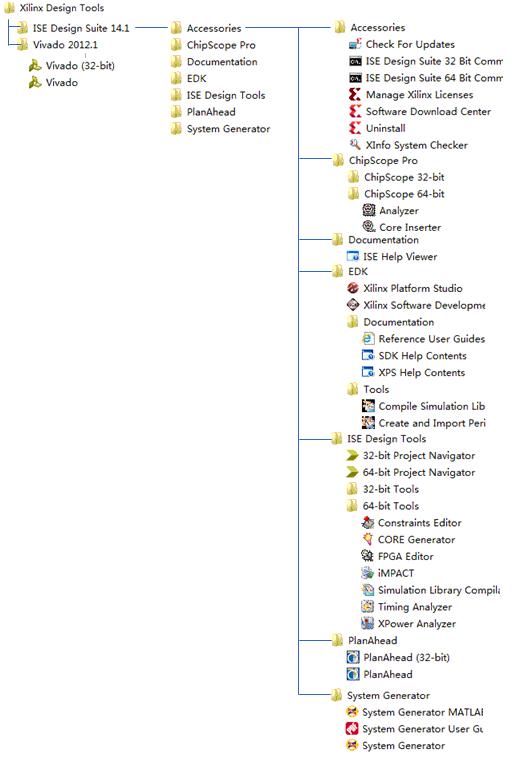

15.3 xilinx 开发套件结构

15.4 实验准备

1》 安装Xilinx Design Tools

2》 ZYNQ7000 EPP Setup

15.5 实验内容

1》 根据按键,来控制LED的on/off

2》 采用外部diff_clk(156.25MHz),并将其分频成两路不同频率后输出。

15.6 实验步骤

1》 编码rill_led.v和rill_led_tb.v,详见附录文件。

2》 创建ISE工程,modelsim工程。

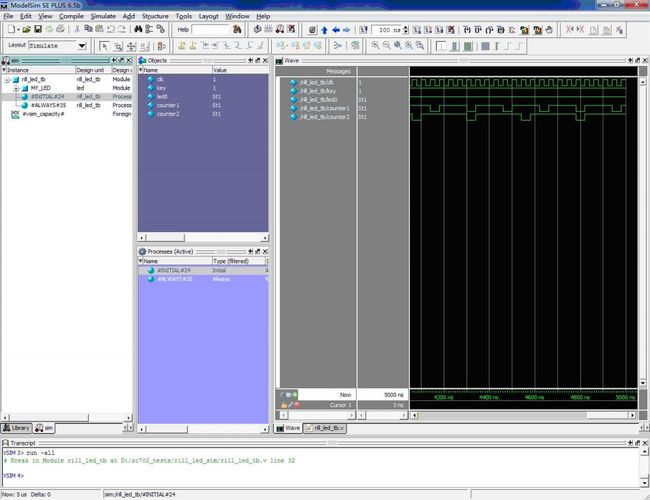

3》 用modelsim,进行function仿真。

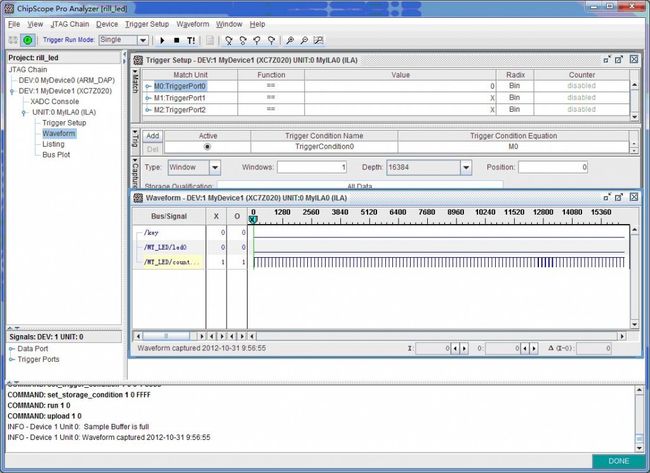

4》 用chipscope,进行FPGA验证。

15.7 实验结果

1》 modelsim仿真波形:

2》 chipscope 仿真波形

附:

1》ISE工程模块代码,UCF文件根据文档找到pin的定义就可以了。

/*

*file name: rill_led.v

*func : simple test

*date : 121030

*/

//===============top level module=============

module rill_led

(

input wire USRCLK_P,//diff_clk_156.25MHz

input wire USRCLK_N,

input wire GPIO_SW_N,

output wire PMOD2_2_LS,

output wire PMOD2_1_LS,

output wire PMOD2_0_LS

);

wire clk;

wire key;

wire led2;

wire led1;

wire led0;

IBUFDS #(.DIFF_TERM ("FALSE"),.IOSTANDARD("DEFAULT"))

my_ibufds

(

.O (clk),//buf output

.I(USRCLK_P),//diff_p buf input(connect directly to top-level port)

.IB (USRCLK_N)//diff_n buf input(connect directly to top-level port)

);

IBUF my_ibuf

(

.O (key),

.I (GPIO_SW_N)//Buffer input (connect directly to top-level port)

);

OBUF my_obuf2

(

.O (PMOD2_2_LS),//Buffer output (connect directly to top-level port)

.I (led2)

);

OBUF my_obuf1

(

.O (PMOD2_1_LS),//Buffer output (connect directly to top-level port)

.I (led1)

);

OBUF my_obuf0

(

.O (PMOD2_0_LS),//Buffer output (connect directly to top-level port)

.I (led0)

);

led MY_LED

(

.clk (clk),

.key (key),

.led0 (led0),

.counter_clk1 (led1),

.counter_clk2 (led2)

);

endmodule //end rill_led

//============================led================

module led

(

input wire clk,

input wire key,

output reg led0,

output reg counter_clk1,

output reg counter_clk2

);

parameter counter_max1 = 156;

parameter counter_max2 = 156;

reg [31:0] counter1 = 0;

reg [31:0] counter2 = 0;

always @(posedge clk)

begin

if(counter1 >= counter_max1)

begin

counter1 <= 0;

counter_clk1 <= 0;

end

else

begin

counter1 <= counter1 + 1;

counter_clk1 <= 1;

end

end

always @(posedge clk)

begin

if(counter2 >= counter_max2)

begin

counter2 <= 0;

counter_clk2 <= 0;

end

else

begin

counter2 <= counter2 + 1;

counter_clk2 <= 1;

end

end

always @(posedge clk)

begin

if(key)

begin

led0 <= 1;

end

else

begin

led0 <= 0;

end

end

endmodule //end led

/************* EOF *****************/

2,为了modelsim仿真方便,将上面代码进行简化,即只仿真实际模块。

/* *file name: rill_led.v *func : modelsim simple test *date : 121030 */ //============================led================ module led ( input wire clk, input wire key, output reg led0, output reg counter_clk1, output reg counter_clk2 ); parameter counter_max1 = 3; parameter counter_max2 = 5; reg [31:0] counter1 = 0; reg [31:0] counter2 = 0; always @(posedge clk) begin if(counter1 >= counter_max1) begin counter1 <= 0; counter_clk1 <= 0; end else begin counter1 <= counter1 + 1; counter_clk1 <= 1; end end always @(posedge clk) begin if(counter2 >= counter_max2) begin counter2 <= 0; counter_clk2 <= 0; end else begin counter2 <= counter2 + 1; counter_clk2 <= 1; end end always @(posedge clk) begin if(key) begin led0 <= 1; end else begin led0 <= 0; end end endmodule //end led /************* EOF *****************/

3,modelsim仿真testbench文件

`timescale 1ns/1ns module rill_led_tb; reg clk; reg key; wire led0; wire counter1; wire counter2; led MY_LED ( .clk (clk), .key (key), .led0(led0), .counter_clk1 (counter1), .counter_clk2 (counter2) ); initial begin clk = 0; #1000 key = 0; #1000 key = 1; #1000 key = 0; #1000 key = 1; #1000 $stop; end always #20 clk = ~clk; endmodule /*************** EOF ******************/