PCI总线

数据总线32位,可扩充到64位。

可进行突发(burst)式传输。

总线操作与处理器-存储器子系统操作并行。

总线时钟频率33MHZ或66MHZ,最高传输率可达528MB/S。

中央集中式总线仲裁

全自动配置、资源分配、PCI卡内有设备信息寄存器组为系统提供卡的信息,可实现即插即用(PNP)。

PCI总线规范独立于微处理器,通用性好。

PCI设备可以完全作为主控设备控制总线。

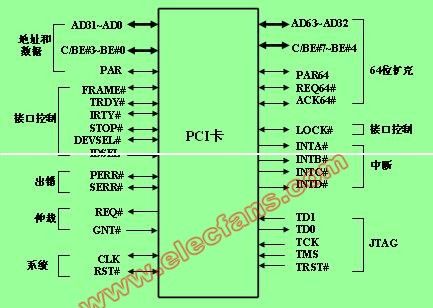

PCI总线引线:高密度接插件,分基本插座(32位)及扩充插座(64位)。

PCI总线引线示意图

PCI配置空间:PCI设备内有一个256B的配置存储器,为系统提供本设备的信息及申请系统存储空间所必需的参数。

PCI主要设备信息:

制造商标识(Vendor ID):PCI组织分配给厂家。

设备标识(Device ID):按产品分类给本卡的编号。

分类码(Class Code):本卡功能的分类码,如图卡、显示卡、解压卡等。

申请存储器空间:PCI卡内有存储器、以存储器编址的寄存器和I/O空间,为使驱动程序和应用程序能访问它们,需申请一段存储区域将它们定位。配置空间的基地址寄存器是专门用于申请存储器空间的。

PCI配置空间:

申请I/O空间:配置空间的基地址寄存器也用来进行系统I/O空间的申请。

中断资源申请:配置空间中的中断引脚和中断线用来向系统申请中断资源。

PCI配置空间分配

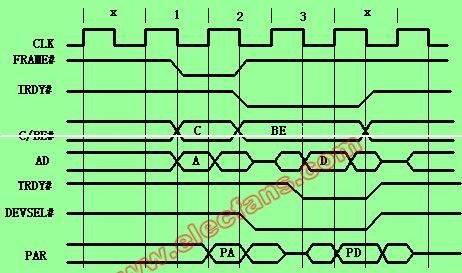

PCI总线访问:以读操作为例。

PCI总线是半同步方式操作,信号是否有效由时钟CLK的上升边采样来确定。

主设备启动总线周期:首先发出FRAME#信号,表明一次访问(总线周期)开始,地址及操作命令字信号出现在AD与C/BE#线上。

从设备响应:对地址和命令字译码后通过发出DEVSEL#有效信号进行响应,通知主设备,从设备已经被选中。

数据读取:主设备与从设备都准备好即IRDY#及TRDY#均有效,主设备将数据取走。

PCI总线访问:

多数据传送周期:PCI支持突发访问方式。

主模块占用一次总线可实现多个周期的数据访问。

第一数据地址由地址周期给出。

以后地址在此基础上按AD1、AD0的编码规定变化,如AD1、AD0为 00 时地址线性增加(每次加4)。

错误校验及报告:

PCI总线对AD线的有效信息都进行奇偶校验操作。PAR为校验位,发送方为AD与C/BE#线(共36位)配好校验值。

接收方在地址周期用SERR#报告校验结果,用PERR#报告数据周期校验结果。

配置空间访问:

配置空间的访问决定于命令字编码,在IDSEL线上发出有效信号,地址线低8位用于访问配置空间的256字节存储器。

总线仲裁:

PCI总线主设备通过REQ#与GNT#信号向总线仲裁器申请占用总线并得到确认。

单一读写操作

突发读写操作