s3c2440的时钟详解

这几天一直忙着研究移植U-boot,移植U-boot的过程中有一步很重要,就是要设置s3c2440的时钟,什么 Fin,Fclk,Hclk,Pclk,Mpll,Upll等时钟信号,让初学者看得一头雾水,各种信号混淆不清,本人特意花了一点时间,把这些东东理了理,现整理如下:

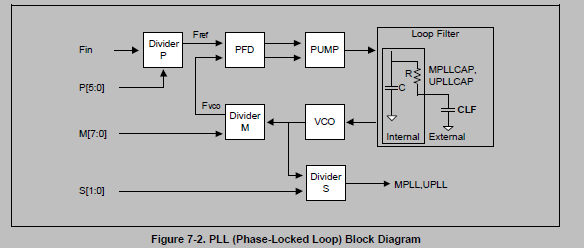

首先得弄清一个大的框架,s3c2440 cpu的默认工作主频有两种12MHz和16.9344MHz,也就是我们的晶振的频率,但一般12MHz的晶振用的比较多,Fin就是指我们接的晶振频率。大家都知道s3c2440上电正常工作后频率是远远大于12MHz和16.9344MHz的,我们的s3c2440的cpu正常工作时的频率就是405MHz,因此这就需要一个电路来提升频率,在s3c2440的datasheet中找到了这个电路,下面这个就是PLL电路:

由图中可以看出,Fin进去后,经过PLL电路,最终输出两个PLL信号频率即MPLL和UPLL,这两个又是什么呢

UPLL是专用于USB设备的,MPLL是用于CPU及外围电路的,不清楚,还是得找s3c2440的datasheet,下面这就是从datasheet中截取的:

UPLL是USB专用,这里就不讲了,下面重点讲下MPLL,刚才已经说了MPLL主要用于CPU和外围设备,但外围设备和CPU的工作频率并不一样啊,CPU的工作频率肯定比外设要高,这就必然要对MPLL进行处理,于是FCLK,HCLK,PCLK就登场了

首先讲下FCLK,首先看下datasheet中的介绍:

The Clock control logic in S3C2440A can generate the required clock signals including FCLK for CPU, HCLK for the

AHB bus peripherals, and PCLK for the APB bus peripherals.

相信搞嵌入式的都能看的懂,FCLK是CPU用的,HCLK是AHB总线用的,比如说SDRAM,PCLK是APB总线用的,比如说UART。这三个我们一个个来讲解,首先看FCLK,CPU用的,看datasheet中的关于FCLK的时序图,我们就会看出一些东东

从上面的图中可以看到FCLK在CPU上电后,过了一段时间就发生了比较大的变化,明显值变大了,从上面这个图中我们可以大致看出s3c2440上电启动过程:

1、上电几毫秒后(power由低变高),晶振输出稳定,此时FCLK=晶振频率,nRESET信号恢复高电平后,CPU开始执行指令。

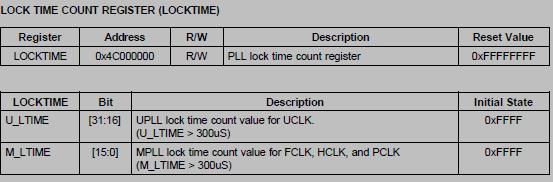

2、我们可以在程序开头启动MPLL,在设置MPLL的几个寄存器后,需要等待一段时间(Lock Time),MPLL的输出才稳定。在这段时间(Lock Time)内,FCLK停振,CPU停止工作。Lock Time的长短由寄存器LOCKTIME设定。

3、Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。

现在对FCLK进行总结一下,FCLK,在CPU上电后,晶振开始正常工作,此时FCLK=晶振频率,注意此时不存在MPLL,经过PLL电路后,得到MPLL,UPLL。此时FCLK=MPLL。

有了MPLL后,才可以谈对s3c2440的时钟设置,说通俗一点,MPLL就相当于一个工资标准,就拿我们公司做个例子吧,主管就相当于CPU,主管下面有各个项目组,每个项目组都有组长,组长下面有象我一样的员工,呵呵。。。哥悲剧啊 ,处于公司最底层,呵呵。。。

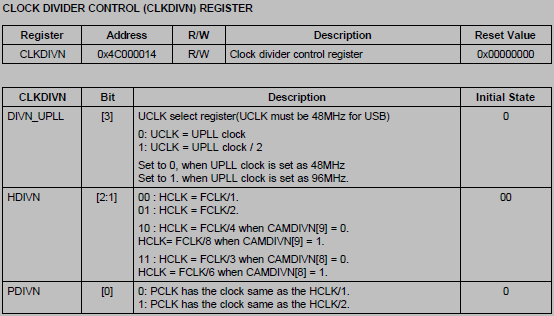

主管的工资肯定是最高的,因为CPU工作频率是最高的,所以主管就拿MPLL的标准,就是405MHz,仅次于主管的呢,也就是组长,s3c2440里就是内存了,也就是AHB总线用的,组长就按HCLK的标准,组长的工资肯定是根据主管的工资定的,s3c2440里确定的是HCLK=FCLK/4,普通员工就是PCLK=HCLK/2,也就是APB总线使用的时钟频率。总的来说分频比为FCLK:HCLK:PCLK=1:4:8.这个分配标准是由谁定的呢,公司里肯定是Boss了,也就是寄存器了,也就是我们的CLKDIVN寄存器,看下datasheet中的介绍大家酒清楚了:

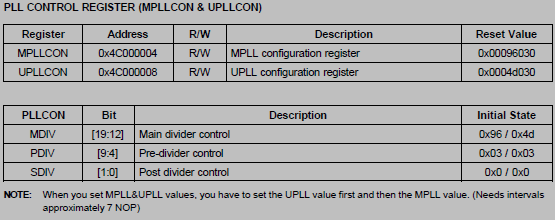

组长,和员工的工资都是参照主管的工资而定的,那主管的工资怎么定呢,当然也是寄存器了,看datasheet介绍:

上面这个表,就给出了方法,对于12MHz的晶振,要想经过PLL电路得到405MHz,查表得应该设置MDIV、PDIV、SDIV分别为0x7f、2、1,当然也有计算公式,计算公式我在这里就不贴出来了,datasheet里面有,上面的表就是根据那个公式算来的。那在哪里设置这3个的值呢,还是datasheet:

从上图可以看出,我们只需要设置MPLLCON寄存器就可以确定FCLK了,再通过CLKDIVN寄存器我们就可以设置FCLK、HCLK、PCLK三者之间的比例了。

关于时钟设置的还有一个寄存器,就是LOCKTIME,在上面的时序图中可以看到它的身影,datasheet中介绍:

前面说过,MPLL启动后需要等待一段时间(Lock Time),使得其输出稳定。位[31:16]用于UPLL,位[15:0]用于MPLL。使用确省值0x00ffffff即可。

讲到这里,关于s3c2440的时钟就基本结束了,写得好累啊,本人也是刚工作的菜鸟,由于只是有限,文中难免有错误,还忘浸淫嵌入式多年的大侠指正,小弟不甚感激!