3位BCD加法计数器 VDHL设计与实现

作者:chenjieb520

一.设计目的

学习BCD加法计数器的设计、分析和测试方法。

二.设计内容

设计一个3位BCD计数器,含异步清零和同步时钟使能。计数器的控制信号由DE2平台上的50 MHz时钟提供,再经过分频器降频到1HZ输出。计数器的输出显示在HEX2~HEX0上,用KEY0可以将计数器清零。

三.程序设计原理

(1) 新建一个QuartusⅡ工程。

(2) 建立一个VHDL文件,实现所要求的电路。

(3) 将VHDL文件添加到工程中,编译工程并对电路进行仿真,确定其功能的正确性。

(4) 分配引脚,将显示输出连接到HEX2~HEX0,用KEY0作为同步清除端。

(5) 重新编译工程,将电路下载到DE2平台上并测试其功能。

四.程序流程图

五.源程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNTBCD IS

PORT(CLK,RST,EN:IN STD_LOGIC;

LED7SA,LED7SB,LED7SC:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END CNTBCD;

ARCHITECTURE behav OF CNTBCD IS

SIGNAL CLK2,FULL,FOUT:STD_LOGIC;

SIGNAL A,B,C:INTEGER RANGE 9 DOWNTO 0;

BEGIN

CLK0:PROCESS(CLK)

VARIABLE CNT23:STD_LOGIC_VECTOR(23 DOWNTO 0);

BEGIN

IF CLK'EVENT AND CLK='1' THEN

CNT23:=CNT23+1;

END IF;

IF CNT23(15)='1' THEN

CLK2<='1';

ELSE CLK2<='0';

END IF;

END PROCESS CLK0;

PROCESS(CLK2,RST,EN)

variable CQ1,CQ2:INTEGER;

BEGIN

IF RST='1' THEN A<=0;B<=0;C<=0;

ELSIF CLK2'EVENT AND CLK2='1' THEN

IF EN='1' THEN

IF A<9 THEN A<=A+1;

ELSE

A<=0;B<=B+1;

IF B=9 THEN

B<=0;C<=C+1;

END IF;

IF C=9 THEN

C<=0;B<=0;A<=0;

END IF;

END IF;

END IF;

END IF;

END PROCESS;

PROCESS(A)

BEGIN

CASE A IS

WHEN 0 => LED7SA<="1000000";

WHEN 1 => LED7SA<="1111001";

WHEN 2 => LED7SA<="0100100";

WHEN 3 => LED7SA<="0110000";

WHEN 4 => LED7SA<="0011001";

WHEN 5 => LED7SA<="0010010";

WHEN 6 => LED7SA<="0000011";

WHEN 7 => LED7SA<="1111000";

WHEN 8 => LED7SA<="0000000";

WHEN 9 => LED7SA<="0011000";

WHEN OTHERS=>NULL;

END CASE;

END PROCESS;

PROCESS(B)

BEGIN

CASE B IS

WHEN 0 => LED7SB<="1000000";

WHEN 1 => LED7SB<="1111001";

WHEN 2 => LED7SB<="0100100";

WHEN 3 => LED7SB<="0110000";

WHEN 4 => LED7SB<="0011001";

WHEN 5 => LED7SB<="0010010";

WHEN 6 => LED7SB<="0000011";

WHEN 7 => LED7SB<="1111000";

WHEN 8 => LED7SB<="0000000";

WHEN 9 => LED7SB<="0011000";

WHEN OTHERS=>NULL;

END CASE;

END PROCESS;

PROCESS(C)

BEGIN

CASE C IS

WHEN 0 => LED7SC<="1000000";

WHEN 1 => LED7SC<="1111001";

WHEN 2 => LED7SC<="0100100";

WHEN 3 => LED7SC<="0110000";

WHEN 4 => LED7SC<="0011001";

WHEN 5 => LED7SC<="0010010";

WHEN 6 => LED7SC<="0000011";

WHEN 7 => LED7SC<="1111000";

WHEN 8 => LED7SC<="0000000";

WHEN 9 => LED7SC<="0011000";

WHEN OTHERS=>NULL;

END CASE;

END PROCESS;

END behav;

六.调试过程

根据上述代码的进行引脚的分配,这里不详细讲述分配的过程。可以得到和实验要求相吻合的结果。

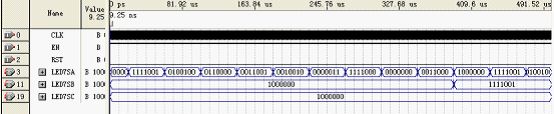

在波形的模拟中,可以得到如下的波形:

这里必须说明是,为了使得模拟的时间更短一些,这里需要将原来的代码中的

IF CNT23(23)='1' THEN 改为 IF CNT23(10)='1' THEN

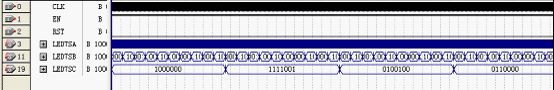

这里才能模拟出如下的波形。波形可以看出,这样的时间设置依然没有得到令人满意的数据。因为B和C的值只是出现了一点点而已,不至于说明程序的准确性。所以这里继续改为IF CNT23(5)='1' THEN,得到如下的波形(由于波形实在太多了,所以这里显示得有点密集):

七.遇到的问题及解决方法

在本次实验中,由于在模拟波形的时候,不能按照在硬件上模拟时所采用的分频倍数。因为这样的话(在硬件中是1s),而在模拟波形,那需要模拟很长的时间,而且的时间的波形限制方面,应该分频数少一点,使得时钟周期尽量保持在微妙级别,这样的就可以得到比较理想的模拟波形了,否则得出的波形将会一直停留在A=0,B=0,C=0的状态上。而且尽量分频得少一点(在模拟波形的时候,否则这个时间将会很长)。

八.参考文献

EDA技术与VHDL(第二版) 潘松 黄继业 编著