s3c2440时钟配置

一、时钟源选择

S3C2440的主时钟源一般为12MHz或16.9344MHz,然后再使用PLL电路倍频产生更高的主频供CPU及外围器件使用。

主时钟源来自外部晶振(XTIpll)或者外部时钟,用芯片引脚OM[3:2]来选择,一般将这两位接地。

二、时钟倍频设置

S3C2440有两个PLL:MPLL和UPLL。UPLL专用与USB设备,MPLL用于CPU及其他外围器件。通过MPLL会产生三个部分的时钟频率:FCLK、HCLK、PLCK。FCLK用于CPU核,HCLK用于AHB总线的设备(比如SDRAM),PCLK用于APB总线的设备(比如UART)。

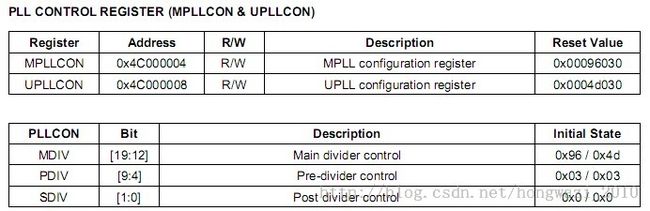

设置PLL相关寄存器可对输入的Fin=12MHz的晶振频率进行倍频。S3C2440使用了三个倍频因子MDIV、PDIV和SDIV来设置倍频,通过寄存器MPLLCON&UPLLCON可设置倍频因子。其中MPLLCON寄存器用于设置处理器内核时钟(主频FCLK),其输入输出频率间的关系为

FCLK=MPLL=(2*m*Fin)/(p*2^s) ,其中m=(MDIV+8), p=(PDIV+2), s=SDIV。

其中UPLLCON寄存器用于产生48MHz或96MHz,提供USB时钟(UCLK),其输入输出频率间的关系为

UCLK=UPLL=(m * Fin) / (p * 2^s) ,其中m=(MDIV+8), p=(PDIV+2), s=SDI

2.1 MPLLCON和UPLLCON寄存器设置

例子:

MPLLCON=(0x7f << 12)|(0x02 << 4)|(0x01) 带入上面的公式可以得到FCLK=400MHz

UPLLCON =(0x38<<12)|(0x02<<4)|(0x02) 带入上面的公式可以得到UCLK=48MHz

2.2 LOCK TIME COUNT REGISTER (LOCKTIME)

设置MPLL的几个寄存器后,需要等待一段时间(Lock Time),MPLL的输出才稳定。在这段时间(Lock Time)内,FCLK停振,CPU停止工作。Lock Time的长短由寄存器LOCKTIME设定.Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。此寄存器一般设为0xFFFFFFFF。

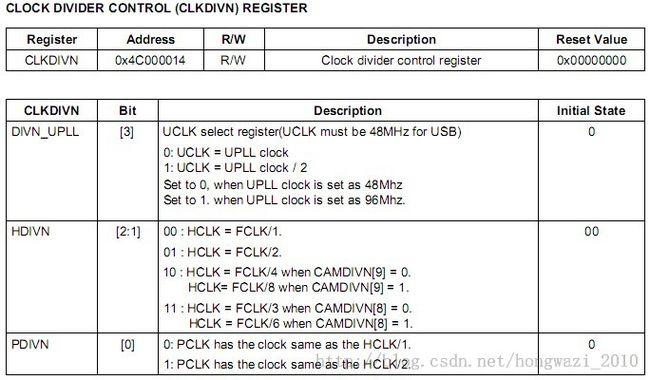

2.3 CLKDIVN和CAMDIVN

通过MPLL会产生三个部分的时钟频率:FCLK、HCLK、PLCK。FCLK用于CPU核,HCLK用于AHB总线的设备(比如SDRAM),PCLK用于APB总线的设备(比如UART)。用户可以通过设置CLKDIVN和CAMDIVN寄存器来控制HCLK和PLCK的分频系数。

例子:

CLKDIVN=0x05 CAMDIVN默认值即可 即FCLK:HCLK:PCLK=1:4:8

三、实例汇编代码

MPLL的启动流程:

1、上电几毫秒后,晶振输出稳定,FCLK=晶振频率,nRESET信号恢复高电平后,CPU开始执行指令。

2、程序开头启动MPLL,在设置MPLL的几个寄存器后,需要等待一段时间(Lock Time),MPLL的输出才稳定。在这段时间(Lock Time)内,FCLK停振,CPU停止工作。Lock Time的长短由寄存器LOCKTIME设定。

3、Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。

AREA Example,CODE,READONLY;声明代码段Example

ENTRY ;标示程序入口

CODE32 ;声明32位ARM指令

START LDR R0, =0x000ad022 ;FCLK=271.5MHz

LDR R1, =0x4C000004 ;MPLLCON寄存器

STR R0,[R1]

LDR R0, =0x00000005 ;FCLK:HCLK:PCLK=1:4:8

LDR R1, =0x4C000014 CLOCK DIVIDER control

STR R0,[R1]

LDR R0, =(0xa<<18) ;CLKOUT0、CLKOUT1引脚复用

LDR R1, =0x56000070 ;端口H控制寄存器

STR R0,[R1]

LDR R0, =(0x86<<3) ;输出HCLK及PCLK

LDR R1, =0x56000080 ;MISCCR寄存器

STR R0,[R1]

END

通过示波器测量,PCLK约为34MHz,HCLK约为68MHz