S3C2440的时钟设置

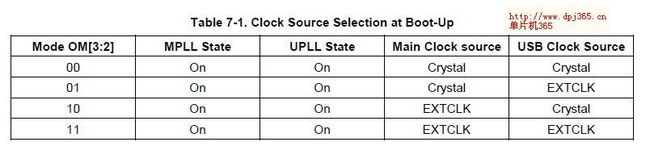

一个嵌入式系统中,晶振就像心脏。必须先确定晶振,设置好系统的时钟,WDT,UART,PWM,TIMER等模块才能正常工作。和51系列单片机相比,S3C2440的时钟电路很复杂。首先通过引脚OM2,OM3来选择时钟源。

以TQ2440开发板为例,OM2,OM3都接地,外接12M晶振,主时钟源和USB时钟源都是外部晶振。

S3C2440具有2个PLL(Phase Locked Loop:用来产生高频的电路),一个是MPLL, 用于产生FCLK, HCLK, PCLK三种频率, 这三种频率分别有不同的用途:

FCLK是CPU提供的时钟信号,如果提到CPU的主频是400MHz,就是指的这个时钟信号。

HCLK是为AHB总线提供的时钟信号, Advanced High-performance Bus,主要用于高速外设,比如内存控制器,中断控制器,LCD控制器, DMA 以及USB host 。

PCLK是为APB总线提供的时钟信号,Advanced Peripherals Bus,主要用于低速外设,比如WATCHDOG,IIS, I2C, SDI/MMC, GPIO,RTC ,UART,PWM,ADC and SPI等等。

另外一个是UPLL,专门用于驱动USB host/Device。并且驱动USB host/Device的频率必须为48MHz。

时钟电路相关寄存器总共有7个,下面分别介绍。

MPLLCON(0X4C00 0004)和UPLLCON(0X4C00 0008)

这两个寄存器用来设置主锁相环产生的时钟和USB锁相环产生的时钟。

MPLL=(2*m*Fin)/(p*2^s) UPLL=(m*Fin)/(p*2^s)

其中m=(MDIV+8),p=(PDIV+2),s=SDIV

P,M范围:1<=P<=62,1<=M<=248

注意:MDIV[19:12],PDIV[9:4],SDIV[1:0],当设置MPLL和UPLL值的时候,需要先设置UPLL再设置MPLL。

例如:MPLLCON = (92<<12) | (1<<4) |(1);//FCLK=400M

这里MDIV=92,PDIV=1,SDIV=1,那么m=100,p=3,s=1,且Fin=12M,所以FCLK=400M

CLKCON(0X4C00 000C) 控制各种模块如SPI,IIC,UART等的时钟电路开关以及系统的SLEEP,IDLE模式,以便降低系统功耗。默认值是全部时钟电路打开,系统工作在正常模式。

CLKSLOW(0X4C00 0010)用来选择系统是否进入慢模式,以及是否关闭MPLL或UPLL,和在慢模式下的分频率。

CLKDIVN(0X4C00 0014)和CAMDIVN(0X4C00 0018照相机时钟分割寄存器)两个寄存器配合来确定FCLK,HCLK,PCLK的比例。

LOCKTIME(0X4C00 0000)设置MPLL,UPLL的锁存时间,采用默认值0XFFFF FFFF,锁存时间各为300us。

说到锁存时间,就要分析下S3C2440的时钟工作过程。

在系统复位时,晶振起振稳定后,PLL开始按照默认值开始工作,但是在复位时,PLL工作是不稳定的,所以S3C2440用FIN(12M)作为MPLL。只到一个新的值写入MPLLCON,UPLLCON,即使用户不想改变复位后PLLCON的默认值,仍然需要把这个默认值写入PLLCON,写入值之后,系统会自动插入一个PLL LOCK TIME,也就是LOCKTIME寄存器中设置的300us。300us后,PLL就开始正常工作。

在系统正常工作时,如果要改变FCLK,写入新值到MPLLCON后,系统也会插入一个PLL LOCK TIME,300us后FCLK就变成新的频率。

S3C2440文档里有个注意的地方:

如果HDIVN不为0,根据如下指令,CPU总线模式从Fast Bus Mode 变为Asynchronous(异步总线模式),2440没有同步总线模式)

MMU_setAsyncBusMode

mrc p15,0,r0,c0,0

orr r0,r0,#R1_nF:OR:R1_iA

mcr P15,0,r0,c1,c0,0

如果HDIVN不为0,且CPU总线模式为Fast Bus mode,CPU的时钟为HCLK.,这种方式可以用在将CPU频率降低,但是却又不改变HCLK和PCLK.

查了些资料,ARM内核在启动后工作在快速模式,改变HDIVN值后,就要进入异步模式。转换的具体原因涉及到ARM内核。目前还没办法弄懂,ARM的学习就像走进一条不知道多长的隧道,难见光明。