JTAG学习笔记 (2)

学习是知行循环的过程,当我们了解的一个东西,就需要通过实践的方法加深对他的认识。

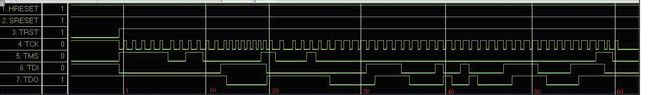

这里我们利用WIGGLER的并口卡,通过并口模拟JTAG时序,对端的设备是MPC8247的板卡,我们将在逻辑分析仪上捕获的数据和TAP的16个状态的状态机比对来进行分析。

下面是一个BYPASS指令:

发送的数据:

"00001111000010010000111100001111"

软件上接收到的数据:

11100001111000010010000111100000

从接受到的数据上看,发现:

1. 最后收到的数据在最高位上

2. 第一个在TDO上捕获的数据被正常的情况早了一个CLK,这个应该是软件的问题,从下面的波形上看是正确的。( 当写完下面的drScan的时候,我觉得这个不应该叫做一个错误,而是一个特性 )

图片URL:

http://hi.csdn.net/attachment/201002/9/3466916_12657282153Bss.jpg

HRESET和SRESET因为没有进行控制,板卡默认上拉。

前5个CLK,TMS为高,表示复位JTAG逻辑,这时候进入Test-Logic Reset状态

第6个CLK进入Run-Test/Idle状态,第7个CLK在Run-Test/Idle状态自旋一次

第8个CLK进入Select-DR-Scan状态

第9个CLK进入Select-IR-Scan状态

第10个CLK进入Capture-IR状态

第11个CLK进入Shift-IR状态

第12~18 CLK在 Shift-IR状态自旋,将BYPASS指令的前7Bits放在TDI信号线上(BYPASS 命令为8个1)

第19 个CLK进入Exit-IR状态,同时将BYPASS指令的第8Bit放在TDI信号线上(BYPASS 命令为8个1)

第20个CLK进入Update-IR状态

第21个CLK进入Run-Test/Idle状态,第22,23个CLK在Run-Test/Idle状态自旋

第24个CLK进入Select-DR-Scan状态

第25个CLK进入Capture-DR状态

第26个CLK进入Shift-DR状态

第27~57(27+32-1-1)CLK在Shift-DR状态自旋,同时将用户数据的前31Bits放在TDI信号线上

第58 个CLK进入Exit-DR状态,同时将用户数据的第32Bit放在TDI信号线上

第59 个CLK进入Update-DR状态

第60个CLK进入Run-Test/Idle状态

其中:

CLK12~CLK19放置命令字

CLK27~CLK58放置用户数据

CLK28~CLK59读取用户数据(软件上捕获的是CLK27~CLK58)

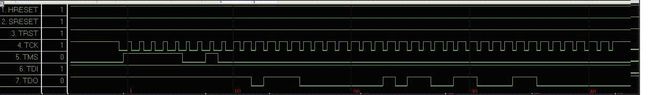

下面是一个drScan操作情况:( 对于在菊花链上有多个设备情况下的扫描操作还不清楚 )

扫描菊花链,扫描到设备:MPC8247

Checking cable...

00000001100011001101000000011101

ID code database file does not exist.

下面这段来自于飞思卡尔提供的BSDL文件,BSDL是Boundary Scan Description Language,里面包含了IEEE规定的必须开发给用户的指令,以及每个PIN脚在扫描链上的位置(CellNum),PIN脚的功能描述,默认的电平状态等信息。

下面这段是数据寄存器IDCODE的数值。

attribute IDCODE_REGISTER of pq27e : entity is

"0000" & -- Version

"000110" & -- Design Center Number

"0011001101" & -- Sequence Number

"00000001110" & -- Manufacturer Identity

"1"; -- IEEE 1149.1 Requirement

图片URL:

http://hi.csdn.net/attachment/201002/9/3466916_1265728416zZX4.jpg

前5个CLK,TMS为高,表示复位JTAG逻辑,这时候进入Test-Logic Reset状态

第6个CLK进入Run-Test/Idle状态,第7个CLK在Run-Test/Idle状态自旋一次

第8个CLK进入Select-DR-Scan状态

第9个CLK进入Capture-DR状态

第10个CLK进入Shift-DR状态

第11~42CLK在Shift-DR状态自旋,同时IDCode寄存器内部的32Bits数据将出现在TDO的信号线上

从波形上可以看到因为是软件模拟出的波形,所以不是很漂亮,通过测量发现TCK的时钟在100KHz到200KHz之间。

而且在程序运行的时候CPU的占用是很高的。