spartan-3e starter kit board 入门

本篇博文简要介绍下通过ISE操作spartan-3e starter kit board上的4个滑动开关和8个led灯。

一、设计思路

1、板子上的led灯一端已经接低电平了,所以,要点亮的话就要向另一端输出高电平即可。

2、板子上自带的50MHZ晶振以及reset键都是设计模块的输入。以便能够及时响应3中的输入。

3、4个滑动开关中SW2、SW1、SW0作为另一组输入。

4、SW2、SW1、SW0的编码即是要被点亮的led灯。即其=000,则led0点亮、=001,led1点亮。

二、从ISE建立project到最终将.bit下载到板子

1、fire->new project

2、芯片的型号以及封装必须选择好

3、

4、右键单击工程管理区,选择new source,选择verilog module,填入fire name

5、设置模块的输入输出口,就是verilog源码中的input与output

6、

7、在客户区输入所要构建的模块的verilog源码

8、源码编辑好后,左键双击过程管理区的check syntax确认有没有语法错误

9、左键双击synthesize-xst完成综合

10、view选择simulation,右键单击工程管理区,选择new source,选择verilog test fixture,输入file name

11、

12、

13、输入测试代码,本例就是在客户区的红线区域。其他例子不一定!

14、右键单击simulate behavioral model,选择properties设置仿真的一些参数。

15、

16、右键单击工程管理区,选择new source,选择implementation constraints file

17、

18、输入约束代码

19、双击implement design,完成实现步骤

20、实现完成之后,通过design summary,查看pinout report。如果,引脚约束与你定义的一致,则正确;

否则,右键依次双击synthesize-xst与implement design,直到引脚约束正确方可进行下一步。

21、双击generate programming file,产生.bit文件

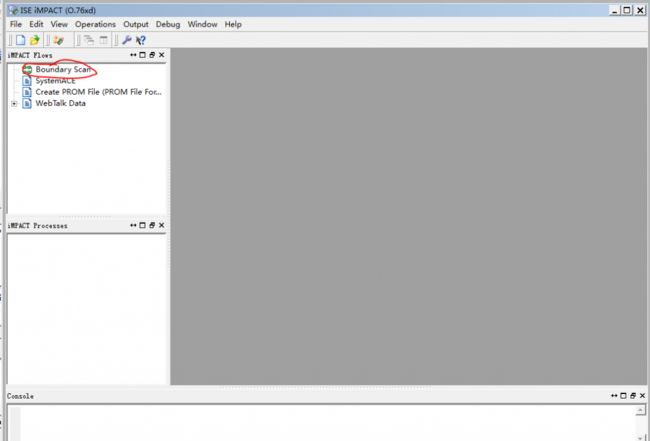

22、双击configure target device,点击ok,代开iMPACT准备下载.bit文件到板子

23、双击boundary scan

24、

25、左键点击initialize chain,检测板子的存在

26、选择要现下载的.bit文件

27、

28、

29、

30、鼠标放在图标上(颜色会变深),点击右键,选择program,如果提示program successed,则说明

已成功下载。

31、操作板子,观察实验结果是否符合设计。

三、总结

1、博主的ISE版本是13.3。不同的版本操作可能会有所差异。

2、实验代码:

led代码:

module led(CLK,RST,LED,MODE);

input CLK;

input RST;

input [2:0] MODE;

output [7:0] LED;

reg [7:0] LED = 8'b10101010;

reg [24:0] cnt_clk;

reg div_clk;

always @ (posedge CLK or posedge RST)begin

if(RST)begin

cnt_clk <= 25'd0;

div_clk <= 1'b0;

end

else begin

if(cnt_clk == 25'd9999999)begin

cnt_clk <=25'd0;

div_clk <= ~div_clk;

end

else begin

cnt_clk <= cnt_clk + 1'b1;

div_clk <= div_clk;

end

end

end

always @ (posedge div_clk or posedge RST)begin

if(RST)begin

LED <= 8'b10101010;

end

else begin

case (MODE)

3'b000 : LED <= 8'b1;

3'b001 : LED <= 8'b10;

3'b010 : LED <= 8'b100;

3'b011 : LED <= 8'b1000;

3'b100 : LED <= 8'b10000;

3'b101 : LED <= 8'b100000;

3'b110 : LED <= 8'b1000000;

3'b111 : LED <= 8'b10000000;

endcase

end

end

endmodule

ucf约束文件:

NET "CLK" LOC = "C9" | IOSTANDARD = LVCMOS33; NET "CLK" PERIOD = 20ns HIGH 40%; NET "RST" LOC = "K17" | IOSTANDARD = LVTTL | PULLDOWN; NET "MODE<0>" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP; NET "MODE<1>" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP; NET "MODE<2>" LOC = "H18" | IOSTANDARD = LVTTL | PULLUP; NET "LED<0>" LOC = "F12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "LED<1>" LOC = "E12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "LED<2>" LOC = "E11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "LED<3>" LOC = "F11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "LED<4>" LOC = "C11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "LED<5>" LOC = "D11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "LED<6>" LOC = "E9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4; NET "LED<7>" LOC = "F9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 4;

仿真代码:

module led_test;

// Inputs

reg CLK;

reg RST;

reg [2:0] MODE;

// Outputs

wire [7:0] LED;

// Instantiate the Unit Under Test (UUT)

led uut (

.CLK(CLK),

.RST(RST),

.LED(LED),

.MODE(MODE)

);

always #5 CLK = ~CLK;

initial begin

// Initialize Inputs

CLK = 0;

RST = 0;

MODE = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

RST = 0;

MODE = 3'b001;

#10000;

MODE = 3'b010;

#10000;

MODE = 3'b100;

#1000 $stop;

end

endmodule

3、以前学过cc2430的板子,现在开始学FPGA,纯菜鸟一枚呀。不过总体感觉来说,硬件的东西,

那些芯片的资料是很重要的。一块电路板上一般都是一个处理器外加若干外设,外设也和处理器有

连接了,但这都是坐在电路板上了。需要芯片资料来获得一定的信息,便于我们使用。

4、也期待大神们不吝赐教!