Intel Spec. Processor Instructions 6 - Instruction Statements

Intel Spec. Processor Instructions 6 - Instruction Statements

I. Instruction statement syntax

assembler instruction: [label] : [prefix] mnemonic [argument [, . . . ]]

label: a unique identifier that defines a label, optional

prefix: a processor instruction prefix (LOCK or REP), optional

mnemonic: a processor or floating-point coprocessor instruction or programmer-defined codemacro

argument: an operand. one, two, three explicit operands, floating-point coprocessor instruction at most two explicit operands

II. Instruction attributes

- Address size attributes

The assembler checks the USE attribute of the segment, EX: .code32 or .code16, AT&T assembler

The instruction contains an anonymous reference the assembler, EX: push dword ptr [eax], implies the USE32 attribute because of eax is 32-bit register

- Operand size attributes

An instruction that accesses dwords (32-bits) or words (16-bits) has an operand size attribute of 32- or 16-bits, respectively

An instruction that accesses a byte has the operand size attribute of the current code segment

III. Instruction encoding format

- Instruction prefix codes

Instruction prefix

F3H REP/REPE/REPZ prefix

F2H REPNE/REPNZ prefix

F0H LOCK prefix

Segment override

2EH CS segment override prefix

36H SS segment override prefix

3EH DS segment override prefix

26H ES segment override prefix

64H FS segment override prefix

65H GS segment override prefix

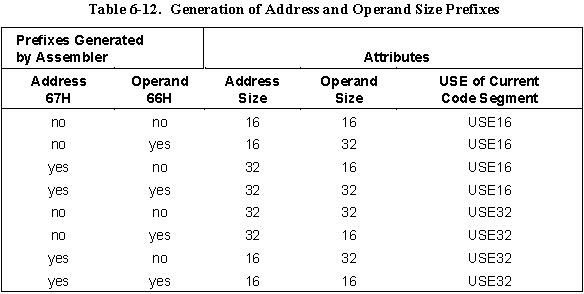

Address size and operand size prefix

67H Address size prefix

66H Operand size prefix

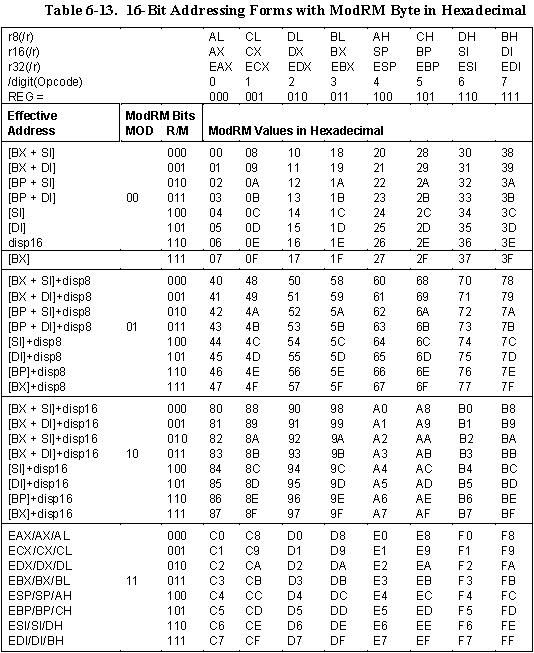

- ModeRM byte

mode: The mod field combines with the r/m field to form 32 possible values representing 8 general registers and 24 indexing modes

reg: The reg field specifies either a register number or three more bits of opcode information, the meaning of the reg field is determined by the first opcode byte of the instruction

r/m: The r/m field can specify a register as the location of an operand, or it can be combined with the mod field to form the addressing-mode encoding

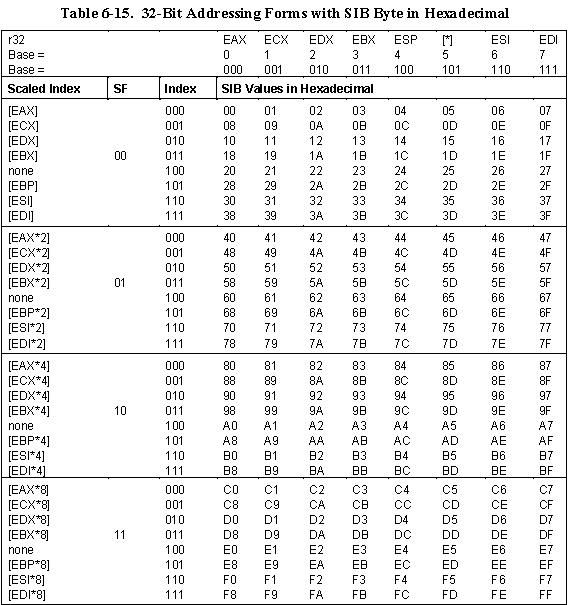

- SIB byte

sf: It specifies the scale factor

index: It specifies the register number of the index register

base: It specifies the register number of the base register