makefile基础和工作常用点补充

一、Makefile简介

定义编译规则、自动化编译、提高效率组织文件

Makefile由一组规则(Rule)组成,每条规则的格式是:

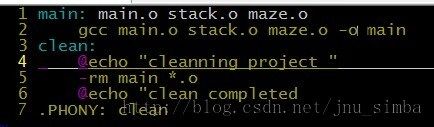

例如:

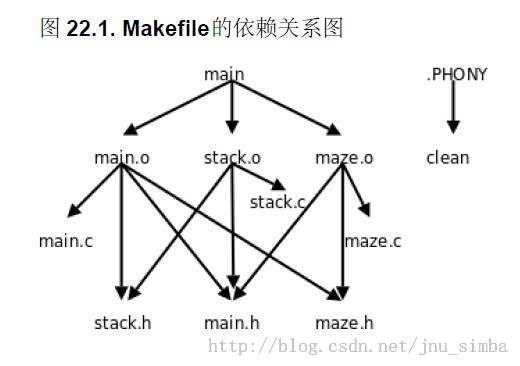

依赖关系如下图:

注意:

(1) 当我们为了执行命令而非创建目标文件时,就会使用伪目标比如 clean,伪目标总是被执行。".PHONY" 的作用是避免和当前

目录下的文件名冲突 (可能引发隐式规则)。

(2) 使用 "-" 前缀可以忽略命令错误,比如创建已有的路径; “@” 可以不显示命令本身

(3) Makefile 中 $、# 有特殊含义,可以进行转义 "\#"、"$$"。

(4) 可以使用 \ 换行 (注释行也可以使用),但其后不能有空格,新行同样必须以 Tab 开头和缩进。

(5) 在工作目录按 "GNUmakefile、makefile、Makefile (推荐)" 顺序查找执行,或 -f 指定。

(6) 如果不在 make 命令行显式指定目标规则名,则默认使用第一个有效规则。

(7) 每条命令都在一个独立 shell 环境中执行,如希望在同一 shell 执行,可以用 ";" 将命令写在一行,也可用\ 换行。

(8) 在makefile 常见的gcc/g++参数 -D 即条件编译; -static 使用静态库;注意 -L../lib -ldown 与 ../lib/libdown.so 等同

二、Makefile基本使用

make规则

没被编译过,则编译;只编译修改过的文件

头文件被改变,只编译包含该头文件的文件

常用选项 : -C dir -f fileName -n 显示待执行的命令,但不执行

Makefile组成

显式规则:生成、依赖文件,生成命令

隐含规则:make支持的自动推导功能, make –p 打印

变量定义:类C中宏作用(?= := +=)。 引用方式 $(var) 或 ${var}。

"=" 递归展开变量,仅在目标展开时才会替换,也就是说它可以引用在后面定义的变量。

":=" 直接展开变量,在定义时就直接展开,它无法后置引用。

"?=" 表示变量为空或未定义时才进行赋值操作。

"+=" 追加赋值,也是递归展开

执行shell命令赋值给变量 A = $(shell uname)

文件包含:include

注释: “#”

特殊变量:

三、Makefile 工作常用点补充

搜索路径

VPATH 变量 VPATH = ./src : ./lib

vpath 关键字( vpath <pattern> <directories> vpath %.h ../ inc )

vpath %.c ./src : ./lib # 定义匹配模式(%匹配任意个字符)和搜索路径。

vpath %.c # 取消该模式

vpath # 取消所有模式

VPATH 和 vpath 定义的搜索路径仅对 makefile 规则有效,对 gcc/g++ 命令行无效,比如不能用它定义命令行头文件搜索路径参数。

变量引用与替换

obj=$(dir:%.c=%.o) 可以将变量 dir 中所有以 c 结尾的单词替换成以 o 结尾

$(addprefix src/, foo bar) 返回值为“src/foo src/bar”

src=$(wildcard *.c ./sub/*.c)

dir=$(notdir $(src))

obj=$(patsubst %.c,%.o,$(dir))

$(^D)

$(^F)

分别表示所有依赖文件的目录部分和文件部分。(无相同的)

自动推导依赖关系

gcc –M main.c自动生成目标文件和源文件的依赖关系; -MM去除系统头文件的依赖关系

maze.d,其内容是 maze.o maze.d:maze.c maze.h main.h