P15协处理器

协处理器寄存器传送(MRC,MCR)

该指令只在条件为真时执行。各种条件在表3-2 中定义了。指令译码如图3-27 所示。

这种指令类型是用于ARM920T 与协处理器直接信息通讯。例如协处理器到ARM920T 的寄存器传输(MRC)

指令在协处理器中的浮点数的FIX,在协处理器中改变浮点数为一个32 位整型,传输结果到ARM920T 寄存器中。

在协处理器中的 ARM920T 寄存器中 32 位数改变为浮点数的 FLOAT 表明 ARM920T 寄存器到协处理器的传输

(MCR)使用。

该指令的重要使用是从协处理器传递控制信息到ARM920T CPSR标志位。例如在协处理器中比较两个浮点数

的结果可以移动到CPSR来控制后续执行流。

31 28 27 24 23 21 20 19 16 15 12 11 8 7 5 4 3 0

Cond 1 1 1 0 CP Opc L CRn Rd Cp# CP 1 CRm

[3:0] 协处理器操作数寄存器

[7:5] 协处理器信息

[11:8] 协处理器标识号

[15:12] ARM 源/目标寄存器

[19:16] 协处理器源/目标寄存器

[20] 加载/存储位

0=存储到协处理器 1=从协处理器加载

[21] 协处理器运行模式

[31:28] 条件字段

协处理器字段

CP#字段用作所有协处理器指令,指定哪个协处理器被调用。

CP Opc,CRn,CP 和CRm字段只用于协处理器,出现在此的解释只是源自协议。当协处理器功能与此不兼

容时容许其他解释。协议解释CP Opc和 CP字段指定对于操作协处理器必须执行,CRn为传输信息的协处理器源

或目标寄存器,CRm为第二个可能由于某种联系依赖指定特殊操作的协处理器寄存器。

传输到 R15

当一个协处理器寄存器传输到 ARM920T 的 R15 作为目标寄存器,传输字的位[31:28]将分别复制到 N,Z,C

和 V标志位。传输字的其它位忽略,传输中PC 和其他CPSR位不会受影响。

从 R15传输

从 ARM920T 的R15作为源寄存器传输到协处理器寄存器,将存储到PC+12。

指令周期时间

执行MRC指令耗时1S+(b+1)I+1C增加周期, 此处S, I和C分别是定义连续周期 (S-cycle), 内部周期 (I-cycle)

和协处理器寄存器传输周期(C-cycle)。执行 MCR指令耗时1S+bI+1C增加周期 b 为协处理器等待忙循环的耗费

周期数。

汇编语法

<MCR|MRC>{cond} p#,<expression1>,Rd,cn,cm{,<expression2>}

MRC 从协处理器移动到 ARM920T 寄存器(L=1)

MCR 从 ARM920T 移动到协处理器寄存器(L=0)

{cond} 两个字符条件助记符,如表 3-2所示。

p# 协处理器必须的独有识别号

<expression1> 放置在 CP Opc字段中的常量表达式

Rd 有效ARM920T 寄存器计算表达式

cn, cm 有效协处理器寄存器计算表达式,分别为 CRn和 CRm

<expression2> 若出现,放置在 CP字段中的常量表达式

例子

MRC p2, 5, R3, C5, C6, ;请求协处理器 2用 c5和c6执行操作数 5,将结果(有符号 32位字)传输回 R3

MRC p6, 0, R4, c5, c6 ;请求协处理器 6用 R4执行操作数 0,将结果放置在 c6

MRCEQ p3, 9, R3, c5, c6 2 ;条件请求协处理器3用c5和c6执行操作数 9(类型 2),将结果传输回 R3

http://my.chinaunix.net/space.php?uid=25520556&do=blog&id=180133

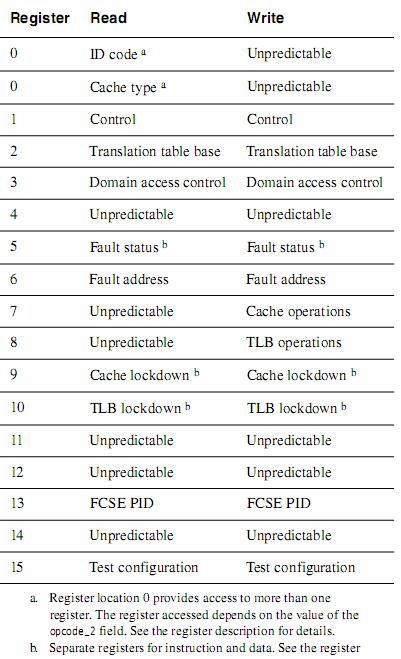

CP15系统控制协处理器

CP15 —系统控制协处理器 (the system control coprocessor)他通过协处理器指令MCR和MRC提供具体的寄存器来配置和控制caches、MMU、保护系统、配置时钟模式(在bootloader时钟初始化用到)

CP15的寄存器只能被MRC和MCR(Move to Coprocessor from ARM Register )指令访问

MCR{cond} p15,<Opcode_1>,<Rd>,<CRn>,<CRm>,<Opcode_2>

MRC{cond} p15,<Opcode_1>,<Rd>,<CRn>,<CRm>,<Opcode_2>

其中L位用来区分MCR(L=1)和MRC(L=0)操作. CP15包括15个具体的寄存器如下:

-R0:ID号寄存器

-R0:缓存类型寄存器

-R1:控制寄存器

-R2:转换表基址寄存器(Translation Table Base --TTB)

-R3:域访问控制寄存器(Domain access control )

-R4:保留

-R5:异常状态寄存器(fault status -FSR)

-R6:异常地址寄存器(fault address -FAR)

-R7:缓存操作寄存器

-R8:TLB操作寄存器

-R9:缓存锁定寄存器

-R10:TLB 锁定寄存器

-R11-12&14:保留

-R13:处理器ID

-R15:测试配置寄存器 2-24

要注意有2个R0,根据MCR操作数的不同传送不同的值,这也一个只读寄存器

-R0:ID号寄存器 这是一个只读寄存器,返回一个32位的设备ID号,具体功能参考ARM各个系列型号的的CP15 Register 0说明.

MRC p15, 0, <Rd>, c0, c0, {0, 3-7} ;returns ID

以下为ID Code详细描叙(ARM926EJ-S); ARM920T Part Number为0x920,Architecture (ARMv4T) 为0x2具体可参照ARM各型号.

-R0:缓存类型寄存器(CACHE TYPE REGISTER),包含了caches的信息。读这个寄存器的方式是通过设置协处理操作码为1.

MRC p15, 0, <Rd>, c0, c0, 1; returns cache details

以下为CP15的一些应用示例

U32 ARM_CP15_DeviceIDRead(void)

{

U32 id;

__asm { MRC P15, 0, id, c0, c0; }

return id;

}

void ARM_CP15_SetPageTableBase(P_U32 TableAddress)

{

__asm { MCR P15, 0, TableAddress, c2, c0, 0; }

}

void ARM_CP15_SetDomainAccessControl(U32 flags)

{

__asm { MCR P15, 0, flags, c3, c0, 0; }

}

void ARM_CP15_ICacheFlush()

{

unsigned long dummy;

__asm { MCR p15, 0, dummy, c7, c5, 0; }

}

void ARM_CP15_DCacheFlush()

{

unsigned long dummy;

__asm { MCR p15, 0, dummy, c7, c6, 0; }

}

void ARM_CP15_CacheFlush()

{

unsigned long dummy;

__asm { MCR p15, 0, dummy, c7, c7, 0; }

}

void ARM_CP15_TLBFlush(void)

{

unsigned long dummy;

__asm { MCR P15, 0, dummy, c8, c7, 0; }

}

void ARM_CP15_ControlRegisterWrite(U32 flags)

{

__asm { MCR P15, 0, flags, c1, c0; }

}

void ARM_CP15_ControlRegisterOR(U32 flag)

{

__asm {

mrc p15,0,r0,c1,c0,0

mov r2,flag

orr r0,r2,r0

mcr p15,0,r0,c1,c0,0

}

}

void ARM_CP15_ControlRegisterAND(U32 flag)

{

__asm {

mrc p15,0,r0,c1,c0,0

mov r2,flag

and r0,r2,r0

mcr p15,0,r0,c1,c0,0

}

}

void ARM_MMU_Init(P_U32 TableAddress)

{

ARM_CP15_TLBFlush();

ARM_CP15_CacheFlush();

ARM_CP15_SetDomainAccessControl(0xFFFFFFFF);

ARM_CP15_SetPageTableBase(TableAddress);

}

void Enable_MMU (void)

{

__asm {

mrc p15,0,r0,c1,c0,0

mov r2, #0x00000001

orr r0,r2,r0

mcr p15,0,r0,c1,c0,0

}

printf("MMU enabled/n");

}

void Disable_MMU (void)

{

__asm {

mrc p15,0,r0,c1,c0,0

mov r2, #0xFFFFFFFE

and r0,r2,r0

mcr p15,0,r0,c1,c0,0

}

printf("MMU disabled/n");

}