quartus PLL 实现 任意分频

1、讲到任意分频,我们就需要借助quartus 强大的硬核 PLL,当然PLL 是模拟电路,是不可能用verilog 或则VHDL 描述出来的,他只是提供给我们一个调用的端口。下面我们就绝缘体实施,任意分频,我们先建立quartus 工程,不再讲解,

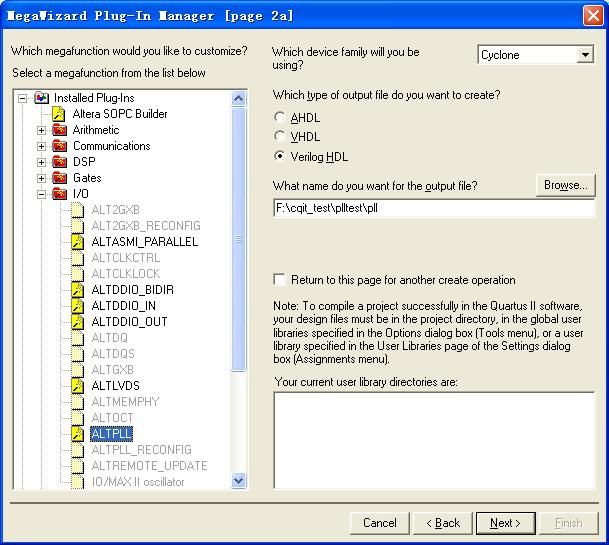

(1)创建一个Megafunction。此在tools--》MegaWizard Plug- In ........,初次建立 选第一项,点Next

(2)创建PLL。注意四点:1.左边要选中IO栏下的"PLL“;2.右上方选择你用的FPGA系列(此处以cylone为例);3.为生成的PLL选择语言,有AHDL,VHDL,Verilog,我一般选的verilog;4.为你的PLL命名,此处为“PLL”,在“F:\FPGA_test\plltest\pll",最后那个pll就是自己写上去的名字

(3),进入PLL定义环节。在上步点NEXT后出现PLL的定义,然后再根据自己需要选择PLL设置,下面我的板子输入时钟是12M,我这里选择为12M,

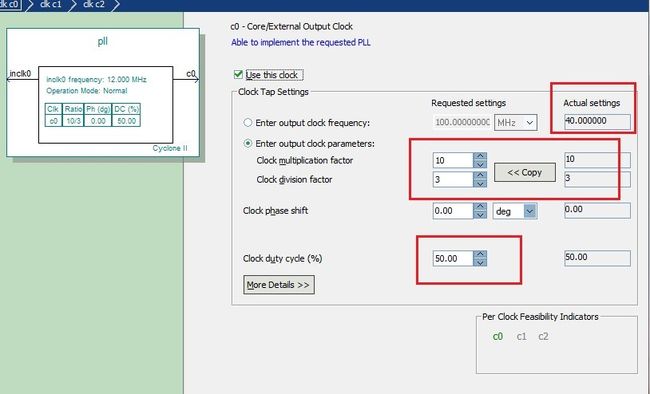

(4)我们去掉红框内部的选择,

(5)这里就是PLL 的关键了, clock mutip....是倍频,clock division.......是分频,我们这里选择不同的数值,他就会输出不同的分频和倍频的数值,注意的是倍频系数最大为10,当然,我是用的飓风2系列的片子,其他系列具体不详。但是都会有个系数上限,和频率上限,如果配置不正确,在编译的时候也会报错的,我这里需要输出一个40M 的频率,就配置10和3 就OK,

(6)本图示没有讲到的设置,为默认设置,点击NEXT 就OK,哈哈!然后就配置完了,下面我们就可以写代码调用它,和测试他了。下面是我的一个测试代码,

意思为用12M 产生一个1s 的信号,利用输出的40M 产生一个1S 的信号,然后再LED 上表现出来,是否一样,当然我们也可以仿真,我这里就用LED 简单的看了下。

module led

(

clk50,

clk12,

reset,

led,led1

);

input clk50,reset,clk12;

output led,led1;

reg [31:0] count,count1,count2;

reg led,led1;

wire clk50,clka,clk12;

wire clk40;

wire clk10;

pll U1

(

.inclk0(clk12),

.c0(clk40)

);

assign clka=clk10;

always @ (posedge clk40 )

begin

count<=count+1;

if(count==40000000)

begin

count<=0;

led<=~led;

end

end

always @ (posedge clk12 )

begin

count1<=count1+1;

if(count1==12000000)

begin

count1<=0;

led1<=~led1;

end

end

endmodule

这里PLL 的端口,为什么是

.inclk0(clk12),

.c0(clk40)

这个问题我们可以打开工程目录下面的PLL.V 一看就明白了!哈哈!!

到这里PLL倍频和分频就讲解完毕