配置vertex-5 XC5VLX220T FPGA, 实现CPU到ax88180和S1R72V17 USB芯片逻辑电路的连通

FPGA的配置工作主要有两部分,连接CPU与AX88180,和连接CPU与S1R72V17。

连接CPU与AX88180

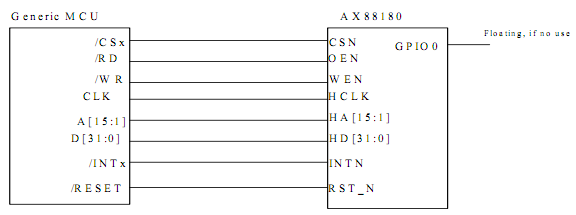

CPU与AX88180的连接可以参考AX88180 datasheet上的附录A,采用32bit数据线连接方式:

主要是32位数据线与CPU DATA线相连,地址线与地址线相连。同样的,分别连接片选,读,写使能,中断和复位线。

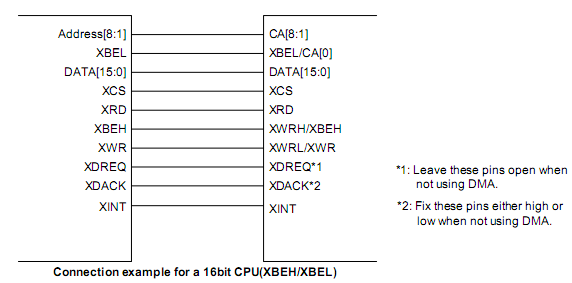

连接CPU与S1R72V17

同样的,连接方式在S1R72V17 datasheet上有参考。 S1R72V17的连接方式很多,有16bit strobe, 16bit XBEH/XBEL模式,8bit 模式。在此我们采用16bit XBEH/XBEL模式,与另外两种模式不同的是连接16bit数据线并且使用高低字节写入信号。连接参考图如下:

对于数据线双向端口的处理

双向端口顾名思义是一种既可以作为输入端口接收数据,也可以作为输出端口发出数据,它对数据的操作是双向的。 比如某个设计需要一个16 位的数据输入口和一个16 位的数据输出口,并且数据输入和输出不会同时发生。 如果数据输入口和输出口分别设计则需要32根数据线,而用双向端口来设计,则只需要16 根数据线,这样就节省了16 根数据 线引脚。

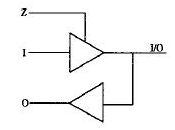

FPGA 中是通过对三态门控制来实现双向端口的,硬件描述图如下:

当z=0 时,上面输出的管子开通,此时数据可以从上面的管子中输出,这时双向端口就作为输出口;当z=1 时,上面的管子被置为高阻态,数据不能从上面的管子输出,此时数据只可以从下面的管子由外向内输入,这时的双向端口是输入口。

对于双向端口的VHDL语言描述实现,主要是要注意给输出信号加上条件判断,同时注意在不输出是给予高阻输入。双向端口的基本形式为:

ENTITY bidir_pin IS ( bidir : INOUT std_logic; oe, clk, from_core : IN std_logic; to_core : OUT std_logic; …… END bidir_pin; ARCHITECTURE behavior OF bidir_pin IS BEGIN bidir <= from_core WHEN oe=‘1’ ELSE “ZZZZ”; to_core <= bidir; END behavior;

首先,在端口申明中要注意申明bidir为 INOUT 类型,bidir输出加入条件信号oe=’1’, 其次非输出条件下高阻输入,最后把端口的输入信号引出为to_core。

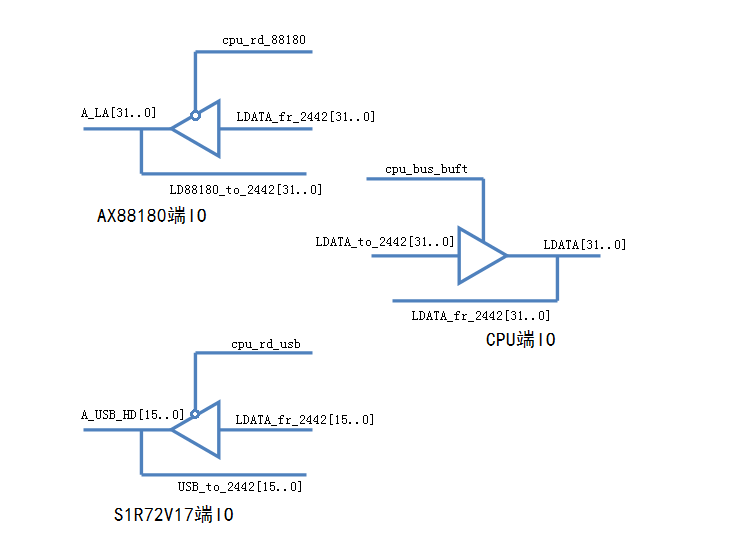

本课题中,为了实现CPU端,AX88180端,S1R72V17端的双端口,需要使用三个使能信号分别控制三个三态门。此处三个使能信号分别为:cpu_bus_buft, cpu_rd_usb,cpu_rd_88180

cpu_rd_usb=0时数据输出到ax88180 IO口否则输入高阻,cpu_bus_buft=1时数据输出到CPU IO,否则为高阻,cpu_rd_usb=0时数据输出到S1R72V17否则为高阻。如下图所示

各控制信号按以下方式形成:

同时,USB_to 2442,LD88180_to_2442两个信号根据片选赋值给LDATA_to_2442。如果片选5选中,则将LD88180输出给LDATA_to_2442, 否则如果片选3选中,则将USB_to_2442输出给LDATA_to_2442,再否则输入高阻。用VHDL语言实现就是:

LDATA_to_2442(31 downto 0) <= LD88180_to_2442(31 downto 0) WHEN LnGCS5='0' ELSE

USB_to_2442(31 downto 0) WHEN LnGCS3='0' ELSE

(others => 'Z');

按此思路,即可写出逻辑电路的VHDL语言描述。

VHDL完整代码如下:

---------------------------------------------------------------------------------- -- Company: NCRL Southeast University -- Engineer: Yuepei Hu -- -- Create Date: 17:13:47 03/21/2011 -- Design Name: UWB_220t -- Module Name: top - Behavioral -- Project Name: 220t -- Target Devices: Vertext-5 XC5VLX220T -- Tool versions: ISE 10.1 -- Description: This Design file is to establish the connection between SC32442 cpu and -- Ax88180 ethernet device and S1R72V17 USB device -- Dependencies: -- -- Revision: 1.0 -- Revision 0.01 - File Created -- Additional Comments: -- ---------------------------------------------------------------------------------- library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity top is Port ( -- AX88180 interface A_CS_88180, A_WE_88180, A_HCLK_88180, A_OE_88180: out STD_LOGIC; A_INT_88180 : in STD_LOGIC; A_LD : inout STD_LOGIC_VECTOR (31 downto 0); A_LA : out STD_LOGIC_VECTOR (15 downto 1); -- 2442 interface LnGCS5, LnGCS3, LnWE, LnOE, nBE0, nBE1: in STD_LOGIC; IRQ_LAN, EINT19: out STD_LOGIC; CLKOUT1: in STD_LOGIC; MAX811_RESET: in STD_LOGIC; RESET: out STD_LOGIC; LDATA: inout STD_LOGIC_VECTOR (31 downto 0); LADDR: in STD_LOGIC_VECTOR (26 downto 0); -- S1R72V17 interface A_USB_HD: inout STD_LOGIC_VECTOR (15 downto 0); A_USB_HA: out STD_LOGIC_VECTOR (8 downto 0); A_USB_INT, A_USB_DREQ: in STD_LOGIC; A_USB_CS, A_USB_RD, A_USB_WRL, A_USB_WRH, A_USB_DACK: out STD_LOGIC; A_USB_BEH: out STD_LOGIC; A_USB_CLKIN: out STD_LOGIC ); end top; architecture Behavioral of top is signal LDATA_fr_2442, LD88180_to_2442, LDATA_to_2442,USB_to_2442: STD_LOGIC_VECTOR (31 downto 0); signal cpu_rd_88180, cpu_bus_buft, cpu_rd_usb: STD_LOGIC; -- cpu_rd_88180='1' when cpu wants to read 88180 -- cpu_rd_usb='1' when cpu wants to read usb -- cpu_bus_buft='1' when cpu read peripheral device begin cpu_rd_88180 <= (NOT LnGCS5) AND LnWE AND (NOT LnOE); cpu_bus_buft <= ((NOT LnGCS5) OR (NOT LnGCS3)) AND LnWE AND (NOT LnOE); cpu_rd_usb <= (NOT LnGCS3) AND LnWE AND (NOT LnOE); LDATA_to_2442(31 downto 0) <= LD88180_to_2442(31 downto 0) WHEN LnGCS5='0' ELSE USB_to_2442(31 downto 0) WHEN LnGCS3='0' ELSE (others => 'Z'); -- Connect AX88180 to SC32442 A_LD(31 downto 0) <= LDATA_fr_2442(31 downto 0) WHEN cpu_rd_88180='0' ELSE (others => 'Z'); LD88180_to_2442(31 downto 0) <= A_LD(31 downto 0); LDATA(31 downto 0) <= LDATA_to_2442(31 downto 0) WHEN cpu_bus_buft='1' ELSE (others => 'Z'); LDATA_fr_2442(31 downto 0) <= LDATA(31 downto 0); A_LA(15 downto 1) <= LADDR(15 downto 1); A_CS_88180 <= LnGCS5; IRQ_LAN <= A_INT_88180; A_WE_88180 <= LnWE; A_HCLK_88180 <= CLKOUT1; A_OE_88180 <= LnOE; RESET<=MAX811_RESET; -- Connect S1R72V17_A to SC32442 A_USB_HD(15 downto 0) <= LDATA_fr_2442(15 downto 0) WHEN cpu_rd_usb='0' ELSE (others => 'Z'); USB_to_2442(15 downto 0) <= A_USB_HD(15 downto 0); USB_to_2442(31 downto 16) <= X"0000"; A_USB_HA(8 downto 1) <= LADDR (8 downto 1); A_USB_HA(0) <= nBE0; A_USB_BEH <= nBE1; A_USB_CLKIN <= '0'; EINT19<=A_USB_INT; A_USB_CS<=LnGCS3; A_USB_RD<=LnOE; A_USB_WRL<=LnWE; A_USB_DACK <= '1'; end Behavioral;

ISE管脚约束参数的设置

完成硬件语言描述只完成了FPGA开发的一半,还需要设置管脚约束参数,即编写UCF文件。

各种参数的功能及语法为:

I/O Name ——IO管脚名称,对应于module里输入输出管脚。

I/O Direction——设定输入(Input)还是输出(Output)管脚。

Loc——位于芯片的位置。

Bank——管脚位于的Bank块,当指定了Loc后,bank也就确定了。

I/O Std.——I/O管脚的电平标准。

每个bank都可以随意设置为该器件支持的电平标准,不同的电平标准在一个bank中要注意它们的电平要一致,比如都为3.3v,电平可以为LVTTL、LVCOMS33。

现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等

UCF文件中IOSTANDARD设定句法为:

INST <I/O_BUFFER_INSTANTIATION_NAME> IOSTANDARD=”<IOSTANDARD VALUE>”;

Drive Str.——I/O管脚的驱动电流。

每一种逻辑电平所支持的驱动电流类别是不同的:LVCOMS12支持2,4,6,8mA 驱动电流,LVCMOS15 和LVCMOS18 支持2,4,6,8,12,和16mA驱动电流。

设定句法:

INST <I/O_BUFFER_INSTANTIATION_NAME> DRIVE = "<DRIVE_VALUE>";

Termination——终端结构(电阻上拉/电阻下拉/悬空)。

PULLDOWN和PULLUP原语

数字电路有三种状态:高电平、低电平、和高阻状态。有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使其处于稳定状态,如图所示。FPGA的I/O端口,可以通过外接电阻上下拉,也可以在芯片内部,通过配置完成上下拉。

上拉电阻是用来解决总线驱动能力不足时提供电流的;

而下拉电阻是用来吸收电流;

Slew——Slew Rate。信号的转换速率,可以理解为信号在某一点的斜率。

它不是只针对时钟信号说的;诸如放大器的slew rate就是一个很重要的参数;而在数字电路里,它可能更常用于描述芯片输入信号的变化率。

在Xilinx的设计环境中,可以将输出信号的Slew rate设置成FAST或SLOW。当设置成FAST时,提高了信号变化的斜率,从而提高了信号的转换速率,但同时使脉冲信号的振铃增大。因此,除非万不得已,不要将输出信号的Slew rate设成FAST。

slew选fast,IO转化时快,但电流大,功耗大。

slew选slow,IO转化慢,但功耗小。

查看器件的DC AC Switching特性手册有详细说明。

设定句法为:

INST <I/O_BUFFER_INSTANTIATION_NAME> SLEW = "<SLEW_VALUE>";

ISE的默认设置为:

IOSTANDARD=LVCMOS25

SLEW=SLOW

DRIVE=12

完整的UCF文件如下:

#for XC5VLX220T-FF1738-1 NET "MAX811_RESET" LOC = "V36" | IOSTANDARD = LVCMOS33; ##clk_tcxo is a 40 MHz external clock source #NET "clk_tcxo" LOC = "AM27" | IOSTANDARD = LVCMOS33; # #NET "clk_tcxo" TNM_NET = "clk_tcxo"; #TIMESPEC "TS_clk_tcxo" = PERIOD "clk_tcxo" 25 ns HIGH 50 %; # ##use DCM_0 to generate an internal clock that is clk_tcxo*5=100 MHz #INST DCM_PS_INST CLK_FEEDBACK = 1X; #INST DCM_PS_INST CLKDV_DIVIDE = 2.0; #INST DCM_PS_INST CLKFX_DIVIDE = 2; #INST DCM_PS_INST CLKFX_MULTIPLY = 5; #INST DCM_PS_INST CLKIN_DIVIDE_BY_2 = FALSE; #INST DCM_PS_INST CLKIN_PERIOD = 25.0; #INST DCM_PS_INST CLKOUT_PHASE_SHIFT = NONE; #INST DCM_PS_INST DCM_AUTOCALIBRATION = TRUE; #INST DCM_PS_INST DCM_PERFORMANCE_MODE = MAX_SPEED; #INST DCM_PS_INST DESKEW_ADJUST = SYSTEM_SYNCHRONOUS; #INST DCM_PS_INST DFS_FREQUENCY_MODE = LOW; #INST DCM_PS_INST DLL_FREQUENCY_MODE = LOW; #INST DCM_PS_INST DUTY_CYCLE_CORRECTION = TRUE; #INST DCM_PS_INST FACTORY_JF = F0F0; #INST DCM_PS_INST PHASE_SHIFT = 0; #INST DCM_PS_INST STARTUP_WAIT = FALSE; #cpu interface NET "CLKOUT1" LOC = "AJ38" | IOSTANDARD = LVCMOS33 | CLOCK_DEDICATED_ROUTE = FALSE; NET "CLKOUT1" TNM_NET = "CLKOUT1"; TIMESPEC "TS_CLKOUT1" = PERIOD "CLKOUT1" 10 ns HIGH 50 %; NET "A_INT_88180" LOC = "U36" | IOSTANDARD = LVCMOS33 | PULLUP; NET "LnGCS5" LOC = "AF31" | IOSTANDARD = LVCMOS18; NET "LnGCS3" LOC = AG34 | IOSTANDARD = LVCMOS18; NET "LnWE" LOC = "AB32" | IOSTANDARD = LVCMOS18; NET "LnOE" LOC = "AB33" | IOSTANDARD = LVCMOS18; NET "nBE0" LOC = "AF36" | IOSTANDARD = LVCMOS18; NET "nBE1" LOC = "AF32" | IOSTANDARD = LVCMOS18; #NET "LADDR[16]" LOC = "AM36" | IOSTANDARD = LVCMOS18; NET "LADDR[15]" LOC = "AK34" | IOSTANDARD = LVCMOS18; NET "LADDR[14]" LOC = "AJ35" | IOSTANDARD = LVCMOS18; NET "LADDR[13]" LOC = "AJ31" | IOSTANDARD = LVCMOS18; NET "LADDR[12]" LOC = "AK33" | IOSTANDARD = LVCMOS18; NET "LADDR[11]" LOC = "AH34" | IOSTANDARD = LVCMOS18; NET "LADDR[10]" LOC = "AH31" | IOSTANDARD = LVCMOS18; NET "LADDR[9]" LOC = "AJ33" | IOSTANDARD = LVCMOS18; NET "LADDR[8]" LOC = "AM31" | IOSTANDARD = LVCMOS18; NET "LADDR[7]" LOC = "AH33" | IOSTANDARD = LVCMOS18; NET "LADDR[6]" LOC = "AL31" | IOSTANDARD = LVCMOS18; NET "LADDR[5]" LOC = "AM32" | IOSTANDARD = LVCMOS18; NET "LADDR[4]" LOC = "AK32" | IOSTANDARD = LVCMOS18; NET "LADDR[3]" LOC = "AM33" | IOSTANDARD = LVCMOS18; NET "LADDR[2]" LOC = "AJ32" | IOSTANDARD = LVCMOS18; NET "LADDR[1]" LOC = "AL32" | IOSTANDARD = LVCMOS18; NET "LDATA[31]" LOC = "AV34" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[30]" LOC = "AV39" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[29]" LOC = "AU37" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[28]" LOC = "AV38" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[27]" LOC = "AV35" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[26]" LOC = "AV31" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[25]" LOC = "AV36" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[24]" LOC = "AU32" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[23]" LOC = "AV33" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[22]" LOC = "AU38" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[21]" LOC = "AU31" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[20]" LOC = "AU34" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[19]" LOC = "AT35" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[18]" LOC = "AU33" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[17]" LOC = "AT37" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[16]" LOC = "AP36" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[15]" LOC = "AT36" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[14]" LOC = "AR37" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[13]" LOC = "AR38" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[12]" LOC = "AP37" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[11]" LOC = "AR35" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[10]" LOC = "AP35" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[9]" LOC = "AN35" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[8]" LOC = "AR34" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[7]" LOC = "AN34" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[6]" LOC = "AN33" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[5]" LOC = "AP33" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[4]" LOC = "AP31" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[3]" LOC = "AR32" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[2]" LOC = "AN31" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[1]" LOC = "AR33" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "LDATA[0]" LOC = "AP32" | IOSTANDARD = LVCMOS18 | DRIVE = 2 | SLEW = "FAST"; NET "RESET" LOC = "Y32" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_HCLK_88180" LOC = "T36" | IOSTANDARD = LVCMOS33 | DRIVE = 12 | SLEW = "FAST"; NET "IRQ_LAN" LOC = "AE37" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST";#connected to EINT9 of ARM CPU NET "A_LA[15]" LOC = "H34" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[14]" LOC = "H33" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[13]" LOC = "H31" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[12]" LOC = "G34" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[11]" LOC = "G33" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[10]" LOC = "G32" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[9]" LOC = "G31" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[8]" LOC = "F35" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[7]" LOC = "F34" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[6]" LOC = "F32" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[5]" LOC = "F31" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[4]" LOC = "E35" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[3]" LOC = "E34" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[2]" LOC = "E33" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LA[1]" LOC = "E32" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[31]" LOC = "N35" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[30]" LOC = "R34" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[29]" LOC = "M36" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[28]" LOC = "P35" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[27]" LOC = "L37" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[26]" LOC = "M37" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[25]" LOC = "N36" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[24]" LOC = "P36" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[23]" LOC = "K35" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[22]" LOC = "L35" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[21]" LOC = "L36" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[20]" LOC = "H35" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[19]" LOC = "J35" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[18]" LOC = "J36" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[17]" LOC = "K37" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[16]" LOC = "G37" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[15]" LOC = "F36" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[14]" LOC = "J37" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[13]" LOC = "H36" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[12]" LOC = "G36" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[11]" LOC = "E38" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[10]" LOC = "E37" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[9]" LOC = "F37" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[8]" LOC = "V35" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[7]" LOC = "D37" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[6]" LOC = "V34" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[5]" LOC = "V33" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[4]" LOC = "Y33" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[3]" LOC = "W33" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[2]" LOC = "U34" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[1]" LOC = "W32" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_LD[0]" LOC = "T35" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_CS_88180" LOC = "T34" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_OE_88180" LOC = "U33" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_WE_88180" LOC = "R35" | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_USB_CS" LOC = L12 | IOSTANDARD = LVCMOS33; NET "A_USB_HA<0>" LOC = H15 | IOSTANDARD = LVCMOS33; NET "A_USB_HA<1>" LOC = H14 | IOSTANDARD = LVCMOS33; NET "A_USB_HA<2>" LOC = H13 | IOSTANDARD = LVCMOS33; NET "A_USB_HA<3>" LOC = J13 | IOSTANDARD = LVCMOS33; NET "A_USB_HA<4>" LOC = J12 | IOSTANDARD = LVCMOS33; NET "A_USB_HA<5>" LOC = J11 | IOSTANDARD = LVCMOS33; NET "A_USB_HA<6>" LOC = H11 | IOSTANDARD = LVCMOS33; NET "A_USB_HA<7>" LOC = J10 | IOSTANDARD = LVCMOS33; NET "A_USB_HA<8>" LOC = H10 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<0>" LOC = F10 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<1>" LOC = E10 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<2>" LOC = G11 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<3>" LOC = F11 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<4>" LOC = G12 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<5>" LOC = F12 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<6>" LOC = E12 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<7>" LOC = D12 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<8>" LOC = G13 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<9>" LOC = E13 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<10>" LOC = D13 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<11>" LOC = G14 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<12>" LOC = F14 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<13>" LOC = E14 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<14>" LOC = F15 | IOSTANDARD = LVCMOS33; NET "A_USB_HD<15>" LOC = E15 | IOSTANDARD = LVCMOS33; NET "A_USB_INT" LOC = L11 | IOSTANDARD = LVCMOS33 | PULLUP; NET "A_USB_RD" LOC = K12 | IOSTANDARD = LVCMOS33; #NET "A_USB_WRH" LOC = K13 | IOSTANDARD = LVCMOS33 | DRIVE = 2 | SLEW = "FAST"; NET "A_USB_BEH" LOC = K13 | IOSTANDARD = LVCMOS33; NET "A_USB_WRL" LOC = K14 | IOSTANDARD = LVCMOS33; NET "EINT19" LOC = AP40 | IOSTANDARD = LVCMOS33; NET "A_USB_DACK" LOC = K10 | IOSTANDARD = LVCMOS33 | PULLUP; NET "A_USB_CLKIN" LOC = M11 | IOSTANDARD = LVCMOS33;