http://tech.c114.net/167/a693120.html

电视机的发展在过去15年来进步神速。诸如液晶显示器(LCD)和电浆显示器(plasma)等平面面板技术的出现,让冷阴极管和背投影产品逐渐消失。屏幕尺寸快速增加而厚度却越来越薄,让电视机变成可以挂在墙上欣赏的艺术品。然而,不只是我们从外观上可以观察到的屏幕构造产生变化,内部的影像接口也不断在改变。模拟已经被数字所取代,为使用者带来一种难以匹敌的观赏经验。

当然,就跟每种新兴技术一样,消费者的需求迟早会超过系统能达到的性能。当影像格式和屏幕尺寸变大时,用来支持它们的频宽也必须随之增加。这就在现有的设计上增加了新的需求,一种越来越难满足的需求。

TranSwitch推出HDwire进入这个具挑战性的市场。以荣获许多一级多媒体产品采用的先进智能财产权(IP)高速接口核心和集成电路(IC)闻名的TranSwitch,以突破电视机中的频宽瓶颈为目标而研发了HDwire.

但是在我们探究这项最新的技术发展之前,让我们先快速浏览一下我们到达目前发展程度的方式及原因。

电视技术的演进

约翰洛吉贝尔德(John Logie Baird) 在1925年首次展示行动影像的传输,这个突破性的进展被公认为是电视的首次真正展示。后续的几十年间,这个系统无疑地有许多更精细的改进,包括广播方式的进步,但电视的基础仍然相同:接收一个模拟讯号然后显示在玻璃屏幕上。彩色取代了黑白、背投影产品补足了冷阴极管(CRT)的不足、缆线和卫星变成传输的媒介,但是最终电视还是一台模拟的显示器。

所有的一切在1990年代中期全世界第一台高分辨率平面电视出现之后发生了变化。使用电浆技术的新电视,厚度只有CRT的一小部分。紧接着很快出现新的接口技术,例如数字影像接口(DVI)和高分辨率多媒体界面(HDMI),这些都预告了模拟电视转变成数字电视的趋势。

然而,这只是个开端。HDMI让播放格式尺寸不断增加的高分辨率影像可以在我们的家用娱乐系统上显示。对频宽的要求开始增加,现有电视构造的限制开始越加明显。

平面电视构造

如果我们简单看看平面电视的主要零件,将会发现:

- 显示面板 (电浆、液晶显示器、有机发光二极管)

- 时序控制器(Tcon)板,用来驱动面板

- 影像处理器板,上面有系统单芯片(SoC)IC.负责把自讯号源接收进来的信息流转换成Tcon的正确格式。

- 电源供应模块

图1:一般平面电视拆解图

当平面电视的尺寸还很小的时候,SoC和Tcon可以固定在同一块印刷电路板(PCB)上。不过,当屏幕尺寸增加之后,继续用一块大型的PCB就变得太昂贵(也太重),因而逐渐形成两块板子的解决方案。

当SoC和Tcon放在不同的PCB之后,就需要一种相互连接的技术来传输他们之间的讯号,在1990年代中期,电视制造商采用LVDS接口技术做为实际上的标准。

LVDS技术

LVDS(低电压差分信号)是由国家半导体在1990年代初所研发的,于1996年首次使用在电视机中。16年后,它仍然是此项应用的主导技术。这项技术的真实名称实际上是平面显示器连结(FPD-Link),但是因为它是LVDS的第一个大型应用,因此很多工程师将FPF-Link和LVDS做为同义词使用。

LVDS被定义在ANSI/TIA/EIA-644-A标准中,这是由数据传输接口委员会TR30.2于1995

年发展的标准。它是低电压、低功率的差分技术,主要使用在点对点和多点连接的接线驱动应用。此标准建议最大数据率655 Mbps,但最近推出的高速LVDS的限制已增加到大约1.2Gbps.

LVDS是设计为每个时脉可驱动7 个资料位。每5条资料信道就需要一条单独的时钟信道,而这就表示要增加大约16%的缆线固定成本。

LVDS及其扩充性

LVDS已经在业界盛行多年,近来分辨率和播放格式的进展已经导致频宽增加不少。具有60Hz和120Hz更新频率的电视已经在商店内贩售,2012年的CES展甚至还陈列了4Kx2K的电视。因此,用来支持这些频宽的LVDS线路的数目已增加颇多,导致电视制造商增加更多生产上的成本和复杂性。

随着市场预估有较高更新频率的电视出货数目会稳定成长,LVDS的限制将变得更加明显。成本压力和工程限制将会迫使电视制造商寻求替代的解决方案。

图2:60/120/240Hz电视出货预估

HDwire-取代LVDS的终极方案

TranSwitch所研发的HDwire提供了一个可替代LVDS 的先进方案。HDwire使用进阶的信

号技术,可以用低价且简单的扁平电缆取代多条LVDS缆线。这项技术预计能以少量线材和更简易的系统设计简化面板的相互连接方式。

HDwire接口可包含多达12条、每一条可支持5.0Gpbs的顺向信息信道,和可支持1.25/2.50Gpbs的可选用的反向数据信道。这个接口可以支持每个色彩12位、分辨率4K x 2K、更新频率120Hz(53.5Gpbs),以及每个色彩12位、分辨率8K x 4K、更新频率30Hz(53.5Gpbs)的显示面板。HDwire提供比其它技术更低的EMI,因此不只简化系统设计还能降低成本。HDwire被设计为可透过FR4 FPCB、FFC软排线和现有的标准缆线,在使用最低功耗、低位错误率(BER)的情况下即可让超高速影像运作。

图3:HDwire系统应用

当我们拿HDwireTM和LVDS解决方案相比,只需要一半频宽(1080p、240Hz、 12位色彩产出、26.7Gbps)的HDwireTM接口,其简单及具成本效益的优势就变得更明显了。

图4:针对1080p/240Hz电视(SoC板附画面频率变频器)的LVDS解决方案

HDwireTM有一项比LVDS更佳的优势,它的连结包括一条高速反向频道,可以自Tcon板将数据传送到SoC板。一般这个功能是透过使用I2C执行,但是这个通讯协议的频宽量有限,每秒只有数个兆位。HDwireTM采用的反向信道是以和顺向信息信道相同的技术为基础,数据传输速率可达到1.25/2.5Gbps.这个高速反向连结有许多用处,例如可以用来将电视前框上的照相机连接到应用处理器,可以让整体视讯会议的流程更顺畅。触控面板的资料也可以透过反向信道传送,让使用这种新兴功能变的更简单。

使用更便宜的缆线

HDwire技术的关键优势之一就是它可以透过低成本的缆线完成高速的信号传输。排除对高成本LVDS排线的需求,使得HDwire解决方案省下不少成本。TranSwitch的技术展示是使用软排线(FFC)作为高速媒介,HDwire的设计可以透过这种最长达1公尺的简单线材运作。FFC和线材端子的相加成本比具备相同效用的LVDS成本要低很多,不需要降低任何最新款屏幕必备的高分辨率画质就能轻易省下这些成本。

维持低功耗

随着消费者的环保意识日渐增加,电视的消耗功率现在也变成前所未见的热门话题。屏幕尺寸的增加,加上实际的显示技术,意味着现在购买新电视时,屏幕的消耗功率变成一个重要的考量因素。能源之星(Energy Star)在他们最近将于2012年5月发表的规格中(版本5.0),将32吋电视的开机时最大功率限制为55W,而50吋电视则是108W(相较之下,版本3.0的数字高达120W和353W)。这表示在分配系统的功率限额时,电视中的每个电路都会受到严密的检查。

幸好,HDwire技术的功率消耗本来就很低。此设计使用预驱动器,以比不归零编码(NRZ)还低的频率运作,可减少讯号源的功率消耗。这会帮助减少二重像和缆线辐射。此外,采用的讯号传输方法是使用多重讯号层,多数讯号是在低于完全电压的层产生的。这也更加降低了系统的功率消耗。

反向信息信道

除了顺向数据频道之外,HDwire还整合了反向数据信道,可将数据从面板传送到SoC.此信道可以1.25/2.50Gbps的速度运作,是将整合在电视面框上的相机连接到应用处理器的理

想导管。这个反向信道比目前大多数电视使用的独立I2C连结更具优势,因为它的速度远远超过一个I2C连结可提供的少量的Mbps.此外,因为它是和现有的设计和缆线整合在一起

,因此反向信道可节省额外成本并降低复杂度。

EMI优势

除了HDwire单纯功能上的优点之外,这项技术在电磁干扰(EMI)的也大大的改善。EMI是双绞线发射出来的辐射电场。它是因为生产缆线时的小瑕疵所造成的,却会对电视设计者造成大问题。发射出的干扰会造成电视机内部的电路以及邻近的电器受到干涉。因此,降低EMI成为CE产品的关键要求也就不令人意外了。

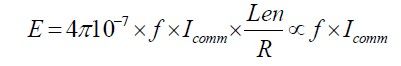

一条双绞线共享讯号发射出的辐射电场强度可以下列公式表示:

E =从距离线材R的位置测出的电场强度[V/m]

f = 共享电流零件的正弦波频率[Hz]

Icomm = 共享电流[A]

Len = 散发辐射的双绞线长度[m]

R =从线材到电场量测位置的距离[m]

因为线材不是完美的(例如,差分对内延迟差),差动发射讯号造成共享讯号(SCD11)。差动发射漏电至到共享讯号,可以透过散射参数SCD11, SCD22 , SCD21 和 SCD12量测出来。根据前述公式,共模讯号辐射成为共模讯号的EMI.共模讯号的EMI比差模讯号的EMI更强,在EMI量测中更加重要。

HDwireTM使用先进的信号传输技术,和其它技术使用的不归零编码(NRZ)相比,EMI可大幅降低。分析显示,和NRZ相比,EMI辐射可降低约5.5dB,降低对抑制EMI技术的需求,也可以帮助简化电视设计。EMI辐射和发射器频谱及频宽具有等比例的关系,HDwireTM的EMI表现改善可以归因为以下几项重要因素:

- 信号传输频宽比NRZ少

- 功率强度比NRZ低

- 升/降时间比NRZ慢

下图说明EMI的改善成果

图5:HDwire EMI表现与NRZ EMI表现之比较

为了判定EMI成果,首先必须要使用网络分析仪量测一般双绞线的S参数。这个S参数会使用在Matlab的仿真中,以决定产生共模EMI的差模-共模讯号的效用。从上图中可看出结果显示HDwire信号传输在关键的2.5GHz-3.5GHz频率产生非常少的EMI.

HDwire成本优势

HDwire优于LVDS的技术优势已经在前述文章中详加讨论过了。不过,许多电视制造商感兴趣的是转换到这项新技术可省下的成本。下图显示出一台4Kx2K电视的HDwire和LVDS的一般生产成本的比较。

图6:使用HDwire的4K电视系统的节省成本

确切减少的成本无疑地是取决于许多变量(例如数量),但是上述图标可用来说明哪些部份可省下成本。使用HDwire桥接IC结合现有的SoC和Tcon芯片可以减少多达一半的零件成本。 不过,当个别整合HDwire发射器和接收器IP(智能财产权)核心在SoC和Tcon时,可能省下的成本会大大地增加。

HDwire特色功能列表

下图是HDwire桥接IC技术的部份关键特色(图标为接收器):

- 整合6条顺向信息信道(可扩充至12条),每条信道传输率5Gbps,以及1条反向信息信道

- 支持最大达100cm的FPCB,BER低于10-12

- 符合显示面板的大范围像素时脉

- 支持60Hz、120Hz和240Hz的面板更新频率

- 异步HDwire输入和4信道LVDS输出- 虚拟随机模式产生电路(PRBS)

- 支持低摆幅LVDS以降低EMI和功耗- 整合8051 MCU和RAM及ROM- 功率下降模式

图7: HDwire电路图及特色表

HDwire系统

下图8说明一般的HDwire系统,显示如何将HDwire桥接IC整合到现有的板子设计中以支持此新接口。

图8: 一般使用桥接IC的HDwire系统

TranSwitch的HDwire产品也可以透过智能财产权(IP)核心的方式提供。让SoC和Tcon厂商可以将此新技术整合到他们的IC中,代表这些装置可以供应给内含HDwire的电视/面板制造商。如此的整合方式带来的成本优势及附加价值对生产商将会非常有益。

竞争力分析

既然已知LVDS的限制,那么出现其它与LVDS竞争的技术也就不足为奇了。以下是作者写作本文时为作者所知的可替代LVDS的技术:

‐ HDwire

‐ V‐by‐One / V‐by‐One HS

‐ eDP

‐ iDP

V-by-One / V-by-One HS

V-by-One是由Thine电子公司研发的技术,用以取代LVDS.虽然目前V-by-One的市场占有率还很小,但是已经有一些电视制造商转换到这个相对新的技术。LG是其中一个制造商,他们在2011年宣布改用V-by-One.

Thine意识到显示器格式需要更大的频宽,在2011年12月发表V-by-One 的1.4版 V-by-One HS.此规格的HS版本支持最高4Gbps数据传输率(有效传输率3.2Gbps)。

这项技术的关键特色如下:

·可扩充顺向资料和时脉的Serdes组(序列器/解除序列器)数量,目前IC支持2条顺向信道。

·支持最高4K x 2K、更新频率240Hz、每个色彩12位(使用于多个IC上的32条信道)

·嵌入式时脉,接收器不再需要参考时脉。

eDP

嵌入式DisplayPort(eDP)是VESA推出的以DisplayPort标准为基础的技术,用以取代LVDS.1.0版本于2008年12月推出,2011年2月发表1.3版本。eDP似乎是在笔电市场较有进展,在电视领域好象不太成功。

这项技术的关键特色如下:

·支持最高顺向信道的4组Serdes及时脉,每组传输速率5.4Gbps(有效数据传输率为每组4.3Gbps)。

·有1条做为控制功能使用的1Mbps的回传信道

·目前支持的最大面板分辨率为8位4Kx2K@60Hz.

iDP

iDP(内部DisplayPort)是另一个VESA标准,此规格的版本1于2010年4月发表,用以取代LVDS.此技术是以简化的DP通讯协议为基础。

iDP的关键特色如下:

·每条信道数据传输率固定为3.24Gbps

·没有AUX信道

·嵌入式时脉(8B10B编码)

·弹性频宽(每数据库最多16组,可超过1个数据库)

·根据VESA网站资料显示,iDP是以大型屏幕显示器内的连接为目标,而eDP则是针对笔记型计算机的GFx和面板间的连接。

自从iDP标准在2010年第一次发表之后,就没有其它新版本继续发表。而且ST Micro网站上和iDP有关的最新新闻发布是2010年11月(LVDS-iDP Bridge ICs)。因此,这项技术看来似乎是已经暂停了。

下列表为和LVDS相关的每项技术的比较表

表:面板互相连接之技术比较

HDwire的每个IC总计有30Gbps的原始频宽(多芯片结构可扩充至60Gbps),提供比其它任何竞争者更多的产量。在同类型技术中,反向影像资料信道是一个独特的特色,让HDwire增添更多产品价值。使用嵌入式时脉,不需要在接收器中使用振动器,所有缆线中的排线都用来传输资料,因此可减低传输的固定成本并简化接收器时脉结构。

TranSwitch HDwire产品线

为了要满足面板连接的不同选择,TranSwitch研发了一系列的HDwire产品以符合CE产业的需求:

-HDwire发射器桥接IC,用于SoC板

-HDwire接收器桥接IC,用于Tcon板

-HDwire发射器IP核心,用于整合SoC IC

-HDwire接收器IP核心,用于整合Tcon IC

上述每项产品都提供相同的基本功能,也就是:

-支持多达6条顺向信息信道(可扩充至12条),每一条信道有5Gbps的原始数据传输率

-单一反向数据传输,传输率1.25/2.50Gbps.

-低EMI辐射

-支持FR4 PCB、FFC软排线和现有的标准线材

HDwire技术展示

TranSwitch在2012年CES展出他们的解决方案,也可以透过预约的方式于公司位于以色列的研发中心体验这项新技术。展示是使用TSMC 65nm制程的HDwireTM模拟测试芯片和Xillinx FPGAs数字设计,可透过单一条8线的FFC缆线运作4个1080p-60Hz影像输入源。此设定等同于4Kx2K-60Hz位率的显示器,足以说明HDwire可以轻松为下一世代的电视降低成本和复杂性。

图9:HDwire技术展示

总结

随着更高分辨率的电视和播放格式的推出,对于可取代LVDS的需求已明显增加。这些播放格式所需要的频宽表示需要多条LVDS排线,因而增加了电视的生产成本。目前市场上有不少互相连接技术,但TranSwitch的HDwire解决方案提供无可匹敌的位率,结合了具附加价值的特色和杰出的EMI表现。HDwire可以透过单一低价缆线运作,是真正能取代LVDS的终极解决方案。

![HDwire取代LVDS技术详释[图]_第1张图片](http://img.e-com-net.com/image/info5/766bbe86e9b14872844b22dd523890c0.jpg)

![HDwire取代LVDS技术详释[图]_第2张图片](http://img.e-com-net.com/image/info5/d395eca0a63745849d50cb382796b164.jpg)

![HDwire取代LVDS技术详释[图]_第3张图片](http://img.e-com-net.com/image/info5/994093cd32164808a927ce0ddcf21a76.jpg)

![HDwire取代LVDS技术详释[图]_第4张图片](http://img.e-com-net.com/image/info5/036ba6b68fcc4ab18c9e3f023ca4c7cd.jpg)

![HDwire取代LVDS技术详释[图]_第5张图片](http://img.e-com-net.com/image/info5/181966d7adfd4a81b2e8808b9afd360c.jpg)

![HDwire取代LVDS技术详释[图]_第6张图片](http://img.e-com-net.com/image/info5/f23fe890159f4530b9ebaa085eebc269.jpg)

![HDwire取代LVDS技术详释[图]_第7张图片](http://img.e-com-net.com/image/info5/bc1d23b06bba4250aaa0bf9ddeac4a37.jpg)

![HDwire取代LVDS技术详释[图]_第8张图片](http://img.e-com-net.com/image/info5/ee458fea13fe4103ac6d082b018f1545.jpg)