【MSP430】MSP430深入研究 之 时钟

称之为混合信号处理器,是由于其针对实际应用需求,将多个不同功能的模拟电路、数字电路模块和微处理器集成在一个芯片上,以提供“单片机”解决方案。该系列单片机多应用于需要电池供电的便携式仪器仪表中。

——摘自百度百科

MSP430说起使用的时间,也有1年半了,之前都是看着别人的代码,看看datasheet的研究的很肤浅。现在有点时间,就花一段时间来把msp430重新研究下!这次会设计到msp430的每个模块的每个寄存器!今天就先从时钟开始!毕竟你想让MCU运行起来嘛!

figure1. system clock

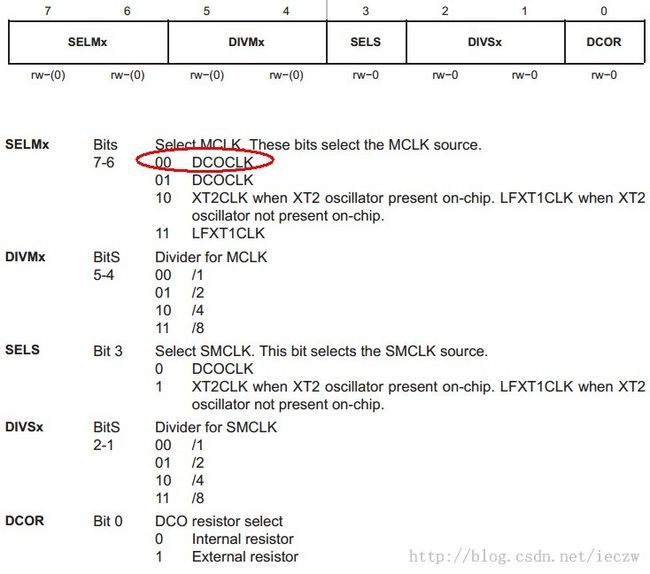

首先明确一点,让MCU运转的是MCLK(Main System Clock),从figure1上可以看出有三路,一路来自于XT1,另一路来自XT2,第三路来自DCOCLK,至于具体选哪路,我们就要配置BCSCTL2(Basic Clock System Control)

figure 2. Register of BCSCTL2(Basic Clock System Control )

如果你现在还在疑问有些书上说的默认MCLK = 1M,原因是默认选择的是DCOCLK,DCOCLK是msp430内部集成的数控晶振,默认为1M,最高可以配置成10M,这个我们后面再说!我们通常选择的是XT2高速时钟,稳定期间如果是msp430f14x的话,建议选择的时候再450K~8M直接,这属于稳定的范围!

所以我们的配置如下:BCSCTL2 |= SELM1;

这时候只是配置了主时钟(MCLK),但是我们经常在外设中要用到SMCLK,或者是ACLK;

ACLK的时钟源为XT1,一般都是接的32768Hz的晶振,我们也可以对他进行1/2/4/8分频;

SMCLK有两个时钟源,一个是DCOCLK,另一个是XT2,至于具体想选哪个那就看你自己了,具体配置在BCSCTL2,默认是选择DCOCLK;

使用DCOCLK缺点是不是很稳定,优点是输出频率可调,当我们在用到可变频率的时候我们就可以使用DCOCLK!

选择XT2就这样配置:BCSCTL2 |= SELS;//默认为8M的输出,当然我们也可以进行1/2/4/8分频;

DCOCLK研究

DCOCTL是一个8位的DCO控制寄存器。该寄存器的位分配图如figure3。

figure 3. Register of DCOCTL(Digital Colck Output Control)

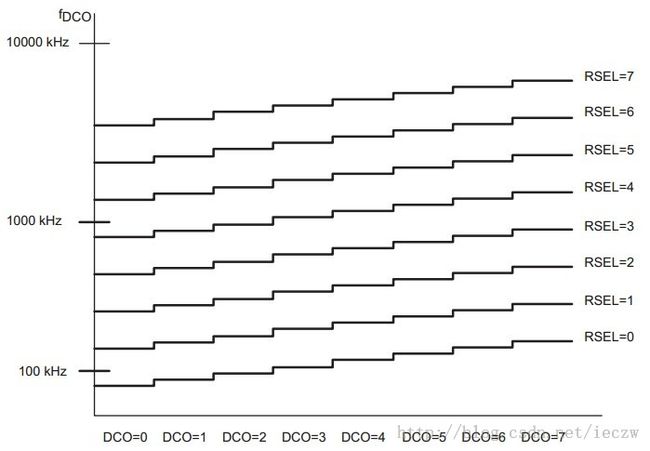

其中DCOx选择内部DCO产生的8中频率之一,可分段条件DCOCLK频率,相邻两个频率相差10%,而频率由注入直流发生器的电流定义。

MODx定义32个DCO周期中插入的频率等于Fdco+1周期的个数。如果DCO常数为7,表示已经选择最高频率,此时不能利用MODx进行频率调整。

figure 4. DCOx & RSELx for frequency

实例代码:

#include <msp430x14x.h>

void init_sysclk()

{

unsigned char i = 0;

// XT2 默认是关闭的,为了方便多次修改时钟

// 这里我们把他加上

BCSCTL1 &= ~XT2OFF;

// MCLK 默认是选择 DCOCLK

// 所以我们要选择 XT2

BCSCTL2 |= SELM1;

// SMCLK 默认也是选择 DCOCLK

// 这里我也让他以 XT2 为时钟源

BCSCTL2 |= SELS;

// 这样,SMCLK,MCLK的时钟的输出都是8MHz了

do{

// 清除时钟震荡错误标志

// 由于修改了MCLK的时钟源

// 需要等待输出时钟与XT2同步

IFG1 &= ~OFIFG;

// 延时一下

for(i=0; i<100; i++)

_NOP();

}while((IFG1 & OFIFG) != 0);

// 当晶振出错标志位为0,则说明已经矫正完成

// 可以正常工作了

IFG1 &= ~OFIFG;

}

#define SMCLK_DIV1 0x00

#define SMCLK_DIV2 0x02

#define SMCLK_DIV4 0x04

#define SMCLK_DIV8 0x06

#define MCLK_DIV1 0x00

#define MCLK_DIV2 0x10

#define MCLK_DIV4 0x20

#define MCLK_DIV8 0x30

void mclk_div(unsigned char div)

{

// 设置分频

BCSCTL2 |= div;

// 重新初始化一下

init_sysclk();

}

void smclk_div(unsigned char div)

{

// 设置分频

BCSCTL2 |= div;

// 重新初始化一下

init_sysclk();

}

请大家多多指导!