FPGA静态时序分析——IO口时序(Input Delay /output Delay)

转载地址:http://www.cnblogs.com/linjie-swust/archive/2012/03/01/FPGA.html

1.1 概述

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

1.2 FPGA整体概念

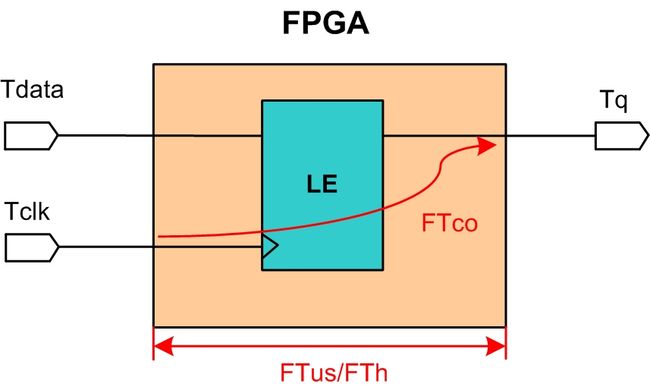

由于IO口时序约束分析是针对于电路板整个系统进行时序分析,所以FPGA需要作为一个整体分析,其中包括FPGA的建立时间、保持时间以及传输延时。传统的建立时间、保持时间以及传输延时都是针对寄存器形式的分析。但是针对整个系统FPGA的建立时间保持时间可以简化。

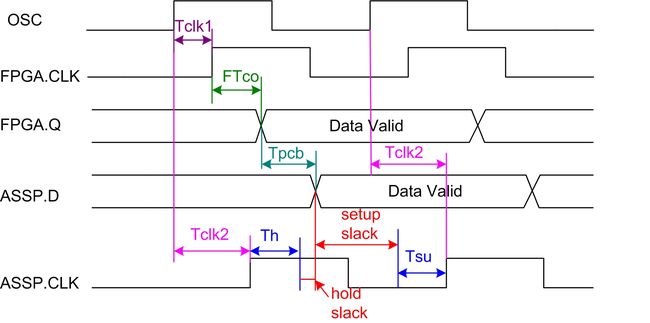

图1.1 FPGA整体时序图

如图1.1所示,为分解的FPGA内部寄存器的性能参数:

(1) Tdin为从FPGA的IO口到FPGA内部寄存器输入端的延时;

(2) Tclk为从FPGA的IO口到FPGA内部寄存器时钟端的延时;

(3) Tus/Th为FPGA内部寄存器的建立时间和保持时间;

(4) Tco为FPGA内部寄存器传输时间;

(5) Tout为从FPGA寄存器输出到IO口输出的延时;

对于整个FPGA系统分析,可以重新定义这些参数:FPGA建立时间可以定义为:

(1) FPGA建立时间:FTsu = Tdin + Tsu – Tclk;

(2) FPGA保持时间:FTh = Th + Tclk;

(3) FPGA数据传输时间:FTco = Tclk + Tco + Tout;

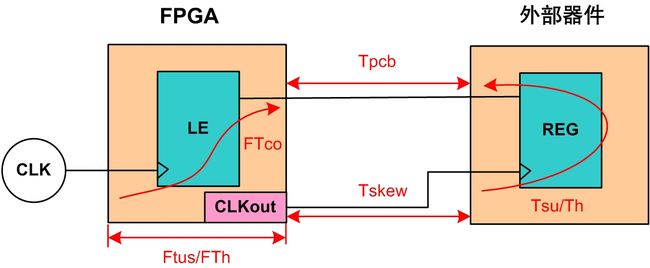

由上分析当FPGA成为一个系统后即可进行IO时序分析了。FPGA模型变为如图1.2所示。

图1.2 FPGA系统参数

1.3 输入最大最小延时

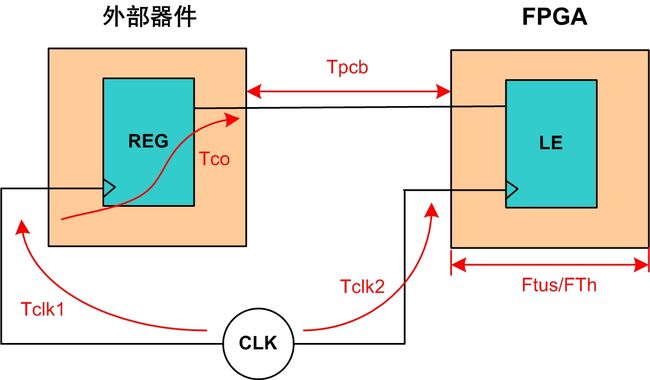

外部器件发送数据到FPGA系统模型如图1.3所示。对FPGA的IO口进行输入最大最小延时约束是为了让FPGA设计工具能够尽可能的优化从输入端口到第一级寄存器之间的路径延迟,使其能够保证系统时钟可靠的采到从外部芯片到FPGA的信号。

图1.3 FPGA数据输入模型

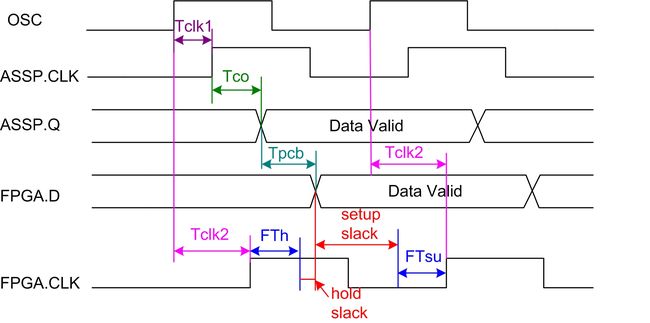

输入延时即为从外部器件发出数据到FPGA输入端口的延时时间。其中包括时钟源到FPGA延时和到外部器件延时之差、经过外部器件的数据发送Tco,再加上PCB板上的走线延时。如图1.4所示,为外部器件和FPGA接口时序。

图1.4 外部器件和FPGA接口时序

1. 最大输入延时

最大输入延时(input delay max)为当从数据发送时钟沿(lanuch edge)经过最大外部器件时钟偏斜(Tclk1),最大的器件数据输出延时(Tco),再加上最大的PCB走线延时(Tpcb),减去最小的FPGA时钟偏移(FTsu)的情况下还能保证时序满足的延时。这样才能保证FPGA的建立时间,准确采集到本次数据值,即为setup slack必须为正,如图1.1的所示,计算公式如下式所示:

Setup slack =(Tclk + Tclk2(min))–(Tclk1(max) +Tco(max) +Tpcb(max) +FTsu)≥0

推出如下公式:

Tclk1(max) + Tco(max) + Tpcb(max) –Tclk2(min) ≤ Tclk + FTsu

由Altera官方数据手册得知:

input delay max = Board Delay (max) – Board clock skew (min) + Tco(max)

结合本系统参数公式为:

input delay max = Tpcb(max) – (Tclk2(min)–Tclk1(max)) + Tco(max)

2. 最小输入延时

最小输入延时(input delay min)为当从数据发送时钟沿(lanuch edge)经过最小外部器件时钟偏斜(Tclk1),最小器件数据输出延时(Tco),再加上最小PCB走线延时(Tpcb),此时的时间总延时值一定要大于FPGA的最大时钟延时和建立时间之和,这样才能不破坏FPGA上一次数据的保持时间,即为hold slack必须为正,如图1.1的所示,计算公式如下式所示:

Hold slack = (Tclk1(min) + Tco(min) + Tpcb(min))–(FTh + Tclk2(max))≥ 0

推出如下公式:

Tclk1(min) + Tco(min) + Tpcb(min) – Tclk2(max) ≥ FTh

由Altera官方数据手册得知:

input delay max = Board Delay (min) - Board clock skew (min) + Tco(min)

结合本系统参数公式为

input delay max = Tpcb(min) – (Tclk2(max)–Tclk1(min)) + Tco(min)

由公式4和公式8得知,进行输入最大最小延时的计算,我们需要估算4个值:

(1) 外部器件输出数据通过PCB板到达FPGA端口的最大值和最小值Tpcb,PCB延时经验值为600mil/ns,1mm = 39.37mil;

(2) 外部器件接收到时钟信号后输出数据延时的最大值和最小值Tco;

(3) 时钟源到达外部器件的最大、最小时钟偏斜Tclk1;

(4) 时钟源到达FPGA的最大、最小时钟偏斜Tclk2;

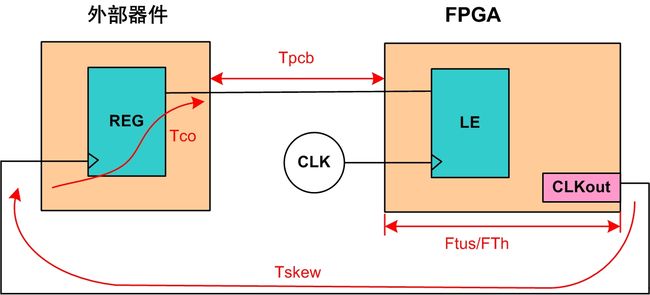

当外部器件时钟为FPGA提供的时候,Tclk1和Tclk2即合成Tshew,如图1.5所示:

图1.5 FPGA输出时钟模型

1.4 输出最大最小延时

FPGA输出数据给外部器件模型如图1.6所示。对FPGA的IO口进行输出最大最小延时约束是为了让FPGA设计工具能够尽可能的优化从第一级寄存器到输出端口之间的路径延迟,使其能够保证让外部器件能准确的采集到FPGA的输出数据。

图1.6 FPGA输出延时模型

输出延时即为从FPGA输出数据后到达外部器件的延时时间。其中包括时钟源到FPGA延时和到外部器件延时之差、PCB板上的走线延时以及外部器件的数据建立和保持时间。如所示,为FPGA和外部器件接口时序图。

图1.7 FPGA输出延时

1. 最大输出延时

由Altera官方数据手册得知:

Output delay max = Board Delay (max) – Board clock skew (min) + Tsu

由公式得知,最大输出延时(output delay max)为当从FPGA数据发出后经过最大的PCB延时、最小的FPGA和器件时钟偏斜,再加上外部器件的建立时间。约束最大输出延时,是为了约束IO口输出,从而使外部器件的数据建立时间,即为setup slack必须为正,计算公式如下式所示:

Setup slack =(Tclk + Tclk2(min))–(Tclk1(max) +FTco(max) +Tpcb(max) +Tsu)≥0

推导出如下公式:

FTco(max) + Tpcb(max) –(Tclk2(min) – Tclk1(max))+Tsu ≤Tclk

再次推导,得到如下公式:

FTco(max) + Output delay max ≤Tclk

由此可见,约束输出最大延时,即为通知编译器FPGA的FTco最大值为多少,根据这个值做出正确的综合结果。

2. 输出最小延时

由Altera官方数据手册得知:

Output delay min = Board Delay (min) – Board clock skew (max) –Th

由公式得知,最小输出延时(output delay min)为当从FPGA数据发出后经过最小的PCB延时、最大的FPGA和器件时钟偏斜,再减去外部器件的建立时间。约束最小输出延时,是为了约束IO口输出,从而使IO口输出有个最小延时值,防止输出过快,破坏了外部器件上一个时钟的数据保持时间,导致hlod slack为负值,不能正确的锁存到数据,最小输出延时的推导计算公式如下式所示:

Hold slack = (Tclk1(min) + FTco(min) + Tpcb(min))–(Th + Tclk2(max))≥ 0

推导出如下公式:

FTco(min) + Tpcb(min) – (Tclk2(max) – Tclk1(min))– Th ≥ 0

再次推导,得出如下公式:

FTco(min) + Output delay min ≥ 0

由公式得知,约束输出最大延时,即为通知编译器FPGA的FTco最小值为多少,根据这个值做出正确的综合结果。

由公式10和公式14得知,进行输出最大最小延时的计算,我们需要估算4个值:

(1) FPGA输出数据通过PCB板到达外部器件输入端口的最大值和最小值Tpcb,PCB延时经验值为600mil/ns,1mm = 39.37mil;

(2) 时钟源到达外部器件的最大、最小时钟偏斜Tclk2;

(3) 时钟源到达FPGA的最大、最小时钟偏斜Tclk1;

(4) 外部器件的建立时间Tsu和保持时间Th;

当外部器件时钟为FPGA提供的时候,Tclk1和Tclk2即合成Tshew,如图1.8所示:

图1.8 FPGA提供时钟模型

1.5 使用范围

通过作者使用总结情况,IO口时序约束主要使用在以下情况:

1. 数据交换频率较高

由于IO时序约束一般计算值都是在几纳秒,当FPGA和外部数据交换频率较低,如FPGA操作640*480的TFT液晶进行刷屏,数据传输频率仅仅24Mhz,一个数据时钟都有41.666ns,完全不用约束都能满足时序要求。但是当操作SDRAM运行到120M时候,由于一个数据变换周期才8ns,因此IO口的少量延时都会影响到SDRAM数据,因此这种情况下需要对输入输出进行完整的IO口时序约束,并且分析正确,才能消除数据传输不稳定过的情况。

2. 代码已经比较优化

当数据交换频率较高,但是时序约束还是不满足时序要求的时候,我们都需要对代码进行分析,好的时序都是设计出来的,不是约束出来的。如程序清单 1.1所示,首先hcount_r 和vcount_r 都为10位计数器,这样的代码TFT的三色输出的端口就会有很大的延时,因为dat_act的胶合逻辑太多,输出路径太长导致。这种情况下应该不是首先做时序约束,应该修改代码,尽量做到寄存器直接输出。只有当代码比较优化的情况,再做时序约束这样才能得到较好的结果。

程序清单 1.1 示例程序

1 assign dat_act = ((hcount_r >= hdat_begin) && (hcount_r < hdat_end))

2 && ((vcount_r >= vdat_begin) && (vcount_r < vdat_end));

3 assign tft_r = (dat_act) ? {rgb16_dat[15:11], 3'b111} : 8'h00;

4 assign tft_g = (dat_act) ? {rgb16_dat[10:5], 3'b111} : 8'h00;

5 assign tft_b = (dat_act) ? {rgb16_dat[4:0], 3'b111} : 8'h00;

1.6 总结

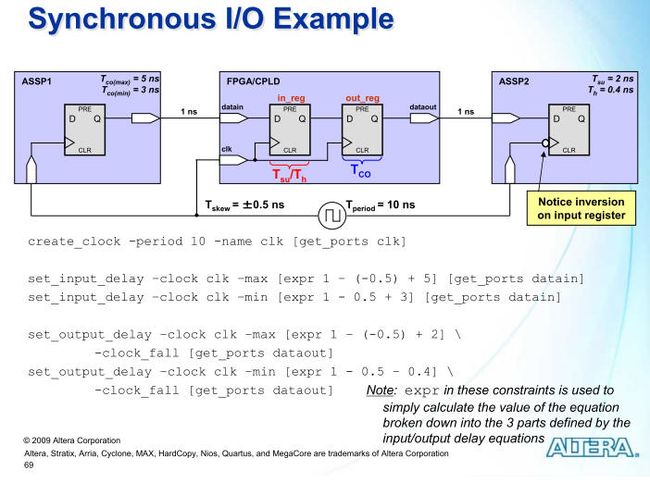

本文档主要是对FPGA的IO口时序约束进行相应的分析,并未做实际的使用分析,在后续文档中将会结合软件,以及实际案例对IO口时序约束进行详细的使用介绍。最后附上一个Altera官方的IO时序约束分析例子,如图1.9所示。

图1.9 Altera官方例程