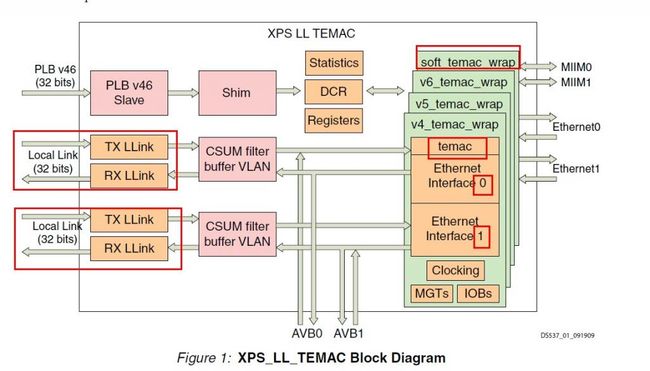

Spartan 6 temac 千兆网卡 IP 核使用

完整版下载 word 文档

http://download.csdn.net/source/3488111

参考

LogiCORE IP XPS LL TEMAC

DS537 December 14, 2010

Xilinx SP605

XPS TEMAC Ports

端口详细说明

1、------------------------------------

中断输出 至中断控制器。

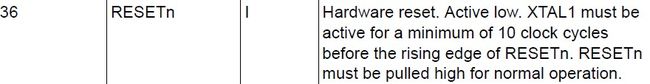

复位信号低电平有效。XTAL1 至少在 RST 信号 上升沿之前 10个周期先有效。

即 88E1111 PHY 应该先上电工作, 然后再复位 , 之后再操作。 正常操作时 RESET 信号 为高电平 。

2、-------------------------------

(3). When Ethernet statistics are enabled with the Virtex-6, Virtex-5, Virtex-4, and Spartan-3 device families, the Ethernet statistics

core’s reference clock is connected to REFCLK.

时钟信号 来自 FPGA 内部 Clock generator 200M

3、-----------------------------

LlinkTemac0_CLK (2) LocalLink to TEMAC LocalLink clock 来自系统时钟。

-------------------------

即:

TemacIntrc0_Irpt 输出中断

REFCLK 参考时钟输入

LlinkTemac0_CLK Llink 时钟 , 均与外部 PHY芯片没有关系 。

4、----------------------

GTX_CLK0 125M 时钟输入, 来自 FPGA 内部。

125 MHz input clock on global clock

routing used to derive the other

transmit clocks for all GMII and

RGMII PHY modes. For soft TEMAC

MII PHY systems, this clock must be

driven by some clock (does not need

to be 125 MHz). The PLB clock may

be used in these cases. Also used

when Ethernet Statistics are enabled

with the Spartan-6 device family

在 GMII PHY 模式下用来驱动发送时钟。 不与外部PHY 芯片交互。

5、-------------------

TemacPhy_RST_n

TEMAC to PHY reset signal

connected internally to the inverse of

the SPLB_Rst input. The PHY is

reset whenever the SPLB is reset

发送至 PHY芯片的复位信号 , 输出 ,初始值为 0

6、-----------------------

GMII_TXD_0(7:0)

TEMAC to PHY transmit data 传送数据至 PHY 8bit

7、-------------------

GMII_TX_EN_0

TEMAC to PHY transmit enable 传输使能

8、----------------------

GMII_TX_ER_0

TEMAC to PHY transmit Error enable 传输错误使能

9、---------------------------

GMII_TX_CLK_0

TEMAC to PHY transmit clock 传输时钟

联接至 PHY 的 GTX_CLK 输入引脚 ,

10、--------------------------------------

GMII_RXD_0(7:0)

PHY to TEMAC receive data 接收 8bit 数据

11、------------------

GMII_RX_DV_0

PHY to TEMAC receive data valid

indicator 接收数据有效指示

12、---------------------

GMII_RX_ER_0

PHY to TEMAC receive error

indicator 接收数据错误指示

13、-------------------

GMII_RX_CLK_0

PHY to TEMAC receive clock 接收时钟

发送数据及信号 125M 时钟,

100M传输速率时, 25M 时钟

10M 传输速率时, 2.5 时钟

14、----------------------

MII_TX_CLK_0

PHY to TEMAC transmit clock (also

used for GMII/MII mode) 10/100/1000模式时使用。

输入时钟,注意连接至FPGA 的全局时钟IO 口。

联接至 88E 1111 的 TX_CLK

在100M 模式时用来做发送时钟。

GTX_CLK 与TX_CLK 区别

GTX_CLK 由FPGA 输出 至 外部 PHY 88E1111芯片

TX_CLK 由 PHY芯片产生 输入至 FPGA 时钟引脚 。

15、----------------------------------

MDC_0

TEMAC to PHY MII management

bus clock

输出 时钟信号 ,

对应 88E1111

MDC 输入引脚 , 串行管理接口数据参考时钟输入。 最大 8.3MHz

16、--------------------------

MDIO_0

TEMAC to/from PHY MII

management data

数据 IO

管理数据, 需要上拉电阻 1.5K ~10K

类似 IIC 总线 。

综上,

与 PHY芯片相关的信号 共分3组,

发射组

与 88E 1111 128Pin QPF 封装之间的对应关系

FPGA 88E1111

-------------------------------------------------------

GMII_TX_CLK----------->GTX_CLK GMII 发送时钟, 提供125M参考时钟给 TX_EN \ EX_ER\TXD[7:0]。 在 10/100BASE-T模式及自适应模式下可以停止。

MII_TX_CLK --------> TX_CLK MII发送时钟,100Base-T模式下的时钟参考 TX_EN TX_ER TXD[3:0]。

GMII_TX_ER ------> TX_ER 发送错误

GMII_TX_EN -------> TX_EN 发送使能

GMII_TXD ---------> TXD 发送数据 TXD[7:4] 不使用时应接低电平。

共 12 个信号线

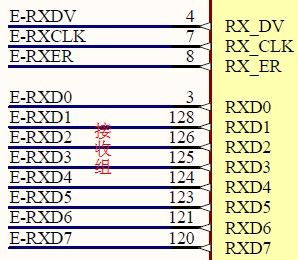

接收组

FPGA 88E1111

-------------------------------------------------------

GMII_RX_CLK --------> RX_CLK 接收时钟

GMII_RX_DV -----------> RX_DV 接收数据有效

GMII_RX_ER ----------> RX_ER 接收数据错误

GMII_RXD ------------> RXD 接收数据

共 11根信号 线

控制组

FPGA 88E1111

---------------------------------------------------

TemacPhy_RST ----------> RESET 低电平 复位

管理接口及中断

MDC -------------> MDC

MDIO --------------> MDIO

无 ------------> INT 中断输出信号 ,开漏输出 ,输出极性可编程,

无 --------------> COL 收发冲突检测, 全双工模式,一直为低,

无 ----------------> CRS 载波检测

PHY 88E1111 芯片接口

-----------------

JTAG组

TSRT JTAG 边界扫描复位输入信号。 低电平有效。 需要外接 4.7K 下拉电阻

----------------------

COMA 低功耗模式。 高电平开启低功耗模式。

RSET 电压参考输入。 接 1% 5K 电阻至VSS,即接至地电位参考。

----------------

125CLK 125M 时钟输出, 输出至外部 MAC 芯片, 使用 MAC 软核时 125M 时钟由FPGA 内核提供,

可以通过配置 CONFIG[3] 引脚关闭。

---------------------------

独立介质接口,与千兆RJ45接口相接

MDI0 +/- 在1000Base-T 模式

MDI1 +/-

MDI2 +/-

MDI3 +/-

XTAL1

参考时钟输入 25MHz + 50 ppm 或 125MHz + 50 ppm ,推荐 振荡器输入。

XTAL2

参考时钟输出

LED

-------------------------

LED_DUPLEX 输出 , 多功能引脚 , 用于 PHY_ADR

LED_RX

LED_TX

CONFIG 0..6 配置引脚

http://www.xilinx.com/support/documentation/boards_and_kits/ug065.pdf

Config0 用于配置 PHY_ADR[2..0]

Bus Interfaces

temac 中包含2个完全独立 MAC Interfce ,

Clock Pin Selection

时钟引脚选择

When targeting a GMII design, it uses a BUFGMUX to switch between the MII_TX_CLK and the GTX_CLK.

当使用GMII时,使用 BUFGMUX 切换 MII_TX_CLK \ GTX_CLK。

This allows for the design to support data rates of 10/100 Mbps and also 1000 Mbps

这样就可以同时支持 10/100 M 和 1000M。

The FPGA pins for these clocks must be selected such that they are located in the same clock region and they are both on clock dedicated pins.

上面两个时钟信号必须选择在同一个时钟区域中的时钟输入引脚上。

The GMII status, control, and data pins must be chosen to be in the same clock region as the above mentioned clocks.

GMII 的 status, control, and data 引脚必须选择在与上面的时钟信号相同的时钟区域中。

Please refer to the appropriate FPGA Family Clocking Resources User Guide for more information.

参考 FPGA Family Clocking Resources User Guide

Spartan-6 FPGA Clocking Resources User Guide UG382 (v1.6) May 12, 2011

Please pay special attention to clocking conflicts. Failure to adhere to these rules will result in build errors and data integrity errors.

尤其注意时钟冲突。