电子设计自动化实验 实验三 频率计制作

电子设计自动化实验 实验三

EDA

一.实验名称:综合性实验三、硬件描述语言的层次化设计

二.实验目的:

熟悉 EDA 软件(QuartusII)的硬件描述语言输入设计方法;

掌握 VHDL 语言的层次化设计方法和仿真分析方法;

了解功能仿真、时序仿真和时序参数分析的意义。三.实验内容:

采用层次化设计的方法,用 VHDL 语言的元件例化语句写出 4 位十进制频率计的顶 层文件,并分别给出其测频功能和时序仿真分析波形图,并加以分析;** 用 EDA 实验箱进行硬件验证,并分析测量结果;建议硬件测试实验电路采用 NO.0 电 路结构,待测信号 F_IN 接 clock0;测频控制时钟 CLK 接 clock2;** 用嵌入式逻辑分析仪 SignalTap II 实际监测 4 位十进制频率计中计数器模块和测 频控制器模块在 FPGA 的工作情况(以 F_IN 为逻辑分析仪的工作时钟,触发条件 DIN=0、CLK 上升沿)。**四.实验原理:

1.测频原理:

有一个测频控制器,这个测频控制器由一个输入信号和三个输出信号构成。分别是:

1.输入信号:CLKK --输入一个频率为1Hz的信号用于产生分频信号

2.输出信号:CNT_EN --通过分频信号得到一个时长为1秒的计数使能信号,用来控制计数器

3.输出信号:LOAD --对分频信号取反得到一个和计数使能信号相反的置数使能信号,用来控制锁存器

4.输出信号:CLR_CNT --在停止计数期间和置数完成后,产生一个计数器清零信号,清空计数器,以便下次测量测评控制器原理图

2.频率计原理:

测频控制器的计数使能信号CNT_EN能产生一个1秒脉宽的周期信号,并对频率计的每一计数器CNT4的ENA使能端进行同步控制。当CNT_EN高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。在停止计数期间,首先需要产生一个锁存信号LOAD,在该信号上升沿时,将计数器在前1秒钟的计数值锁存进各锁存器LTCH4中,并由外部的7段译码器译出,显示计数值。设置锁存器的好处是,显示的数据稳定,不会由于周期性的清零信号而不断闪烁。锁存信号之后,必须有一清零信号CLR_CNT对计数器进行清零,为下1秒钟的计数操作作准备。

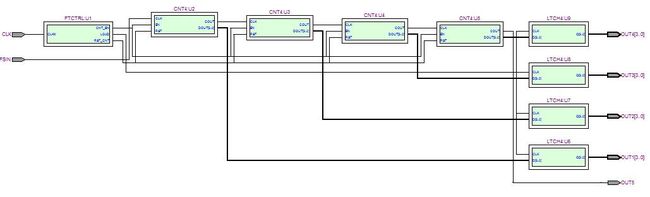

图片

五.实验代码

用元件例化的方法来实现频率计的功能。需要在频率计代码中调用测评控制器,锁存器,计数器的代码。

1.测频器代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY LAB_03 IS

PORT (

CLK,FSIN : IN STD_LOGIC;

OUT1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

OUT2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

OUT3 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

OUT4 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

OUT5 : OUT STD_LOGIC

);

END ENTITY LAB_03;

ARCHITECTURE bhv OF LAB_03 IS

COMPONENT CNT4 --调用计数器模块

PORT ( CLK,RST,EN : IN STD_LOGIC --为便于识别端口名与调用实体相同(可不同)

DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT : OUT STD_LOGIC);

END COMPONENT;

COMPONENT LTCH4 --调用锁存器模块

PORT ( CLK : IN STD_LOGIC;

D : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END COMPONENT;

COMPONENT FTCTRL --调用测频控制器模块

PORT ( CLKK : IN STD_LOGIC;

CNT_EN : OUT STD_LOGIC;

RST_CNT : OUT STD_LOGIC;

LOAD : OUT STD_LOGIC);

END COMPONENT;

SIGNAL NET1,NET2,NET3 : STD_LOGIC; --定义若干信号作为内部走线

SIGNAL D1,D2,D3,D4 : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL DOUT1,DOUT2,DOUT3,DOUT4 : STD_LOGIC_VECTOR(3 DOWNTO 0); --cnt4out

SIGNAL COUT1,COUT2,COUT3 : STD_LOGIC; --cnt4out

BEGIN --需要一个测评控制器,四个计数器,四个锁存器。分别定义每个元件端口映射

U1: FTCTRL PORT MAP(CLKK=>CLK,CNT_EN=>NET1,RST_CNT=>NET2,LOAD=>NET3);

U2 : CNT4 PORT MAP(CLK=>FSIN,EN=>NET1,RST=>NET2,DOUT=>D1,COUT=>COUT1);

U3 : CNT4 PORT MAP(CLK=>COUT1,EN=>NET1,RST=>NET2,DOUT=>D2,COUT=>COUT2);

U4 : CNT4 PORT MAP(CLK=>COUT2,EN=>NET1,RST=>NET2,DOUT=>D3,COUT=>COUT3);

U5 : CNT4 PORT MAP(CLK=>COUT3,EN=>NET1,RST=>NET2,DOUT=>D4,COUT=>OUT5);

U6 : LTCH4 PORT MAP(CLK=>NET3,D=>D1,Q=>OUT1);

U7 : LTCH4 PORT MAP(CLK=>NET3,D=>D2,Q=>OUT2);

U8 : LTCH4 PORT MAP(CLK=>NET3,D=>D3,Q=>OUT3);

U9 : LTCH4 PORT MAP(CLK=>NET3,D=>D4,Q=>OUT4);

END ARCHITECTURE bhv;

关于这段代码做以下两个简单说明

- 内部连接线:简单理解元件例化语句的功能,元件例化就是引入一种连接关系,将预先好的设计实体定义为一个元件,然后利用特定的语句将此元件与当前的设计实体中的指定端口连接。信号量就是用于内部多元件连接的端口。通过这个端口,两元件相对的映射连接起来。不同的是,这个端口并不区分端口模式(IN/OUT/INOUT/BUFFER),但区分端口的数据类型(STD_LOGIC/STD_LOGIC_VECTOR等)。因此“=>”是连接符号。

- 关于元件个数:在这个实体中共使用了九个元件,即U1~U9。其中计数器模块和锁存器模块都用了4个。所以为了区分,要个每个元件唯一的例化名,即U1~U9。然后再分别说明是哪个元件,并用端口映射去做连接。可用RTL图形观察器去检查连续是否正确。

U1 : FTCTRL PORT MAP(CLKK=>CLK,CNT_EN=>NET1,RST_CNT=>NET2,LOAD=>NET3);

U1为测评控制器,内部有四个信号。其中CLKK连接端口CLK,剩余三个输出分别连到内部信号端口NET1/2/3,以待其他元件连接即可联通。

RTL图示

附上调用的三个元件的代码

计数器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT4 IS

PORT (CLK,RST,EN : IN STD_LOGIC;

DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT : OUT STD_LOGIC);

END CNT4;

ARCHITECTURE behav OF CNT4 IS

BEGIN

PROCESS(CLK, RST, EN)

VARIABLE Q : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF RST='1' THEN Q := (OTHERS=>'0');

ELSIF CLK'EVENT AND CLK='1' THEN

IF EN='1' THEN

IF Q <9 THEN Q := Q + 1;

ELSE Q := (OTHERS =>'0'); END IF;

END IF;

END IF;

IF Q ="0000" THEN COUT<='1';

ELSE COUT<='0';

END IF;

DOUT <= Q;

END PROCESS;

END behav;

锁存器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY LTCH4 IS

PORT (CLK : IN STD_LOGIC;

D : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END LTCH4;

ARCHITECTURE bhv OF LTCH4 IS

BEGIN

PROCESS(CLK,D)

BEGIN

IF CLK'EVENT AND CLK ='1' THEN Q <= D;

END IF;

END PROCESS;

END bhv;

测评控制器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY FTCTRL IS

PORT(CLKK : IN STD_LOGIC;

CNT_EN : OUT STD_LOGIC;

RST_CNT : OUT STD_LOGIC;

LOAD : OUT STD_LOGIC);

END FTCTRL;

ARCHITECTURE bhv OF FTCTRL IS

SIGNAL DIV2CLK : STD_LOGIC;

BEGIN

PROCESS( CLKK ) BEGIN

IF CLKK'EVENT AND CLKK = '1' THEN

DIV2CLK <= NOT DIV2CLK;

END IF;

END PROCESS;

PROCESS( CLKK,DIV2CLK) BEGIN

IF CLKK='0' AND DIV2CLK='0' THEN RST_CNT <= '1';

ELSE RST_CNT <= '0';

END IF;

END PROCESS;

LOAD <= NOT DIV2CLK;

CNT_EN <= DIV2CLK;

END bhv;