LVDS/DVI/HDMI Interface

转载自:http://blog.csdn.net/shanghaiqianlun/article/details/6983878

数字视频信号

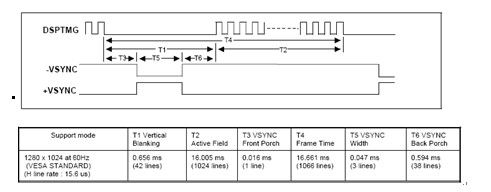

以SXGA为例,其时序如下:

垂直:

水平:

图中DSPTMG为使能信号,VSYNC为场同步信号,HSYNC为行同步信号。在行场的消隐期(T1与T7),DSPTMG为低电平,在此期间无有效视频数据。

注意一个重要参数:对于这个时序的SXGA点频是108MHz

1066×1688×60=107.964480MHz

1 Open LVDS Display Interface(OpenLDI)

LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口,每一条通道输出的都是一对差分信号。它为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。LVDS是利用电压差(典型值为350 mV)进行编码信息。

1.LVDS的电路组成

LVDS发送器将驱动板主控芯片输出的并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1.1 LVDS接口电路的组成示意图

2.采用LVDS规范传输数据的时序图

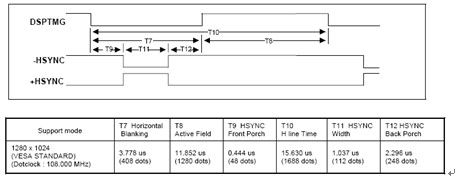

图1.2 18位单像素传输、非直流平衡模式

图1.3 24位单像素传输、非直流平衡模式

由图1.2可以看出,非直流平衡模式18位单像素传输共用了4个通道(1个时钟信号、3个数据信号),在一个时钟周期内传送了21bit,数据信号包括3×6位的RGB信号、使能信号DE、行场信号。其中使能信号DE很重要,实际上使能信号为低电平时就是行场的消隐期,有些接收端可不接收行场控制信号只接受使能信号即可,也正是因此;1.3图,非直流平衡24位单像素传输共用了5个通道,其中RES为预留位。

LDI突破了TTL瓶颈,带宽得到了提升。但随着1080p的视频信号成为主流,8位颜色要求大约3Gbps的带宽,这大大超过了4通道LVDS接口能力。所以LVDS有了双像素传输模式。

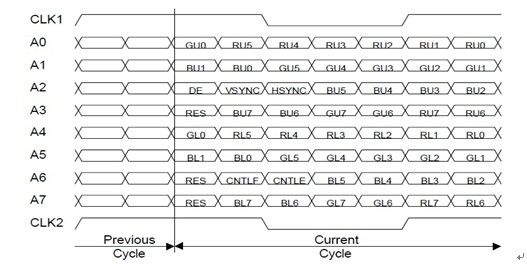

图1.4 24位双像素传输、非直流平衡模式

由图1.4可以看出,非直流平衡模式24位双像素传输共用了10个通道(2个时钟信号、8个数据信号),在一个时钟周期内传送了56bit,数据信号包括6×8位的RGB信号(两个像素)、使能信号DE、控制信号CNTLF和CNTLE、行场控制信号以及两个预留位RES。与图1.3相比,点频降低了一半,也就是位宽是原来的2倍。IC对较宽数据位处理时具有更大的采样余量,以及更大的电压和温度容限。此外,信号频率低,噪声频率也低,功耗也小。

另外LVDS也可以工作在直流平衡模式,直流平衡位的目的是最大限度地减少信号线的短期和长期的直流偏置。DCBAL是直流平衡位。

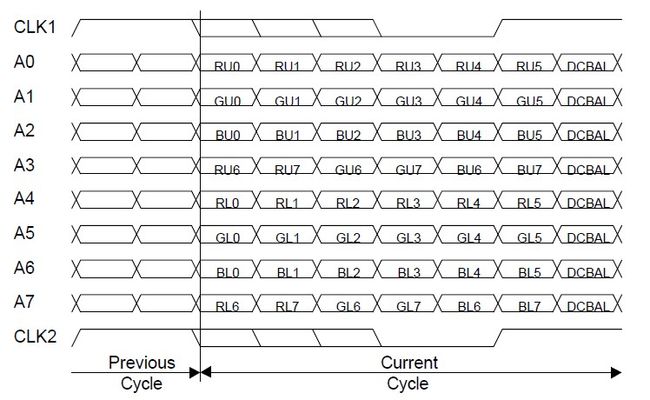

图1.5 24位双像素传输、直流平衡模式

图1.6直流平衡模式下24位双像素传输的数据格式

2 DVI(Digital Video Interface)接口

1.DVI简介

DVI即数字视频接口,是一种高速传输数字信号的技术,DVI视频传输避免了模拟视频信号传输过程中发送端(一般为显卡)的数模转换和接收端(一般为LCD显示器)的模数转换过程,同时也避免了模拟信号传输过程中的噪声干扰的问题,因此图像无损失。

DVI接口在传输数字信号时又分为单链路(Single Link)和双链路(Dual Link)两种方式。根据DVI标准,一条TMDS通道可以达到165MHz的工作频率和10-bit接口,也就是可以提供1.65Gbps的带宽,即每秒可传送1.65亿点像素。

单链路DVI接口的传输速率只有双链路的一半,最大的分辨率和刷新率只能支持到1920x1200,60hz。至于双链路的DVI接口,支持到2560x1600,60Hz模式,也可以支持1920x1080,120Hz的模式。液晶显示器要达到3D效果必须拥有120Hz的刷新率,所以3D方案中,使用DVI的话,必须要使用双连接的DVI接口的DVI线。总的来说,如果是1920x1200内的分辨率,单双连接两者输出的画质是一样的。

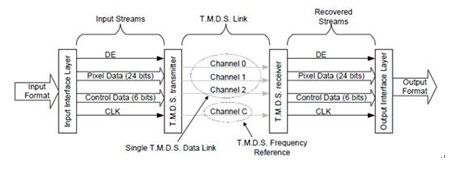

对于单链路的DVI接口,共有4个通道,通道0-2对应RGB三个分量,行场同步信号及一些可选的控制信号分别分配在在这三个通道上,第4个通道为时钟通道。DVI的核心技术是TMDS(Transition Minimization Differential Signal)技术,这里以8bit的R分量的传输为例简单做一个简单说明:并行的8bit的R分量传输时需要转化为串行数据,为了可靠传输,不能简单地进行了并转串,而是以TMDS编码算法进行并转串,TMDS算法使转换后的串行信号的变换最小(Transition Minimization)以及串行码流直流分量的平衡(DC Balancing)。串行信号是以差分形式传输的(Differential Signal)。在接收端,通过TMDS接收器可以解码出R、G、B、Hs、Vs、PixelClock等信号。

图2.3 单链路DVI接口

2. TMDS协议

图2.4 TMDS连接结构

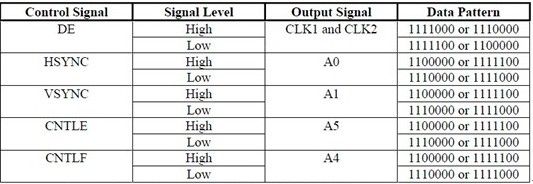

数据流中包含了像素和控制数据。DE有效期间,成为像素数据有效期间,就是说这段时间发送的是有效像素数据。DE无效期间,成为发送空间隙期间,这段时间发送的数据不包括有效像素数据,仅仅是控制信号。

发送端有3个一模一样的编码器,每个编码器的输入是2个控制信号和8bit的像素数据。依照DE的状态,编码器将按照两个控制信号的状态或8bit像素数据产生10bit的TMDS字符。每个解码器输出是一个连续的串行TMDS字符流。

TMDS数据通道传送的是一个连续的10bit TMDS字符流,在空期间,传送4个有显著特征的字符,它们直接对应编码器的2个控制信号的4个可能的状态。在数据有效期间,10bit的字符包含8bit的像素数据,编码的字符提供近似的DC平衡,并最少化数据流的跳变次数,对有效像素数据的编码处理可以认为有两个阶段:第一个阶段是依据输入的8bit像素数据产生跳变最少的9bit代码字;第二阶段是产生一个10bit的代码字,表示是否对输入代码进行反转。最终的TMDS字符,将维持发送字符总体的DC平衡。

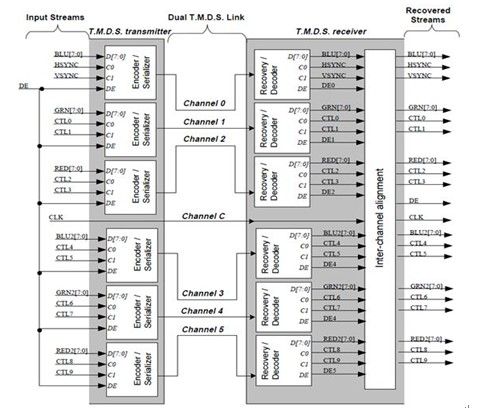

3. 单/双链路TMDS

图2.5 单链路TMDS通道映射

图2.6 双链路TMDS通道映射

无论是单链路还是双链路TMDS都是先将输入信号在发送端编码器编码,然后把并行数据转换为串行数据,由数据通道发送至接收端恢复为并行数据,最后进行解码。

单链路TMDS发送器由三个相同的编码器组成,如图2.5,2个控制信号和8bit像素数据映射到每个编码器,除了行同步HS和场同步VS外,其它控制信号的作用并没有定义,在发送器的输入端,控制信号CTL1、CLT2、CTL3必须保持逻辑低电平,推荐CTL0也保持逻辑低电平。

双链路发送器增加了三个数据通道,如图2.6,双链路配置在第一个链路上发送每行的奇像素,在第二个链路上发送每行的偶像素,每一行的第一个像素是奇数像素,即为像素1。

3 HDMI 接口(High Definition Multimedia Interface)

HDMI即高清晰度多媒体接口,源于DVI接口,同样以TMDS信号传输技术为核心,这也就是为何HDMI接口和DVI接口能够通过转接头相互转换的原因。HDMI是一种数字化视频/音频接口技术,是适合影像传输的专用型数字化接口,其可同时传送音频和影音信号,最高数据传输速度为5Gbps。同时无需在信号传送前进行数/模或者模/数转换。HDMI可搭配宽带数字内容保护(HDCP)(DVI也支持该协议),以防止具有著作权的影音内容遭到未经授权的复制。HDMI所具备的额外空间可应用在日后升级的音视频格式中。而因为一个1080p的视频和一个8声道的音频信号需求少于4Gbps,因此HDMI还有很大余量。这允许它可以用一个电缆分别连接DVD播放器,接收器。

图3.1 HDCP是一种双向内容保护机制

1 HDMI原理

一般情况下,HDMI连接由一对信号源和接受器组成,有时候一个系统中也可以包含多个HDMI输入或者输出设备。每个HDMI信号输入接口都可以依据标准接收连接器的信息,同样信号输出接口也会携带所有的信号信息。HDMI数据线和接收器包括三个不同的TMDS数据信息通道和一个时钟通道,这些通道支持视频、音频数据和附加信息,视频、音频数据和附加信息通过三个通道传送到接收器上,而视频的像素时钟则通过TMDS时钟通道传送,接收器接受这个频率参数之后,再还原另外三个数据信息通道传递过来的信息。

HDMI输入的源编码格式包括视频像素数据、控制数据和数据包。其中数据包中包含有音频数据和辅助信息数据,同时HDMI为了获得声音数据和控制数据的高可靠性,数据包中还包括一个BCH错误纠正码。HDMI的数据信息的处理可以有多种不同的方式,但最终都是在每一个TMDS通道中包含2位的控制数据、8位的视频数据和4位的数据包。HDMI的数据传输过程可以分成三个部分:视频数据传输期、数据包传输期和控制数据传输期。

图3.2 HDMI数据传输示意图

图3.3 HDMI对数据的编码

视频数据传输期,HDMI数据线上传送视频像素信号,视频信号经过编码,生成3路(即3个TMDS数据信息通道,每路8位RGB)共24位的视频数据流,输入到HDMI发射器中。24位像素的视频信号通过TMDS通道传输,将每通道8位的信号编码转换为10位,在每个10位像素时钟周期传送一个最小化的信号序列,视频信号被调制为TMDS数据信号传送出去,最后到接受器中接收。

数据包传输期,TMDS通道上将出现音频数据和辅助数据,这些数据每4位被一组,构成一个上面提到的4位数据包,数据包和视频数据一样,被调制为10位一组的的TMDS信号后发出。视频数据传输期和数据包传输期均开始于一个Guard Band保护频带,Guard Band由2个特殊的字符组成,这样设计的目的在于在明确限定控制数据传输期之后的跳转是视频数据传输期。

控制数据传输期,在上面任意两个数据传输周期之间,每一个TMDS通道包含2位的控制数据,这一共6位的控制数据分别为HSYNC(行同步)、VSYNC(场同步)、CTL0、CTL1、CTL2和CTL3。每个TMDS通道包含2位的控制数据,采用从2位到10位的的编码方法,在每个控制周期最后的阶段,CTL0、CTL1、CTL2和CTL3组成的文件头,说明下一个周期是视频数据传输期还是数据包传输期。

图3.4 CTL0、CTL1、CTL2和CTL3组成的文件头

数据包和控制数据的传输是在视频数据传输的消隐期,这意味着在传输音频数据和其他辅助数据的时候,并不会占据视频数据传输的带宽,并且也不要一个单独的通道来传输音频数据和其他辅助数据。这也就是为什么相比DVI,HDMI可以同时传输视频信号和音频信号的原因。