Xilinx ISE使用流程(从新建项目到仿真执行)-之一

最近在忙着做毕业设计(计算机专业,非电子专业),从小就喜欢电子技术,但由于之前没有接触过FPGA,所以特意跑书店买了一本《Xilinx FPGA数字设计》一书,这本书同时用VHDL和Verilog HDL两种语言讲解,使用的示例非常简洁明了,是一本非常适合入门的图。我在学习VHDL的时候,发现网上资料很少,所有决定把自己所学的知识和心得分享给广大网友,以便初学FPGA的同学们可以快速掌握Xilinx ISE工具的应用。

注意:阅读本篇文章需要数字电路和C语言等语言基础,本篇文章的代码示例出自《Xilinx FPGA数字设计》,请大家尊重版权。我使用的Xilinx版本为ISE 14.2。

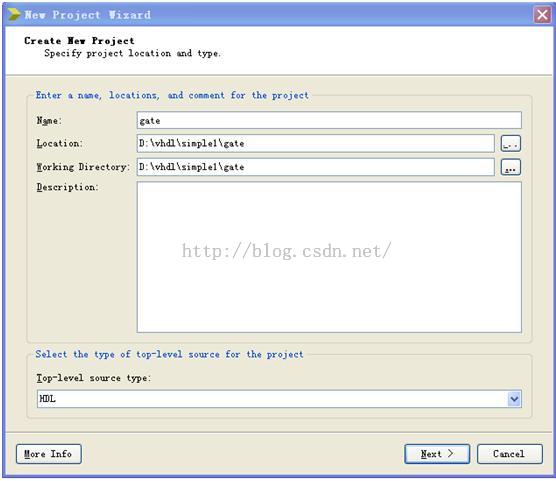

1、 新建项目

单击File->New Project,弹出New Project Wizard向导界面。在Namel一栏中输入gate,location目录选择D:\vhdl\simple1\gate,working Directory选择D:\vhdl\simple1\gate,Top-level source type:选择HDL,即硬件描述语言

单击Next,选择芯片型号和封装等,其中,芯片大家可以选择自己喜欢的,Synthesis Tool(综合工具)选择XST (VHDL/Verilog),Simluator(仿真工具)选择ISim (VHDL/Verilog),当然你也可以选择Modesim工具,Preferred Language(偏好语言)选择VHDL,VHDL Source Analysis Standard(VHDL语言分析标准)选择VHDL-200X

单击Next,进入Project Summary页面,单击Finish,这一节我就不截图了。

进入程序主界面,我们可以看到一个空视图(Empty View),如下图:

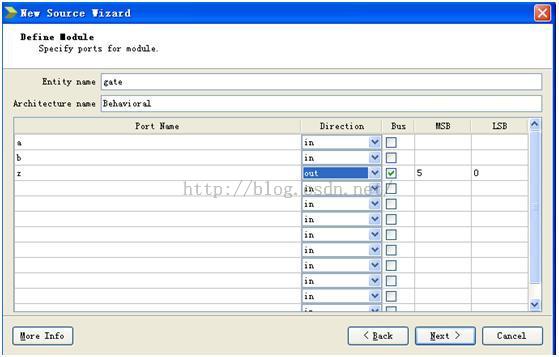

接下来我们要添加源代码了,在Hierarchy(层级)面板中选中XC6SLX16-3CSG324节点,右键单击New Source菜单,弹出New Source wizard向导界面,选中VHDL Module树节点,在右侧的File name输入gate。如下图:

单击Next按钮,在Port Name列中输入a,b,z三个变量,Direction(方向)选择:a,b选择in,z选择out,并选中Bus复选框,MSB(最高有效位)为5,LSB(最低有效位)为0,如下图所示:

单击Next后,再单击Finish,这一节我也不截图了。ISE会自动弹出gate.vhd源码编辑器,我们在41行输入如下代码(我贴的是全部的代码):

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 15:31:41 04/10/2016

-- Design Name:

-- Module Name: gate - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity gate is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

z : out STD_LOGIC_VECTOR (5 downto 0));

end gate;

architecture Behavioral of gate is

begin

z(0)<=a and b;--与门电路,将输入a和输入b进行与运算,赋值给z(0)

z(1)<=a nand b;--与非门电路,将输入a和输入b进行与非运算,赋值给z(1)

z(2)<=a or b;--或门电路,将输入a和输入b进行或运算,赋值给z(2)

z(3)<=a nor b;--或非门电路,将输入a和输入b进行或非运算,赋值给z(3)

z(4)<=a xor b;--异或门电路,将输入a和输入b进行异或运算,赋值给z(4)

z(5)<=a xnor b;--异或非门电路,将输入a和输入b进行异或非运算,赋值给z(5)

end Behavioral;

保存代码。接下来进行综合,综合主要是语法检查,编译和映射,双击No Processes Running窗口中的Syntesize – XST,如果有语法错误则需要解决语法错误。

接下来进行仿真,测试我们的程序是否正确。切换到Simulation窗口,选中gate节点,右键New Source菜单,选择VHDL Test Bench,在File Name中输入Test,如下图

单击下一步,选择gate,单击下一步,选择Finish完成。将60,71-92行的代码删掉。

重新添加如下代码:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY test IS

END test;

ARCHITECTURE behavior OF test IS

-- 门电路调用声明(UUT)

COMPONENT gate

PORT(

a : IN std_logic;

b : IN std_logic;

z : OUT std_logic_vector(5 downto 0)

);

END COMPONENT;

--输入信号

signal a : std_logic := '0';

signal b : std_logic := '0';

--输出信号

signal z : std_logic_vector(5 downto 0);

-- No clocks detected in port list. Replace <clock> below with

-- appropriate port name

BEGIN

-- 调用门电路

uut: gate PORT MAP (

a => a,

b => b,

z => z

);

--设置输入信号

init:process begin

a<='0';

b<='0';

wait for 100 ns;

a<='0';

b<='1';

wait for 100 ns;

a<='1';

b<='0';

wait for 100 ns;

a<='1';

b<='1';

wait for 100 ns;

end process;

END behavior;

看完这些代码,我不禁佩服这本书的作者,将如此简单易学的示例搬出来,这也是这本书非常出色的地方。超赞!

选中gate节点,然后点击Simulate Behavioral Model (仿真行为型行),如下图:

ISE自动弹出信真界面,单击![]() 按钮缩小波形窗口,直到出现下图

按钮缩小波形窗口,直到出现下图

波形说明:当a=0,b=0时,Z(0)是与门输出,为0,Z(1)是与非门电路,为1,Z(2)是或门电路,为0,Z(3)是或非门电路,输出为1,Z(4)异或门电路,为0,Z(5)是异或非门电路,为1,故波形输出由高到低为101010,证明我们的程序是正确的。如下图: