数字集成电路设计-3-除法器的verilog简单实现(续)

引言

1,改成clk方式。

2,添加clk,50MHz。

3, 添加rst,同步复位。

4,添加calc_done,指示计算完成,高有效。

3.1 模块代码

- /*

- * module:div_rill

- * file name:div_rill.v

- * syn:yes

- * author:network

- * modify:rill

- * date:2012-09-10

- */

- module div_rill

- (

- input clk,

- input rst,

- input[31:0] a,

- input[31:0] b,

- output reg [31:0] yshang,

- output reg [31:0] yyushu,

- output reg calc_done

- );

- reg[31:0] tempa;

- reg[31:0] tempb;

- reg[63:0] temp_a;

- reg[63:0] temp_b;

- reg [5:0] counter;

- always @(a or b)

- begin

- tempa <= a;

- tempb <= b;

- end

- always @(posedge clk)

- begin

- if(!rst)

- begin

- temp_a <= 64'h0000_0000_0000_0000;

- temp_b <= 64'h0000_0000_0000_0000;

- calc_done <= 1'b0;

- end

- else

- begin

- if(counter <= 31)

- begin

- temp_a <= {temp_a[62:0],1'b0};

- if(temp_a[63:32] >= tempb)

- begin

- temp_a <= temp_a - temp_b + 1'b1;

- end

- else

- begin

- temp_a <= temp_a;

- end

- counter <= counter + 1;

- calc_done <= 1'b0;

- end

- else

- begin

- counter <= 0;

- calc_done <= 1'b1;

- temp_a <= {32'h00000000,tempa};

- temp_b <= {tempb,32'h00000000};

- yshang <= temp_a[31:0];

- yyushu <= temp_a[63:32];

- end

- end

- end

- endmodule

- /*************** EOF ******************/

/*

* module:div_rill

* file name:div_rill.v

* syn:yes

* author:network

* modify:rill

* date:2012-09-10

*/

module div_rill

(

input clk,

input rst,

input[31:0] a,

input[31:0] b,

output reg [31:0] yshang,

output reg [31:0] yyushu,

output reg calc_done

);

reg[31:0] tempa;

reg[31:0] tempb;

reg[63:0] temp_a;

reg[63:0] temp_b;

reg [5:0] counter;

always @(a or b)

begin

tempa <= a;

tempb <= b;

end

always @(posedge clk)

begin

if(!rst)

begin

temp_a <= 64'h0000_0000_0000_0000;

temp_b <= 64'h0000_0000_0000_0000;

calc_done <= 1'b0;

end

else

begin

if(counter <= 31)

begin

temp_a <= {temp_a[62:0],1'b0};

if(temp_a[63:32] >= tempb)

begin

temp_a <= temp_a - temp_b + 1'b1;

end

else

begin

temp_a <= temp_a;

end

counter <= counter + 1;

calc_done <= 1'b0;

end

else

begin

counter <= 0;

calc_done <= 1'b1;

temp_a <= {32'h00000000,tempa};

temp_b <= {tempb,32'h00000000};

yshang <= temp_a[31:0];

yyushu <= temp_a[63:32];

end

end

end

endmodule

/*************** EOF ******************/

3.2 testbench

- /*

- * module:div_rill_tb

- * file name:div_rill_tb.v

- * syn:no

- * author:rill

- * date:2012-09-10

- */

- `timescale 1ns/1ns

- module div_rill_tb;

- reg clk;

- reg rst;

- reg [31:0] a;

- reg [31:0] b;

- wire [31:0] yshang;

- wire [31:0] yyushu;

- wire calc_done;

- initial

- begin

- clk = 0;

- rst = 0;

- #20 rst = 1;

- #40 a = $random()%10000;

- b = $random()%1000;

- #1000 a = $random()%1000;

- b = $random()%100;

- #1000 a = $random()%100;

- b = $random()%10;

- #1000 $stop;

- end

- always #10 clk = ~clk;

- div_rill DIV_RILL

- (

- .clk (clk),

- .rst (rst),

- .a (a),

- .b (b),

- .yshang (yshang),

- .yyushu (yyushu),

- .calc_done (calc_done)

- );

- endmodule

- /******** EOF ******************/

/* * module:div_rill_tb * file name:div_rill_tb.v * syn:no * author:rill * date:2012-09-10 */ `timescale 1ns/1ns module div_rill_tb; reg clk; reg rst; reg [31:0] a; reg [31:0] b; wire [31:0] yshang; wire [31:0] yyushu; wire calc_done; initial begin clk = 0; rst = 0; #20 rst = 1; #40 a = $random()%10000; b = $random()%1000; #1000 a = $random()%1000; b = $random()%100; #1000 a = $random()%100; b = $random()%10; #1000 $stop; end always #10 clk = ~clk; div_rill DIV_RILL ( .clk (clk), .rst (rst), .a (a), .b (b), .yshang (yshang), .yyushu (yyushu), .calc_done (calc_done) ); endmodule /******** EOF ******************/

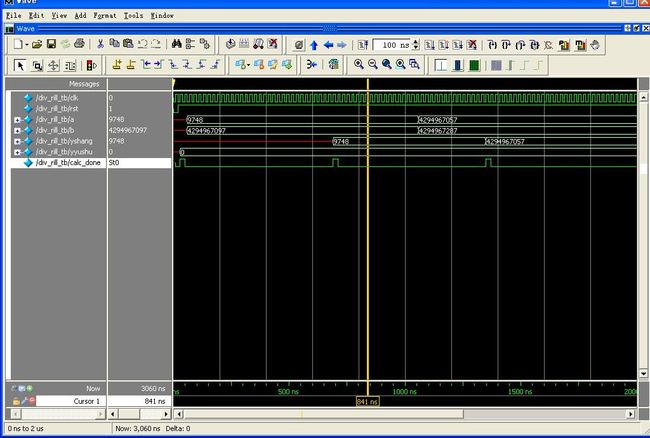

3.3 仿真

http://blog.csdn.net/rill_zhen/article/details/7964535