时钟设置的关键性寄存器

《朱老师物联网大讲堂》学习笔记

学习地址:www.zhulaoshi.org

这一节的内容,是来熟悉和时钟系统相关的寄存器。

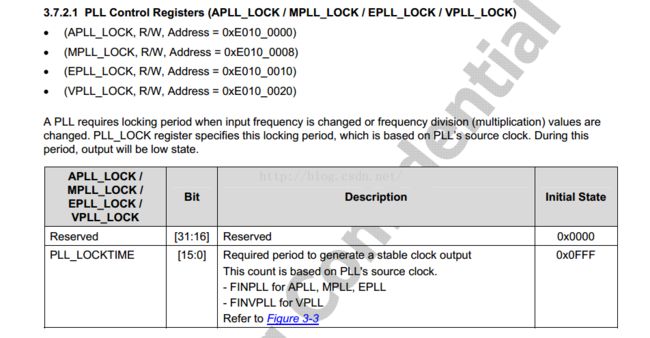

APLL_LOCK,MPLL_LOCK ,EPLL_LOCK, VPLL_LOCK,

这四个PLL可以简单记为xPLL_LOCK,都是用来控制对应的锁定周期的,

下图是数据手册相关介绍,没涉及具体怎么去计算,怎么去设置的问题。

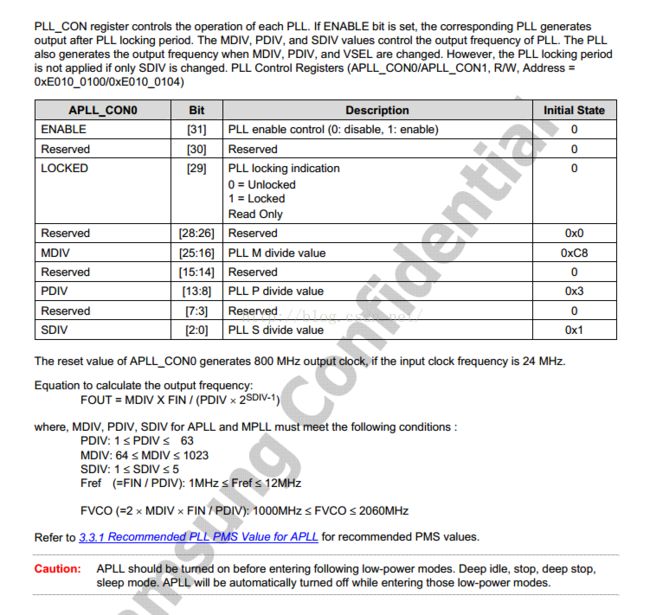

APLL_CON0,APLL_CON1

MPLL_CON

EPLL_CON0

EPLL_CON1

VPLL_CON

上述寄存器简记为xPLL_CON,主要是用来打开/关闭PLL电路,

设置PLL的倍频参数,查看PLL锁定状态等。

下面是APLL_CON0寄存器的介绍,下面还涉及了时钟频率的计算说明。

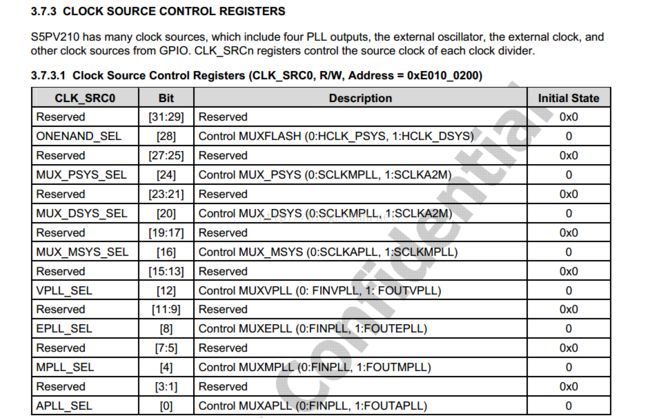

CLK_SRCn (n:0~6)

CLK_SRC寄存器是用来设置时钟来源的,对应时钟框图中的MUX开关,决定走哪一条路。

CLK_SRC_MASKn寄存器用来决定MUX开关n选1后是否能继续通过,

与前面的那个寄存器相比,一个决定走哪条,一个决定能不能走。

截图没截取完整,不过不重要,有一点要说明的是,时钟默认是开的!

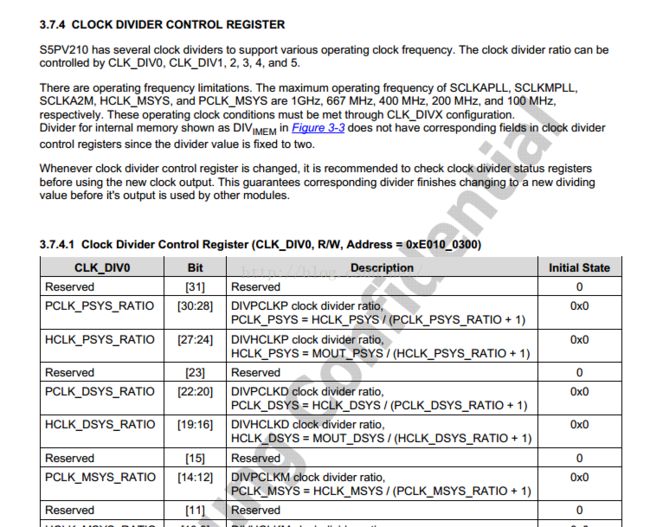

CLK_DIV

各模块的分频器参数设置

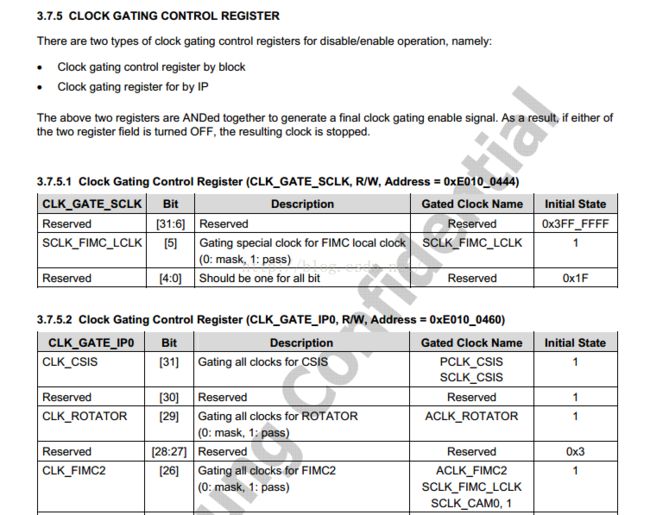

CLK_GATE

这个是控制最终输出的,

找个到,不知道是不是这个,怎么还分了两种~

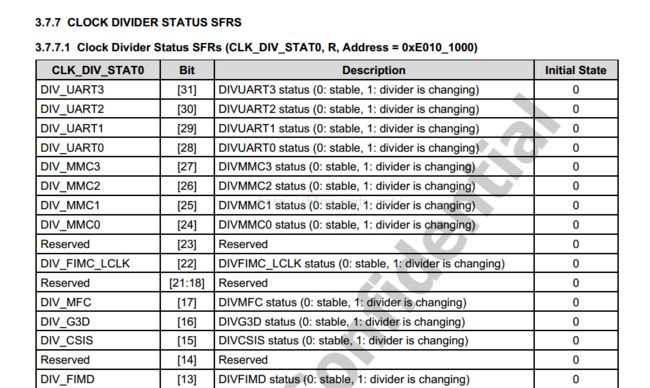

CLK_DIV_STATn

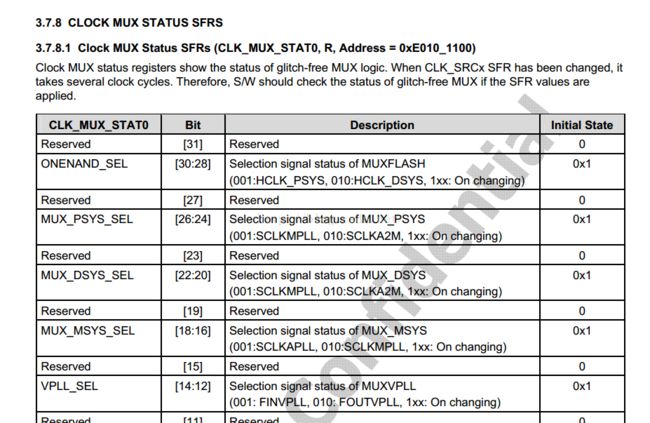

CLK_MUX_STATn

用来查看DIV和MUX的状态是否已经完成还是在进行中。

最重要的寄存器有3类:CON, SRC, DIV,

CON决定PLL倍频多少,

SRC决定走那一路,

DIV决定分频多少。