ARM ASM Conditional Execution

Conditional Execution

Here the description is based on ARMv7/Cortex-9.

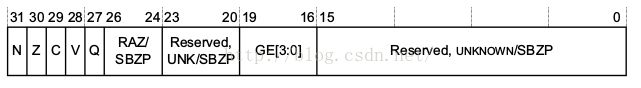

1. The Application Program Status Register (APSR)

Program status is reported in the 32-bit Application Program Status Register (APSR). The APSR bit assignments

are:

•

Reserved bits, that are allocated to system features, or are available for future expansion. Unprivileged

execution ignores writes to fields that are accessible only at PL1 or higher. However, application level

software that writes to the APSR must treat reserved bits as Do-Not-Modify (DNM) bits. For more

information about the reserved bits, see Format of the CPSR and SPSRs on page B1-1148.

Although bits[15:0] are UNKNOWN on reads, it is permitted that, on a read of APSR:

— Bit[9] returns the value of CPSR.E.

— Bits[8:6] return the value of CPSR.{A,I, F}, the mask bits.

This is an exception to the general rule that an UNKNOWN field must not return information that cannot be

obtained, at the current Privilege level, by an architected mechanism.

ARM recommends that these bits do not return the CPSR bit values on a read of the APSR.

•

Bits that can be set by many instructions:

—

The Condition flags:

N, bit[31] Negative condition flag. Set to bit[31] of the result of the instruction. If the result is

regarded as a two's complement signed integer, then the processor sets N to 1 if the result

is negative, and sets N to 0 if it is positive or zero.

Z, bit[30] Zero condition flag. Set to 1 if the result of the instruction is zero, and to 0 otherwise. A

result of zero often indicates an equal result from a comparison.

C, bit[29] Carry condition flag. Set to 1 if the instruction results in a carry condition, for example an

unsigned overflow on an addition.

V, bit[28] Overflow condition flag. Set to 1 if the instruction results in an overflow condition, for

example a signed overflow on an addition.

—

The Overflow or saturation flag:

Q, bit[27] Set to 1 to indicate overflow or saturation occurred in some instructions, normally related

to digital signal processing (DSP). For more information, see Pseudocode details of

saturation on page A2-44.

—

The Greater than or Equal flags:

GE[3:0], bits[19:16]

The instructions described in Parallel addition and subtraction instructions on

page A4-171 update these flags to indicate the results from individual bytes or halfwords

of the operation. These flags can control a later SEL instruction. For more information, see

SEL on page A8-602.

•

Bits[26:24] are RAZ/SBZP. Therefore, software can use MSR instructions that write the top byte of the APSR

without using a read, modify, write sequence. If it does this, it must write zeros to bits[26:24].

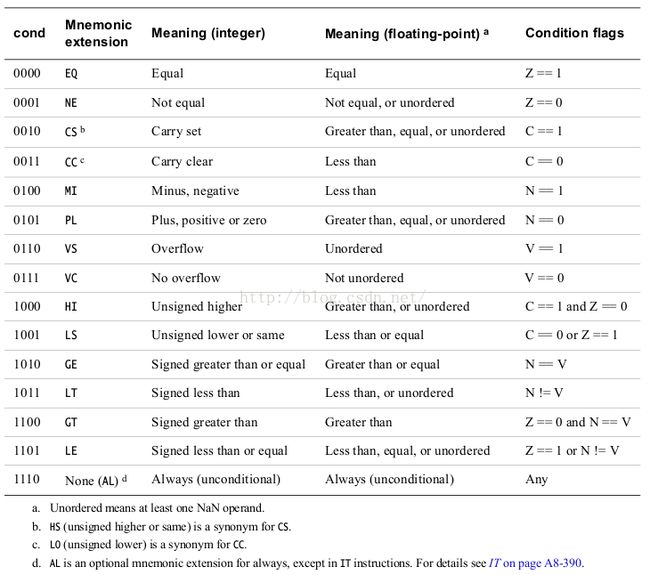

Instructions can test the N, Z, C, and V condition flags, combining these with the condition code for the instruction

to determine whether the instruction must be executed. In this way, execution of the instruction is conditional on the

result of a previous operation.

2. If corresponding condition is true, the instruction is executed. If the condition is false, the instruction is turned into a nop. The condition is specified by suffixing the instruction with a condition code mnemonic.