巅峰之作 IBM Power 7处理器架构分析

转自:http://server.it168.com/a2009/0831/671/000000671333_all.shtml

【IT168评测中心】在x86处理器Nehalem占据人们视线许久之后,其强有力的对手RISC阵营的一个重要的支柱:POWER架构最近开始动作连连,除了Freescale在嵌入式处理器市场的动作之外,IBM也开始在企业级微处理器市场出击,在前几天与硅谷中心地带——斯坦福大学举行的Hot Chips 21上,IBM宣布了最新一代POWER架构——Power 7处理器的详细资料。

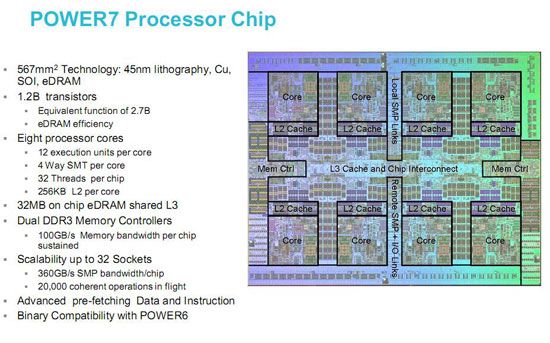

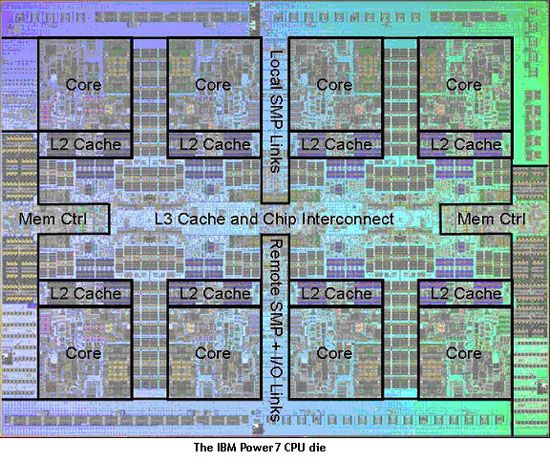

IBM Power 7处理器采用了IBM的45nm SOI铜互联工艺制程,典型的Power 7处理器具有八个核心,晶体管数量达到了12亿,核心面积567mm2,从这里可以明显看出Power7的与众不同,作为对比,同样八核心的Nehalem-EX具有23亿个晶体管,整整多了一倍。关于为什么具有这个差别后面将会谈到。

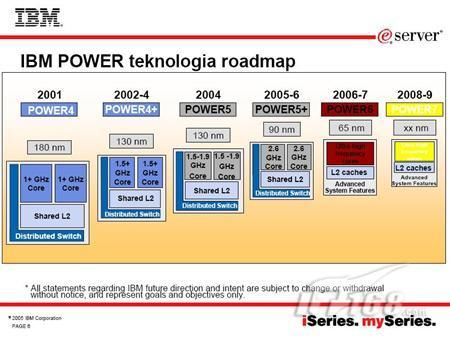

距离上一代Power6推出已经经过了三年(2006年Power6推出),三年的时间内,CISC,或者说x86处理器已经有了不少的变化,Power7的情况又如何呢?请看下文。

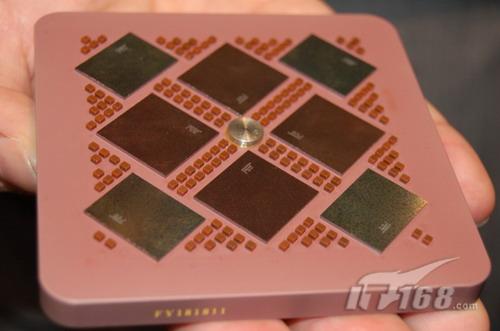

含有4个Power5 die和4个36MB L3缓存的Power5处理器

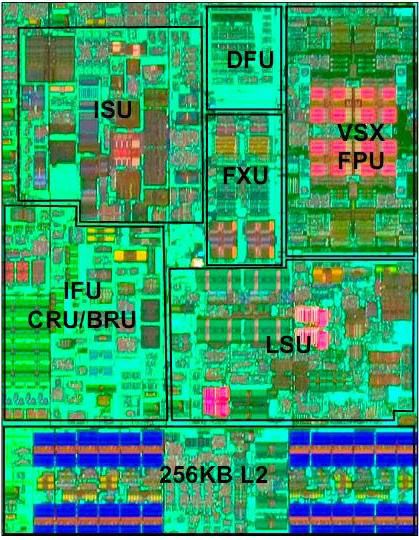

和以往的IBM Power处理器不太一样,IBM Power7是一个单晶片的八核处理器,而不是如Power5那样由多个晶圆合体(Power7据说支持单个处理器两个晶圆,也就是形成一个16核心处理器)。IBM Power7是一个典型的多核心处理器,每个核心的架构如下图:

单个IBM Power7核心

IFU:Instruction Fetch Unit,指令拾取单元

CRU/BRU:Condition Register Unit/Branch Unit,条件寄存器单元/分支单元

LSU:Load/Store Unit,存取单元

ISU:Instruction Schdule Unit,指令调度单元

DFU:Decimal Fixed Point Unit,十进制整数单元

FXU:Fixed Point Unit,整数单元

VSX FPU:Vector-Scalar Extension Floating Point Unit,向量/标量扩展浮点单元

通常,一条指令从左下开始顺时针执行到右下

Power7处理核心的最大特点是它具有12个执行单元,以及4个同步多线程。这12个执行单元是:

两个FXU整数单元+一个DFU十进制整数单元:十进制整数单元的用途目前暂时难以看到

四个VSX FPU向量/标量扩展浮点单元:和传统的FPU不同,它可以进行向量计算。Power7基于Power Architecture版本2.06,扩展了指令集以支持向量运算,对比于通常的SIMD,向量运算会具有更高的效率,它可以更好地利用寄存器

共四个LSU存取单元:内存存取——Load两个,Store两个——因此它紧挨着L1,以及L2

一个CRU条件寄存器单元和BRU分支单元:POWER架构和我们常见的x86不同,有些时候,一种特别的浮点运算是由额外的单元执行而不是由通用整数单元执行,这就是和POWER架构的condition register条件寄存器相关的运算,它由CRU来执行

BRU分支单元执行分支指令,实际上,它和CRU结合紧密,因此合在一起;CRU和BRU都有点偏向于控制单元(如IFU和ISU这样的就是彻头彻尾的控制单元),控制着指令的走向,因此它们靠近IFU指令拾取单元,也靠近L1/L2的位置

Power7是OOOE(Out-of-Order Execution,乱序执行)架构的处理器,和上一代Power6的IOE(In-Order Execution,顺序执行)不同——有趣的是,Power5是OOOE的,也就是说,Power7又变回去了。

顺序执行的结构简单,可以获得较高的运行频率,乱序执行则可以获得更好的运行效率,但是设计会变得复杂——设计不是问题,问题是发热量也随之增大。从结果来看,Power7的频率应该比Power6低一点。至于执行效率本身,乱序本身显然更好,Power7的流水线级数进行了缩减和优化以提升运行频率。

Power7的内核相对来说是非常复杂的,12个相对独立执行单元的设计可不常见,如Nehalem约有9个执行单元(不过执行端口只有6个:三个运算端口,三个存取端口。三个运算端口可以同时执行三个整数运算和三个浮点运算)。Power7在每个时钟周期可以分发6条指令,Nehalem则是4条,在单位时钟的微指令执行能力上,Power7大约是Nehalem的1.5倍。

强大的执行能力让Power7可以具有更多的多线程能力:每个Power7具有4个同步多线程,Power5和Power6都是两个。同步多线程是充分利用乱序架构的好方法,相对来说,顺序架构利用起来就比较难。近年来处理器的发展是追求低功耗、大规模并行,越来越走向多路处理了,既然走向了多核心,那么走向更多路的SMT同步多线程也就顺理成章了,相对来说Power7的功耗并不高,见后。在并行编程方面,进展比较缓慢,但进步总是有的。

显然,多线程技术将会越来越盛行,我们熟悉的x86世界:AMD已经宣布要采用多线程技术,而Intel的Nehalem将来可能会进化到4个多线程。

|

商用处理器

|

||||||||||||||

| 类别 | IBM Power5 | IBM Power6 | IBM Power7 | Fujitsu SPARC64 VI | Fujitsu SPARC64 VII | Sun UltraSPARC T1 | Sun UltraSPARC T2 | IBM/Sony/Toshiba Cell | Intel NetBurst | Intel Nehalem-EX | Intel Atom | Intel Itanium 2 Montecito |

||

| 核心数量 | 2 | 2 | 8 | 2 | 4 | 8 | 8 | 9 | 1 | 8 | 1 | 2 | ||

| 线程数 | 2x2 | 2x2 | 8x4 | 2x2 | 4x2 | 8x4 | 8x8 | 1x2+8(异构) | 1x2 | 8x2 | 1x2 | 2x2 | ||

| 多线程 | SMT | SMT | SMT | CMT | SMT | FMT | FMT+SMT | SMT | SMT | SMT | SMT | CMT | ||

| 流水线 | OOOE乱序 | IOE顺序 | OOOE乱序 | OOOE乱序 | OOOE乱序 | IOE顺序 | IOE顺序 | IOE顺序 | OOOE乱序 | OOOE乱序 | IOE顺序 | IOE顺序 | ||

Power7的L3——L4缓存值得一提,它的容量达到了32MB(包括特别快速的L3或者说L2.5在内)!实际上,这些缓存(至少是大部分)属于DRAM(Dynamic RAM,动态内存),和通常CPU使用的SRAM(Static RAM,静态内存)不同,IBM称之为eDRAM,embedded DRAM,集成动态内存。DRAM也就是我们通常的内存条使用的技术。

DRAM和SRAM的区别是:DRAM使用一个晶体管和一个电容存储一个bit,由于电容会漏电,因此必须周期性地充电以维持数据,优点是简单、便宜;SRAM则用6个晶体管(Nehalem则使用了8个晶体管以降低功耗)组成的双稳态触发器电路来存储一个bit,不需要周期性地充电,速度很快,然而占地面积大,耗电高,造价也高。

为什么要用DRAM呢?不是说DRAM的速度慢么?这要从多个方面来考虑:首先是容量,Power7本身的8个核心以及4路多线程要求具有大容量的缓存以维持一定的性能水准,至少要达到30MB;其次是功耗,假如采用SRAM的话,其功耗将会非常高的:32MB的缓存会消耗大量的电力,并且设计更加复杂,多个核心的内部互联也变得麻烦(4核心的Itanium 3 Tukwila具有30MB的SRAM L3,不过目前处于难产阶段),使用DRAM的话,功耗将得到降低,同时占地面积也更小,互联线路也简单了。唯一的缺点是性能,这一点无法避免,这应该就是L2.5或者说L3存在的原因,这个特别快速的4MB区域可能仍然是SRAM构成的。

大容量的L3通过内部互联结构连接,据说处理器核心互联的带宽达到了500GB/s!经过了大容量L3(L4)的筛选之后,仍然需要大量的内存带宽,Power7提供了两个DDR3内存控制器,每个控制器支持4个DDR3通道,大约支持到主流水准:DDR3-1600,这样内存控制器可以提供100GB/s的带宽!内置内存控制器的设计并不容易,需要提供各种RAS特性,并需要面对多种不同厂商不同型号不同参数的内存模组。Nehalem支持三个DDR3通道,Nehalem-EX也只支持4个。

为了更好地支持多个内存通道,并提高性能,Power7每个内存控制器都具有16KB的重调度缓存来重新排序内存存取请求。

Power7的一个重点是多路处理器,Power7实现了SMP的硬件一致性处理。一般而言,随着处理器数量的增多,处理器互联总线的带宽需求呈非线性的增长,受限于总线技术,一般的SMP系统在4路到8路左右就已经达到了饱和(x86的SMP机器都在这个范围左右),更大的系统就必须采用其它的拓扑结构了。

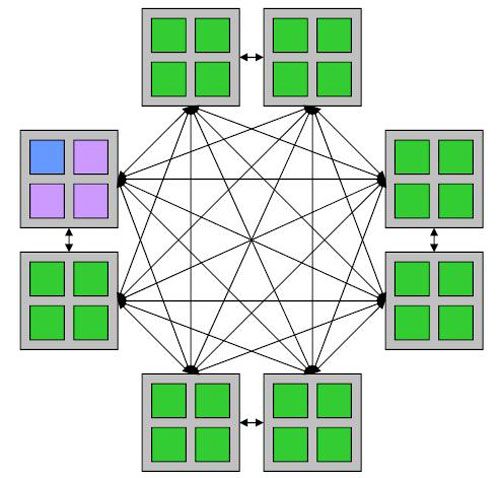

IBM Power 7 CPU:本地SMP连接(中上)和远程SMP连接(中下)

Power7通过三个方面的设计来达到32路SMP能力:巨大的带宽、特别的拓扑结构和特别的一致性协议。Power7的处理器间总线可以提供360GB/s的带宽。

Power7使用了一个两层的拓扑模型:4个处理器组成一个本地SMP组(需要7个本地I/O总线),然后8个SMP组之间两两直接互联(每个SMP组需要7个外部I/O总线),为了实现这个目标,Power7提供了两个总线:一个用于本地SMP,一个用于远程SMP。总线的位宽是120Byte。

此外为了支持这个拓扑结构,Power7的一致性协议混合了两种一致性消息的广播方法:一种是全局广播,一种是本地SMP组的猜测性广播。这个一致性协议定义了13种状态(Nehalem使用的MOESI是5种),并通过缓存线上额外的设置位,Power7最终实现了复杂的结构,在32路处理器、8核心、总共256个处理内核的SMP系统里,可以同时维持20000个缓存一致性操作。

显然,Power7打造了新的一代的顶级处理器平台:8核、4线程、32MB缓存,以及32路256核1024线程的大型SMP机器,Power7是目前处理器设计的巅峰之作。