直流电源总结

直流稳压电源总结

嵌入式电路设计的电源为所有功能模块提供能源,其效率和功耗是反应电路设计成功与否的绝对标志,故将稳压电源所涉及到的知识点梳理总结以巩固知识点。在嵌入式系统设计中所使用均是小功率芯片,而诸如PC电源等大功率电源可以直接找专业开关电源厂商直接购买,且开发难度非常大只有专业电源工程师才能把握。

常用直流稳压电源可分为线性稳压电源(俗称LDO)和开关稳压电源。前者调整元件工作于线性放大区,通过连续的电流所以其动态响应较好,但其功耗和体积较大转换效率很低,一般进行降压转换处理,使用在较敏感模拟电路。后者体积和功耗较小转换效率高,但其电压输出纹波大,动态响应差,可用于降压或升压转换处理。

线性稳压电源

上图为结构简图,V1是调整管,Vi是输入电压,Vo是输出电压。R1、R2形成采样电阻,采样电压Vf同参考电压Vr进行比较,放大产生的电压经过直流电平位移后,作为调整管的基极输入,这样构成一个负反馈回路。LDO功耗通输入和输出电压之间的差有关系,压差越大,功耗越大。决定输入和输出电压之差与输出级的调整管的饱和压降有关系。在低饱和方式中,输出级采用PNP功率晶体管,分别有以下几种饱和压降形式。

开关稳压电源

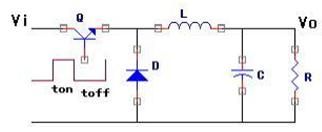

以上为DC-DC原理图,其实现方式有很多种,如最传统的脉宽调制(PWM)技术,目前流行的为提高效率的零电压、零电流、相移脉宽调制零电压谐振变换、还有最新的动态调整(DLL)等,对于DLL将在后面进行详细分析。

脉宽调制形式

² BUCK变换器 由电压源、串联开关和电流负载组成,也称为串联开关变换器。下图为其基本原理框图:

依据state2的接地不同可分为二极管接地和MOSFET接地,前者称为“同步”而后者称为“异步”

下面是其各自原理图

同步

异步

同步方式 Ton为晶体管道通时间,在此时间段,L电流逐渐增加,当道通结束后,进入晶体管截止时间段Toff,这时候由于L内电流到达最大值Imax,电感中电流不能突变,所以继续有电流流过并且逐步减少,此时二极管D充当截止时的续流元件。当截止结束后,电感中的电流到达最小值Imin,重新开始下一个周期。电压为Vin=VL+Vout,故为降压转换。

异步方式 与以上相同,只是其LOW-SIDE MOSFET充当续流元件。

² BOOST变换器 该变换器是从buck变换器进行对偶变换后得到的,其原理图如下:

BOOST开关又称为并联开关变换器,即开关与输入电源并联而得名。

BOOST开关又称为并联开关变换器,即开关与输入电源并联而得名。

当开关管导通时,二极管D关闭,电感L与开关管的节点电压为0。当开关管关闭时,电感L两端的电势翻转,所以电感L与开关管的节点电压大于输入电压Vi,电感电流通过二极管D续流,使得Vout=Vi+VL,可由下列公式证明,Vo = Vi*[T/(T-Ton)],T为开关脉冲周期,Ton是导通时间。

依据拓扑结构还有buck-boost、Cuk、推挽、全桥、半桥等就不做详细分析了。

前面的PWM通过控制开关管的导通占空比来调节输出电源功率,而谐振型转换器以正弦波处理功率开关管,使得开关管在零电流或者在零电压的情况下实现导通和关闭,从而降低开关功耗,提高变换效率。随着频率升高,开关损耗增加,开关管存在的结电容使得开关管承受感性关断、容性导通的恶劣条件。当开关导通时,电容上的能量损耗在器件内部,造成严重的开关噪声,并且通过开关密勒电容耦合到驱动电路,使得驱动电路产生噪声和不稳定因素;关断时,由Ldi/dt感应电动势产生电压尖峰对开关管的最大电压具有很大挑战,同时关断时结电容储存CV2/2的能源。为了改善晶体管的工作条件,提出零电流开关和零电压开关技术,并且引入谐振的概念。

² 零电流谐振开关 其原理图如下:

按照开关中电流允许单向还是双向流动,可以分为半波型和全波型,如下图所示:

其原理是:当LC回路经过开关管谐振,电流缓慢上升,在电流上升之前,晶体管经过驱动进入饱和区,由于LC的谐振作用,开关中的电流将振荡,使得开关能够自动换流。由于谐振开关没有瞬态的大电压和大电流同时流过,故而开关管的损耗是很低的。

² 零电压谐振开关 其原理图如下:

其工作原理在此不作阐述。

由于谐振电源中传输的是正弦波,PWM传输的是方波,正弦波包含的能量没有方波高。经过谐振型开关电源减低了开关损耗,但是传递的能量却下降了,所以整体转换效率并不比PWM电路高多少。

电源拓扑结构中电感选择

电感芯常用有铁芯粉、钼坡莫合金粉末MPP、气隙铁氧体以及铁硅铝磁合金或高磁通磁环。当混合镍铁和钼粉末成本,MPP是最昂贵的选择,铁硅铝磁合金是次昂贵的复合粉末磁芯。在多数电源中常见的灌形、E和EI形磁芯为气隙铁氧体,这些外形可以在必要时提供灵活性和可变性,但成本更高。高磁通磁环常用于滤波电感而不是电源变换电路,而功率电感则常用铁芯粉。

一般较小电感值带来较大峰值电流,相应的带来较大的输出电压纹波;而较大电感值可以减小峰值电流来减少电压纹波。从能量储存方面来看在相同开关时间内电感越大储存的能量越多,所以小电感比大电感动态响应要快,电源转换效率电感小的要比电感大的要低。而对于同样电感值时,一般尺寸较大的直流电阻较低而可提供0.5%到1%效率提升。

根据电感公式有:

V = L*di/dt

V=Vi-Vo,ΔT=Ton即开关的导通时间,而Ton=T*D(T为振荡周期且T=1/F,D为导通占空比D=Vo/Vi),且di/dt的中值等于Io,所以峰值电流等于Io+ di/2.

一般电源要求电流纹波在0.3Io~0.5Io之间,计算时选择精度较高的0.3Io即可。所以公式可变为Vi-Vo =L*ΔI/(1/F* Vo/Vi),即

L≥(Vi-Vo)*Vo/0.3Io*Vi*F(其中Vi取输入最大值ViMax来计算)

以上只是理论模式的计算,在实际电路中还存在着电感串联电阻损耗、高低边MOSFET损耗、开关管损耗。

电感串联电阻损耗 PL = I2*R,其中R为电感串联电阻。在确定了电感值后一般选择电阻较小的电感以提高转换效率。

高低边MOSFET损耗

² 高边MOS管损耗 Pmos = Io2*R*D,其中R为高边管导通有效电阻,D= Vo/Vi。

² 低边MOS管损耗 Pmos = Io2*R*D,其中R为低边管导通有效电阻,D=1-Vo/Vi。

当输出电流较大时,由于发热效应使得管导通电阻变大,所以要适当增大电阻值。

开关损耗 开关损耗在开关打开和关闭的过程中,有MOS管栅极电容充放电而引起,在开关打开瞬间,开关两端电压较大将给栅极电容充电;关闭时电容放电电流较大,且充放电都在器件内部进行故而很容易产生噪声和干扰。

一般采用粗略计算开关功率损耗:Psw =V*Io*tsw*fsw,其中tsw为开通或关闭时间(不是占空比所对应的开通和关闭时间,是MOS接收到信号到有效动作的延时时间),fsw为开关频率。

以上只是对功耗的详细计算,在实际的选择电感值计算时不需如此复杂。可以根据如下公式来计算即可:

对于同步电路,即设计中片外拓展肖特基二极管续流。使用

L≥(Vi-Vo- Io*R)*(Vo+Io*R)/0.3Io*Vi*F (R为肖特基电阻和电感电阻之和)

对于异步电路,即设计中使用低边MOS管进行续流时:

L≥(Vi-Vo-Io*R)*(Vo+Io*R)/0.3Io*Vi*F (R为低边管导通有效电阻和电感电阻之和)

死区时间在电源IC设计中的应用

如下图为一种DC-DC转换器的拓扑结构,Q1为开关管,Q2为同步整流管。控制电路产生DRVP和DRVN两个信号,以控制Q1和Q2轮流导通,使输出电压保持在稳定值。

由于MOS管具有双向导通特性,可能存在开关管Q1和整流管Q2同时导通的状态,而且两个管子的导通电阻很小,导通电流会很大,将会影响电源效率。为了防止这种情况的发生,需要在两个管子的开关信号之间插入一个死区时间(deadtime)。

固定死区时间是较常用的方法,结构简单,但为了保证系统在整个工作范围内功率管和整流管都不会同时导通,死区时间要足够长。在此期间,电路就可能通过Q2的寄生体二极管放电,产生功耗。与之相匹配是零电平检测技术:当P管关闭后,检测LX点电压,若为0,将N管导通。这种技术可以动态改变死区时间,然而由于电路中使用比较器,其产生的延时是无法避免,而且随着工艺参数,温度等环境因素的影响而发生改变,因此会产生多余的导通时间,使用动态逻辑调节技术可以获得合适的死区时间,并且对环境依赖较小,但实现起来较复杂,在此介绍死区时间控制电路利用动态检测电感中的电流改变电容重放电时间,不需要比较器。

² 总体电路框图

PWM信号经过两相不交叠时钟电路的变换,产生DRVP,DRVN来分别驱动Q1和Q2,当PWM下降沿到来时,DRVN首先为0将Q2关断,然后通过延时(fixed time)信号到达与非门1,在经过缓冲(反向器)后,DRVP才变为0,P管开启;PWM上升沿时P管关闭,LX电压从VDD大小开始下降,然后经过动态死区时间控制和缓冲级,DRVN变为1,N管重新开启。

² 动态死区时间延时电路

如下图所示:

若死区时间过长,则寄生体二极管导通,LX电压被钳位到-0.7V;死区时间过短会导致开关Q1和Q2同时导通,产生能量损耗。上图为死区时间为a合适 b过长 c过短的电压情况。

合理的死区时间是LX电压降为0的时间,即为零电压检测(前面已阐述),只不过使用延时电路取代了零电压比较器而已。左图为时间控制电路原理图,Q2的寄生电容Cx的放

电时间为Tx = Cx*Vdd/IL,从Vdd降到0的放电时间。可知死区时间是和电感电流成反比的。因此可以采样电感电流来动态地调节死区延时时间,使其在电流增大时减小,达到优化目的。

反相器对电容充电产生的延时受Isen控制,有如下公式

Ty=Cdelay*Vdd/Isen,若设定Cdelay=Cx/K,则Tx=Ty,即电路产生的延时与寄生电容放电时间相等,得到合适的死区时间而使得LX电压恰好降为0时打开Q2管。

电流采样电路

该模块是DC-DC中的重要单元,需要具备高精度,高速度,才能准确地感应负载电流的变化。

其电路图如下:

上图中Ms的作用是镜像Q1的电流,Q1在开启时工作在线性工作区,所以Ms也要工作在线性工作区(Ms和Q1一样均接地)。因为Q1工作于线性区,漏源电压与电流成正比,即:

Ms1和Ms2构成开关管(压降可以忽略)以防止M5源极接地,MR为源极跟随器;M2—M5组成单级放大器,钳制Vr与VLX电压相等,M6—M8为其提供偏置,M9提供一个负反馈,可以增大放大器的带宽并提高速度,为了提高精度,Ibias值很小。

当Vr = Vlx时,那么Iq1/Is =(W1/L1)/(W2/L2)=K

且Iq1=IL+Ibias,Is=Ir+Ibias,Ir=Isen

当Ms和Q1取一样的PMOS管时,则有IL = Isen

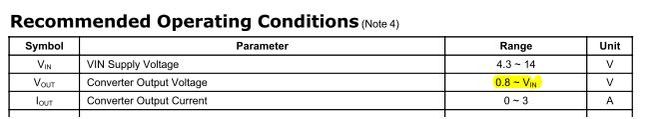

现以APW7145为例来计算其损耗和确定电感值

由上查表可得:

输入电压范围为4.3-14V,开关切换频率为500K,常见高边阻抗为55毫欧,低边为45毫欧。

后面结构图所示此为异步DC-DC降压转换器,对LX电压采用零电位比较器进行检测。死区时间为可控制,常见死区时间为20ns且对应LX电压为-700mV;此死区时间过长,寄生体二极管导通,LX电压被钳位到-0.7V。

考虑使用最大输出电流为500mA

进行简单计算电感值:L≥(Vi-Vo)*Vo/0.3*Vi*F

=(12-3.3)*3.3/0.3*12*500000=15.95uH