【我所認知的BIOS】—>PCI 的中斷(PIC下)

【我所認知的BIOS】—>PCI 的中斷(PIC下)

LightSeed

2009-5-13

1、PCI中斷概述

注:整篇都是討論在PIC(8259)下的中斷過程。當PCI設備插到主板上後(本來南橋裏含有的當然就不用插啦),它要和其他設備通信,或者讓CPU幫它做這般這般,或者CPU讓它做那般那般等等。。。那麼他們究竟是怎麼通信的呢?這就是PCI中斷在中間起的強大作用。PCI中斷,有一個很大的特點,它可以共用。這個特點我先提出來,對於後面講做個鋪墊。

2、PCI中斷的HW

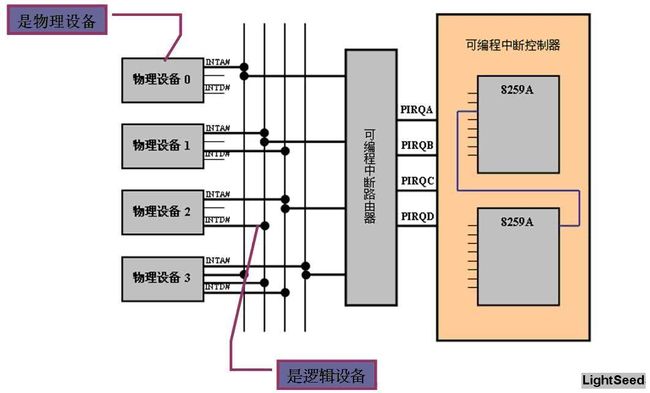

在談到PCI設備的時候,我要首先說明一下。我們平時用程式去scan的那個device是邏輯上的device。比如說BUS#0DEV#31FUN0中說的device是邏輯device。而平時我們說一個PCI顯卡,PCI網卡設備,他們都是物理device。一個物理device可能會有多個邏輯device。這裡其實就是function的意思。邏輯device其實是function。這裡要搞清楚。圖2.1是對PCI設備中斷的抽象圖。

PCI設備用INTA~INTD pin連接到8259來傳送中斷信號。需要說明的是,單function的PCI設備只能用INTA。

圖2.1 PCI設備中斷的抽象圖

正如圖2.1所示,設備引出的INTx連接經過中斷路由後連接到8259的PIRQA~D。

3、INTx的繞線

細心的人肯定會發現,上面圖2.1中的連線是有繞的。那麼爲什麽HW要這樣做呢?這就牽涉到“loading balance”的概念。以下是引用程式設計俱樂部的帖子,原作者liaoo

“Interrupt pin為出廠時就決定的,不能改變. Ex. 使用 SE or ru check PCI Reg3Dh = 01/02/03/04 for INT#A/B/C/D. 而 interrupt line則是BIOS知道了 "routing"後去填的.例如,BIOS知道

INT#A最終會接到 PIC mode的 8259的 IRQ 11,則 PCI Reg3Ch在 PCI scan 階段會被填成 "0Bh". 至於你說的如何接,PCI spec有提到,為了 "loading balance", board designer可以決定.Ex. 2 PCI devices, 都是利用 INT#A發 interrupt(so their PCI Reg3Dh = 01h).兩者接到同一個板子上. 假如,board designer決定將:(以下為假設的接法)

PCI slot1 接成: INT#A接到 I-router的INT#B,INT#B接到 I-router的INT#C,INT#C接到 I-router的INT#D,INT#D接到 I-router的INT#A PCI slot2 接成: INT#A接到 I-router的INT#A,INT#B接到 I-router的INT#B,INT#C接到 I-router的INT#C,INT#D接到 I-router的INT#D

則當 2 PCI devices接到 slot1 and 2時,就發生:雖然都是透過INT#A發 interrupt,但是,最後卻是從 "不同的 source出去的 ( Device 1 從 INT#B出去,Device 2從 INT#A出去...)”

4、分配IRQ給PCI設備。

如前文所述,繞線好了後,經過路由INTx都連接到了PIRQA~D。BIOS kernel會把經過計算好的可以用的PCI irq No.分配給PIRQA~D。比如說PIRQA~D分別對應IRQ5,IRQ9,IRQ5,IRQ9。那麼最終連接到PIRQA上的設備(邏輯設備)都會分配到IRQ5。至此PCI IRQ的分配就算是完成了。

5、關於PCI IRQ的說明

有人肯定會疑問,爲什麽上面PIRQA和PIRQC對應的IRQ No.都是5呢?這個怎麼能通信啊?呵呵,您的擔心是正常的,但是又是工程師們已經解決了的問題。篇首有提到,PCI IRQ是可以共用的。在這裡便被派上用場啦。

6、關於PCI IRQ Routing Table

6.1 PCI IRQ Routing Table綜述

上面的幾點我們談的熱火朝天,只有確定了PCI設備的INTx連接到了南橋的PIRQy那麼就可以正確地把IRQ No.分配給相應的PCI設備了。但是這裡有一个缺点:OS或者其他說軟體是無法知道硬體上究竟某個設備的INTx與南橋的PIRQy具體是怎麼對應的。OS或者其他軟體在不值得的情況下就不能正確分配IRQ No.給設備。那麼這個PCI IRQ Routing Table就挺身而出充當了描述硬體信息的這麼一個角色。它在整個IRQ分配的過程中,是重中之重。那麼我們來分析一下它的架構。

6.2 PCI IRQ Routing Table 的結構

| Byte Offset |

Size in Bytes |

Name |

| 0 |

4 |

Signature |

| 4 |

2 |

Version |

| 6 |

2 |

Table Size |

| 8 |

1 |

PCI Interrupt Router's Bus |

| 9 |

1 |

PCI Interrupt Router's DevFunc |

| 10 |

2 |

PCI Exclusive IRQs |

| 12 |

4 |

Compatible PCI Interrupt Router |

| 16 |

4 |

Miniport Data |

| 20 |

11 |

Reserved (Zero) |

| 31 |

1 |

Checksum |

| 32 |

16 |

First Slot Entry |

| 48 |

16 |

Second Slot Entry |

| (N + 1) * 16 |

16 |

Nth Slot Entry |

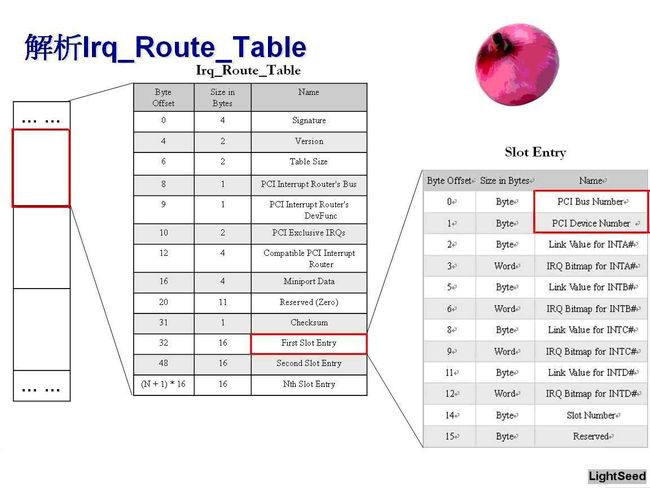

關於上面的這個結構表,其實我是想用中文描述一下,但是又覺得真的不妥。有些文字翻譯過來以後就有點不好理解。我還是貼一下PCI IRQ Routing Table spec的原文吧。如果有人對這個的E版真的不太瞭解,那麼我想我可以嘗試一下翻譯過來。只是這個表頭其實在BIOS code中都是固定的,或者會自動算好的(所以知道就可以了)。重要的是“Slot Entry”。所以我要對這個部份詳細說明一下。

6.3 Slot Entry的解析

Slot Entry: Each slot entry is 16-bytes long and describes how a slot's PCI interrupt pins are wire OR'd (線或)to other slot interrupt pins and to the chip set's IRQ pins. Each entry has the following format:

| Byte Offset |

Size in Bytes |

Name |

| 0 |

Byte |

PCI Bus Number |

| 1 |

Byte |

PCI Device Number (in upper five bits) |

| 2 |

Byte |

Link Value for INTA# |

| 3 |

Word |

IRQ Bitmap for INTA# |

| 5 |

Byte |

Link Value for INTB# |

| 6 |

Word |

IRQ Bitmap for INTB# |

| 8 |

Byte |

Link Value for INTC# |

| 9 |

Word |

IRQ Bitmap for INTC# |

| 11 |

Byte |

Link Value for INTD# |

| 12 |

Word |

IRQ Bitmap for INTD# |

| 14 |

Byte |

Slot Number |

| 15 |

Byte |

Reserved |

對於上表,Byte Offset 0和1分別是PCI Bus No.和Device No.這是在軟體運行過程中判斷的標誌。“Link Value for INTA#”則是一個數字,分別是代表INTA連接到了南橋的PIRQy。比如說:0代表連接到了PIRQA,1代表連接到了PIRAB。。。等等。後面以此類推。以上各個slot聯合在一起就是我們平時經常說的PCI IRQ Routing Table了。其實真正深入進去看,它也不是那麼神秘。

6.4 圖解PCI IRQ Routing Table

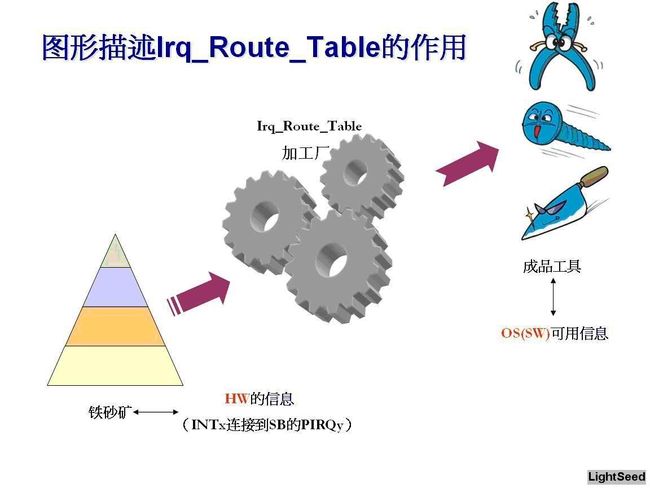

讓我們從圖片的角度來說明一下。見圖6.1

圖6.1

PCI IRQ Routing Table就像一個加工廠一樣,它把原始HW上的信息轉化成OS或者其他軟體可以識別的信息。

PCI IRQ Routing Table其實就像一個洋蔥一樣,它可以分成一層一層的信息。讓我們看看圖6.2就一目了然了。

圖6.2

7、PCI 中斷共用的處理

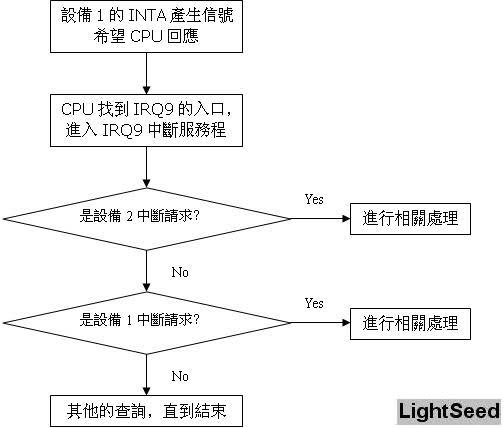

系統必須為每個中斷提供對應的中斷服務程式,當然這個程式的入口位址是在中斷向量錶中有填入的。本文給出在路由機制中,設備2 的INTA # 和設備3 的INTD # 共用,假設連接到了PIRQB。通常,如果多個設備使用同一個中斷請求線IRQi,則後登記的中斷入口會覆蓋先登記的服務程式的入口,先登記中斷的入口被存儲在後登記中斷的服務程式中,依次形成一條鏈。設備1的INTA發出中斷信號後,計算機經過一系列的過程會進入到IRQ9的中斷服務子程式(ISR)中, CPU 首先轉入最後登記入口的中斷服務中,(這裡就先進入到設備2的中斷服務程式中去)查詢該設備的中斷請求位元,若該位被置1,則執行該程式,否則找到下一個共用中斷的入口。(很明顯不是設備2,那麼)轉入下一個中斷服務程式執行,在該程式中再查詢該設備的中斷請求位元,判斷是否是該設備提出的中斷。(這個時候,設備1舉手說,終於輪到我啦,CPU大哥我要你幫我幹點事,好了後獎勵你一個香吻。。。)

我琢磨著畫個流程圖好理解點如下。

中斷流程圖

PS: 画这些图的时候真的花了不少时间,如果看的起我想转载的话,请说明出处。谢谢。