【我所认知的BIOS】->PCI enumerate

PCI enumerate

By Lightseed

10/06/2010

这篇文章本是很久以前写的,最近感觉比较懒惰今天才贴出来。近两年开始EFI越来越流行了,可以说逐渐有颠覆legacy bios的趋势。处于对知识的渴望和追求我也最近对EFI有了一些简单的了解,我打算在后续的文章中做一个关于EFI的专题,基于EDK来写blog应该不错。毕竟它是开源的嘛,如果以AMI的EFI来写文章我估计可能会涉及到商业机密的问题。希望能像网上那个《linux的那些事儿》那样做成一个一个的小专题。也希望如果有兴趣的朋友或者BIOSER能够和我联系,咱们一起研究哈。期待您的加入。。。先说说我的打算,PCI,IDE等这些比较重要的东西都各自做一个小专题。至于其他的嘛暂时还没想到。形式以code为例子直接加注或者说明。

另外之前有关于ACPI的文章,但是看了看,真的觉得没啥好说的,都是架构上的一些东西。估计要说的话,肯能也就要结合到实际的代码,我再斟酌斟酌用什么形式来表达出来会比较好。

1、PCI bridge的工作原理

在PCI的架构中,引入了PCI bridge的概念来扩展使用更多的PCI设备。其他的基本东西就不多讲了,开门见山先分析在PCI bridge处理总线上访问的原理。

1.1PCI总线的两种方式

PCI总线上有两种访问方式,分别是Type0和Type1。且bridge会通过比对自己的secondary bus number和subordinate bus number后做出后续的反应是type0还是type1的配置。

1.2详细说说type1,

当总线上CPU发出了一个访问PCI的动作,(假设说CPU用的是type0的方式,经过bridge1后被其配置成了type1)那么PCI bridge会去做比对,这时就出现了三种情况:

①如果此总线序号不在bridge的secondary bus number和subordinate bus number之间则忽略掉它。

②如果此总线序号与bridge的secondary bus number相同则将其转换成类型0 配置命令。

③如果此总线序号位于bridge的secondary bus number与subordinate bus number之间则将它不作改变的传递到二级总线接口中。

总之就是通过这中方式找到PCI总线上的对应的PCI设备,然后访问之~。

2、PCI 在枚举过程

2.1PCI的bus number必须遵循的一个规则

在我们当前的主板上面PCI to PCI bridge是基本上都会有的,整个PCI系统要能够正确地被解析访问到,PCI的bus number必须遵循一个规则:

All PCI buses located behind a PCI-PCI bridge must reside between the seondary bus number and the subordinate bus number.

有了这个规则,那么不管是BIOS还是linux在分配PCI bus number的时候就有规可循了。

2.2PCI bus number的分配过程详解

算法:不管是在Award bios还是在linux上都是深度优先。

概念:

Primary Bus Number:the bus number of the PCI bus which the primary interface of the bridge is connected.

Secondary bus number:the bus number of the PCI bus which the secondary interface of the bridge is connected.

Subordinate bus number:the bus number of the highest numbered PCI bus which is behind (or subordinate to) the bridge.

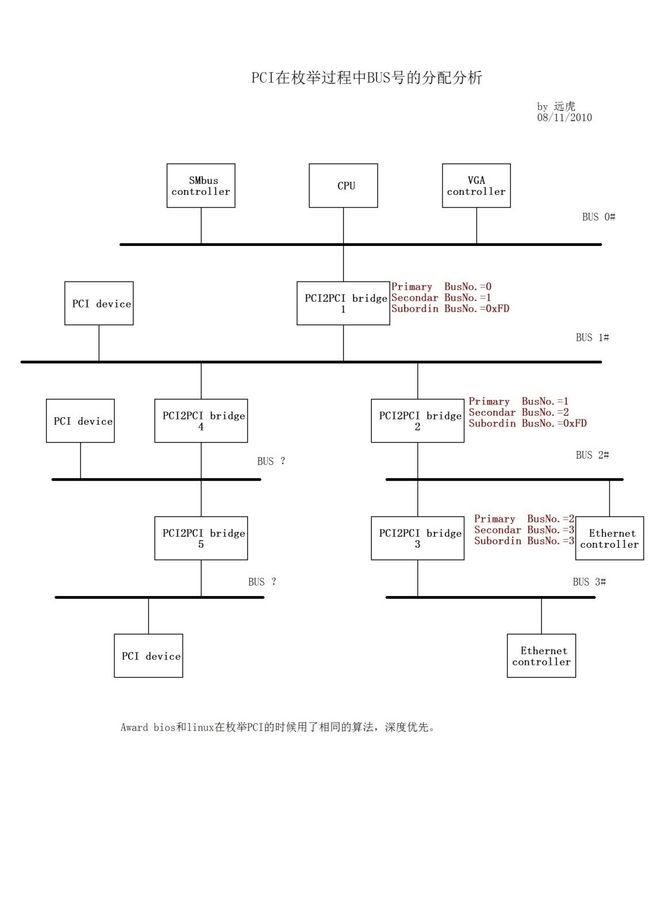

假设的PCI结构图1:

图1 假设的某平台上的PCI设备连接图

2.2.1PCI bus number初始化step1:

当在BUS 0#上第一个被扫到的PCI2PCI bridge1的时候(事实上也只有一个),primary bus number被填成0,鉴于深度优先的原则,那么这个bridge下的那条bus对应的bus number就应该是BUS 1#,为了能够继续往后面扫PCI device(不漏掉PCI bridge)所以把subordinate bus number设置为FDH。同样方式识别到了PCI2PCI bridge2。直到到了PCI2PCI bridge3的时候,发现在bridge3下下面已经没有其他的PCI bridge了。因此,才在PCI2PCI bridge3的相应寄存器里面填上,

Primary BusNo.=2

Secondar BusNo.=3

Subordinate BusNo.=3

然后分别填好bridge2的Subordinate bus number = 3。

见如图2

图2 PCI bus number初始化1

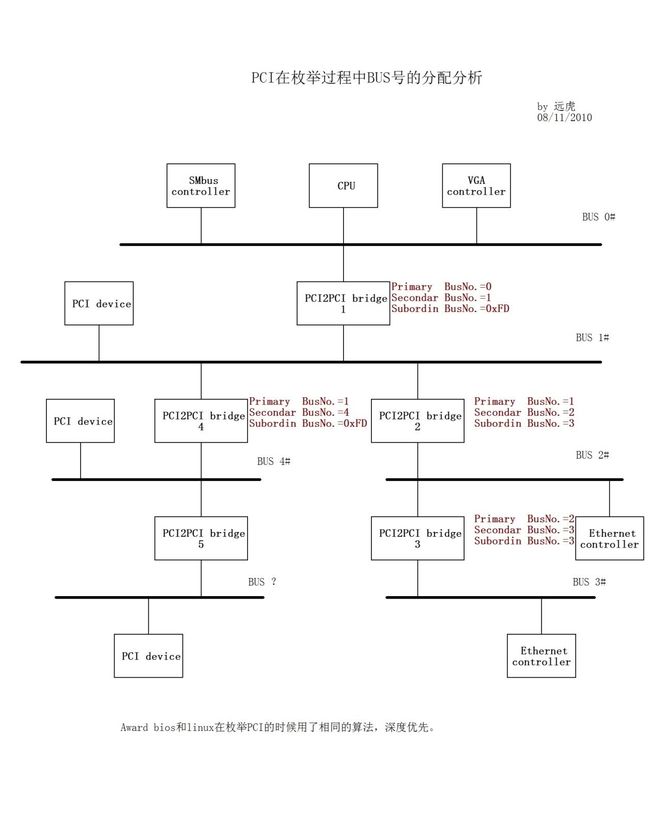

2.2.2 PCI bus number初始化step2:

当PCI2PCI bridge2后面的PCI bus number分配好了后,在bus 1#上面又被扫到了PCI2PCI bridge4,用同样的算法可以确定在这个bridge后面的PCI bus number了。

此时,PCI2PCI bridge4的相应寄存器被初始化成:

Primary BusNo.=2

Secondar BusNo.=3

Subordinate BusNo.=0xFD

见图3

图3

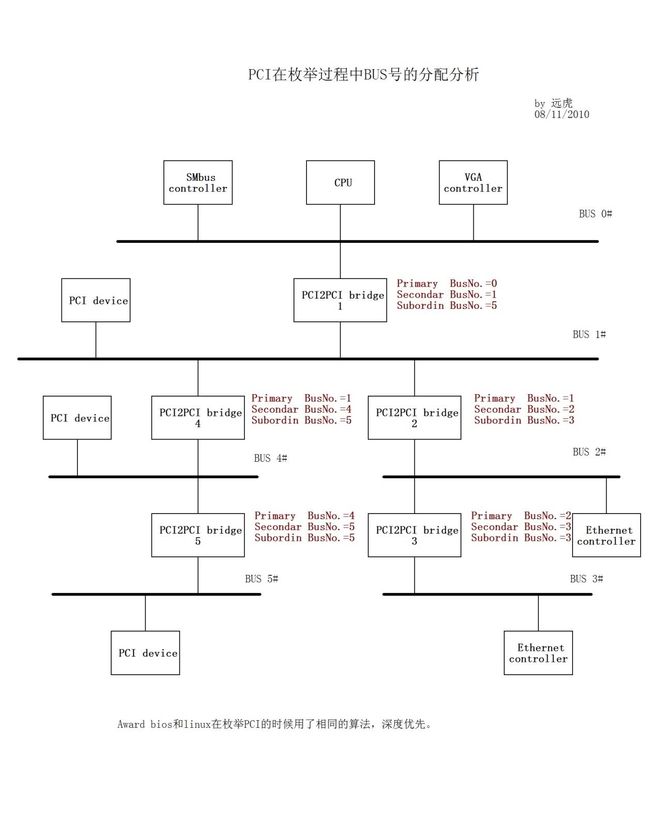

2.2.3 PCI bus number初始化step2:

当PCI2PCI bridge5后面已经没有挂PCI设备的时候,此时整个PCI系统上的所有bus number都可以被确定了。在初始化PCI2PCI bridge5的三个寄存器后,

Primary BusNo.=4

Secondar BusNo.=5

Subordinate BusNo.=5

然后分别回填PCI2PCI bridge4和PCI2PCI bridge1的Subordinate bus number寄存器。

见图4

图4 PCI bus number的完整分配过程

3、PCI的资源分配

资源的问题,就不对赘述了。只是这里提一下,是因为在分配bus number的过程中,BIOS其实就已经把每个PCI设备需要的resources都已经记录下来了。然后在bus number分配好了后,后续就好进行资源分配了。

4、PCI bridge的address decode

4.1Subtractive decode

如果bridge支持subtractive decode,当在primary面没有找到另外的相应设备,则4 个周期的超时之后,认为在当前总线上没有找到相应设备。产生从primary 面到secondary 面的响应。如果此bridge不支持subtractive decode的功能,则bridge不会响应并且不会传输数据,而是调用中断提示错误。

这个功能,主要是针对PCI to ISA bridge的。如果这个功能不打开的话,那么PCI to ISA bridge下面的ISA设备就不能正常work。因为一般情况下前面4K的IO空间系统都是没有做任何操作的。这个和PCI的IO操作不一样。所以需要这么一种模式来做。比如ITE8888。

4.2Positive decode

如果数据处理中找到相应的设备地址在“bridge windows”中的话,那么bridge使用positive decode立即响应,从primary面到secondary面正向译码。

4.3Negative decode

在bridge的正向译码窗口外从secondary面到primary 面的地址译码。这种译码发生在bridge的secondary面的设备要访问primary面的设备的时候,而传输的地址数据不在window中定义。如果地址在window 中范围内,则允许同一总线中的对应设备处理(transaction)---peer-to-peer transactions 而不经过bridge。如图5

图 5 Address decoding types

图6 Secondary side bridge rules

4.4PCI-PCI Bridge的类型

在系统中支持3 种类型的p2p bridge。这些类型是:

①只支持 subtractive的pci-pci bridge

②只支持 positive的p2p bridge

③Subtractive类型p2p bridge

Subtractive-only PCI-to-PCI bridge

这种类型的bridge 没有windows 的概念的pci-pci bridge。只能实现通过subtractive decode方式访问pci bridge 的secondary侧的地址资源。不支持传输(transactions)的开始和终止都在secondary侧的pci总线上。点对点(peer to peer)的传输(transactions)是不支持的。

注:此种类型的bridge在pci-pci bridge的spec中没有定义。

Positive-only PCI-to-PCI bridge

这种类型的bridge只能通过positive decodes 来实现源自桥的primary侧的传输。Subtractive decode是不支持的。由于此种桥具有bridge window,所以能实现点对点(peer to peer)的传输(transactions)。同时还能支持negative decode由于此类桥不支持subtractive decodes ,所以positive-only p2p bridge 不能寻址secondary侧的设备。

Subtractive PCI-to-PCI bridge

这种类型的bridge具有bridge windows的功能,而且支持positive 、subtractive decode。如下图。因为此类桥有positive decode window,可以通过window 实现在桥的secondary侧的peer-peer 的transactions。同时也可以实现negative decode过程。由于这类bridge支持subtractive decodes,那么就能支持桥的secondary侧的legacy设备的寻址。

Reference,

1. PCI-to-PCI Bridge Architecture Specification, revision 1.1

2.http://tldp.org/LDP/tlk/dd/pci.html#pci-pci-config-eg-4