TTL和CMOS逻辑器件

TTL和CMOS逻辑器件

逻辑器件的分类方法有很多,下面以逻辑器件的功能、工艺特点和逻辑电平等方法来进行简单描述。

1:TTL和CMOS器件的功能分类

按功能进行划分,逻辑器件可以大概分为以下几类: 门电路和反相器、选择器、译码器、计数器、寄存器、触发器、锁存器、缓冲驱动器、收发器、总线开关、背板驱动器等。

1)门电路和反相器

逻辑门主要有与门74X08、与非门74X00、或门74X32、或非门74X02、异或门74X86、反相器74X04等。

2)选择器

选择器主要有2-1、4-1、8-1选择器74X157、74X153、74X151等。

3)编/译码器

编/译码器主要有2/4、3/8和4/16译码器74X139、74X138、74X154等。

4)计数器

计数器主要有同步计数器74X161和异步计数器74X393等。

5)寄存器

寄存器主要有串-并移位寄存器74X164和并-串寄存器74X165等。

6)触发器

触发器主要有J-K触发器、带三态的D触发器74X374、不带三态的D触发器74X74、施密特触发器等。

7)锁存器

锁存器主要有D型锁存器74X373、寻址锁存器74X259等。

8)缓冲驱动器

缓冲驱动器主要有带反向的缓冲驱动器74X240和不带反向的缓冲驱动器74X244等。

9)收发器

收发器主要有寄存器收发器74X543、通用收发器74X245、总线收发器等。

10)总线开关

总线开关主要包括总线交换和通用总线器件等。

11)背板驱动器

背板驱动器主要包括TTL或LVTTL电平与GTL/GTL+(GTLP)或BTL之间的电平转换器件。

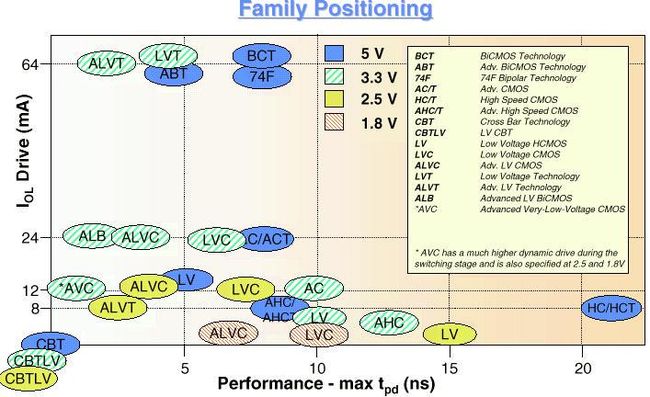

2:TTL和MOS逻辑器件的工艺分类特点

按工艺特点进行划分,逻辑器件可以分为Bipolar、CMOS、BiCMOS等工艺,其中包括器件系列有:

- Bipolar(双极)工艺的器件有: TTL、S、LS、AS、F、ALS。

- CMOS工艺的器件有: HC、HCT、CD40000、ACL、FCT、LVC、LV、CBT、ALVC、AHC、AHCT、CBTLV、AVC、GTLP。

- BiCMOS工艺的器件有: BCT、ABT、LVT、ALVT。

3:TTL和CMOS逻辑器件的电平分类特点

TTL和CMOS的电平主要有以下几种:5VTTL、5VCMOS(Vih≥0.7*Vcc,Vil≤0.3*Vcc)、3.3V电平、2.5V电平等。

- 5V的逻辑器件

5V器件包含TTL、S、LS、ALS、AS、HCT、HC、BCT、74F、ACT、AC、AHCT、AHC、ABT等系列器件 - 3.3V及以下的逻辑器件

包含LV的和V 系列及AHC和AC系列,主要有LV、AHC、AC、ALB、LVC、ALVC、LVT等系列器件。

4:包含特殊功能的逻辑器件

A.总线保持功能(Bus hold)

由内部反馈电路保持输入端最后的确定状态,防止因输入端浮空的不确定而导致器件振荡自激损坏;输入端无需外接上拉或下拉电阻,节省PCB空间,降低了器件成本开销和功耗。ABT、LVT、ALVC、ALVCH、ALVTH、LVC、GTL系列器件有此功能。命名特征为附加了“H”如:74ABTH16244。

图2:总线保持功能图 图3:串行阻尼电阻图

B.串联阻尼电阻(series damping resistors)

输出端加入串联阻尼电阻可以限流,有助于降低信号上冲/下冲噪声,消除线路振铃,改善信号质量。具有此特征的ABT、LVC、LVT、ALVC系列器件在命名中加入了“2”或“R”以示区别,如ABT162245,ALVCHR162245。对于单向驱动器件,串联电阻加在其输出端,命名如SN74LVC2244;对于双向的收发器件,串联电阻加在两边的输出端,命名如SN74LVCR2245。

C.上电/掉电三态(PU3S,Power up/power down 3-state)

即热拔插性能。上电/掉电时器件输出端为三态,Vcc阀值为2.1V;应用于热拔插器件/板卡产品,确保拔插状态时输出数据的完整性。多数ABT、LVC、LVT、LVTH系列器件有此特征。

D.ABT 器件(Advanced BiCMOS Technology)

结合了CMOS器件(如HC/HCT、LV/LVC、ALVC、AHC/AHCT)的高输入阻抗特性和双极性器件(Bipolar,如TTL、LS、AS、ALS)输出驱动能力强的特点。包括ABT、LVT、ALVT等系列器件,应用于低电压,低静态功耗环境。

E.Vcc/GND对称分布

16位Widebus器件的重要特征,对称配置引脚,有利于改善噪声性能。AHC/AHCT、AVT、AC/ACT、CBT、LVT、ALVC、LVC、ALB系列16位Widebus器件有此特征。

F.分离轨器件(Split-rail)

即双电源器件,具有两种电源输入引脚VccA和VccB,可分别接5V或3.3V电源电压。如ALVC164245、LVC4245等,命名特征为附加了“4”。

5:逻辑器件的使用指南

1. 多余不用输入管脚的处理

在多数情况下,集成电路芯片的管脚不会全部被使用。例如74ABT16244系列器件最多可以使用16路I/O管脚,但实际上通常不会全部使用,这样就会存在悬空端子。所有数字逻辑器件的无用端子必须连接到一个高电平或低电平,以防止电流漂移(具有总线保持功能的器件无需处理不用输入管脚)。究竟上拉还是下拉由实际器件在何种方式下功耗最低确定。 244、16244经测试在接高电平时静态功耗较小,而接地时静态功耗较大,故建议其无用端子处理以通过电阻接电源为好,电阻值推荐为1~10K。

2. 选择板内驱动器件的驱动能力,速度,不能盲目追求大驱动能力和高速的器件,应该选择能够满足设计要求,同时有一定的余量的器件,这样可以减少信号过冲,改善信号质量。 并且在设计时必须考虑信号匹配。

3. 在对驱动能力和速度要求较高的场合,如高速总线型信号线,可使用ABT、LVT系列。板间接口选择ABT16244/245或LVTH16244/245,并在母板两端匹配,在不影响速度的条件下与母板接口尽量串阻,以抑制过冲、保护器件,典型电阻值为10- 200Ω左右,另外,也可以使用并接二级管来进行处理,效果也不错,如1N4148等(抗冲击较好)。

4. 在总线达到产生传输线效应的长度后,应考虑对传输线进行匹配,一般采用的方式有始端匹配、终端匹配等。

始端匹配是在芯片的输出端串接电阻,目的是防止信号畸变和地弹反射,特别当总线要透过接插件时,尤其须做始端匹配。 内部带串联阻尼电阻的器件相当于始端匹配,由于其阻值固定,无法根据实际情况进行调整,在多数场合对于改善信号质量收效不大,故此不建议推荐使用。始端匹配推荐电阻值为10~51 Ω,在实际使用中可根据IBIS模型模拟仿真确定其具体值。

由于终端匹配网络加重了总线负载,所以不应该因为匹配而使Buffer的实际驱动电流大于驱动器件所能提供的最大Source、Sink电流值。

应选择正确的终端匹配网络,使总线即使在没有任何驱动源时,其线电压仍能保持在稳定的高电平。

5. 要注意高速驱动器件的电源滤波。如ABT、LVT系列芯片在布线时,建议在芯片的四组电源引脚附近分别接0.1 μ或0.01 μ电容。

6. 可编程器件任何电源引脚、地线引脚均不能悬空;在每个可编程器件的电源和地间要并接0.1uF的去耦电容,去耦电容尽量靠近电源引脚,并与地形成尽可能小的环路。

7. 收发总线需有上拉电阻或上下拉电阻,保证总线浮空时能处于一个有效电平,以减小功耗和干扰。

8. 373/374/273等器件为工作可靠,锁存时钟输入建议串入10-200欧电阻。

9. 时钟、复位等引脚输入往往要求较高电平,必要时可上拉电阻。

10. 注意不同系列器件是否有带电插拔功能及应用设计中的注意事项。

11. 注意电平接口的兼容性。 选用器件时要注意电平信号类型,对于有不同逻辑电平互连的情况,请遵守本规范的相应的章节的具体要求。

12. 在器件工作过程中,为保证器件安全运行,器件引脚上的电压及电流应严格控制在器件手册指定的范围内。逻辑器件的工作电压不要超出它所允许的范围。

13. 逻辑器件的输入信号不要超过它所能允许的电压输入范围,不然可能会导致芯片性能下降甚至损坏逻辑器件。

14. 对开关量输入应串电阻,以避免过压损坏。

15. 对于带有缓冲器的器件不要用于线性电路,如放大器。