DM8168的互连与内存映射

DM8168是多处理器系统,每个子系统或处理器都有自己的内存和内存映射的寄存器。为了简化软件开发,使用一个统一的内存映射,这样从所有总线Master方来看芯片资源具有了一致性。

整个系统内存映射被划分为4个1GB的quadrant,用于目标地址空间的定位。4个quadrant:Q0、Q1、Q2和Q3总计4-GB 的32位地址空间。(HDVPSS包括一个第33位地址位,用于附加的4GB地址范围,这用作虚拟寻址和非物理内存寻址),在每个quadrant内部,系统目标以4MB为边界进行映射(除了EDMA目标,它降低到1MB范围)。

DM8168是使用一种互连技术,将多处理器和子系统连接到一起的。因此我们有必要介绍一下这个互连技术。

所谓互连,就是模块之间实现存取的一种技术,先要理解一些基本概略:

l Initiator(发起者):向互连发起读写请求。典型如:处理器、DMA。

l Target(目标):不同与Initiator,它不向互连发出读写请求,但是它能响应这些请求。它还可以向系统产生中断和DMA请求。典型如:外设、内存控制器

l Agent(代理):一个模块与互连的连接是通过代理的,它是模块与互连之间的适配器(有时可以配置)。一个Target通过一个Target代理(TA)与互连连接,Initiator通过Initiator代理(IA)与互连连接。

l Interconnect(互连):应该包含译码、路由、仲裁等逻辑,才能实现连接在其上的多个Initiator和多个Target之间的互连。

DM8168的互连是基于一种分层架构(L3,L4),如下图。注意箭头并不是表示数据流的方向,而是表示Master/Slave(或者Initiator/Target)关系。

图5-1 互连概貌

图5-2 L4结构

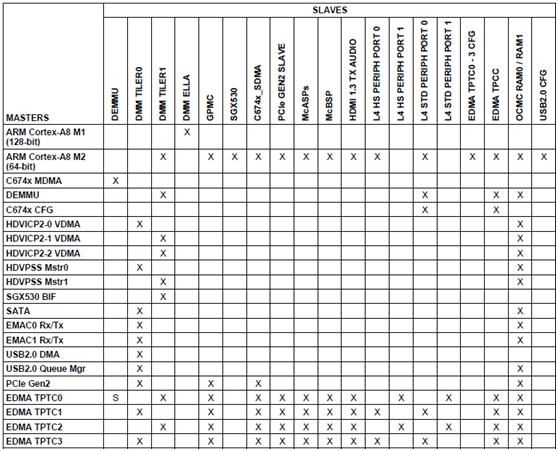

表5-1 L3 Master/Slave互连

(1) X = 互连存在;S = 可裁减的通道。Non-DEMMU可存取的目标(如C674x SDMA)总是直接映射。

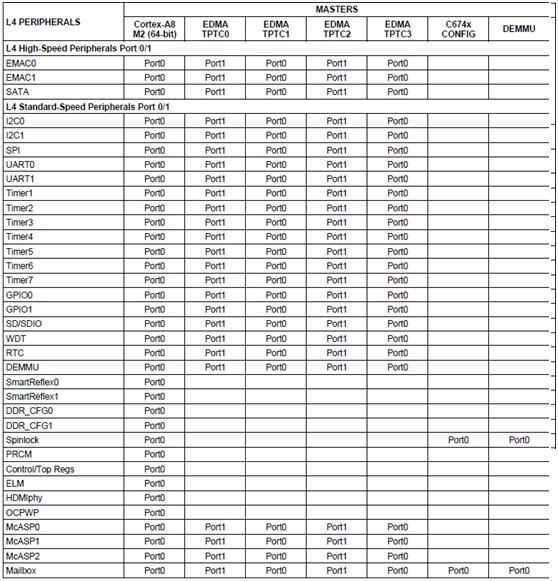

表5-2 L4外设连接

(1)X,Port0,Port1 = 连接存在

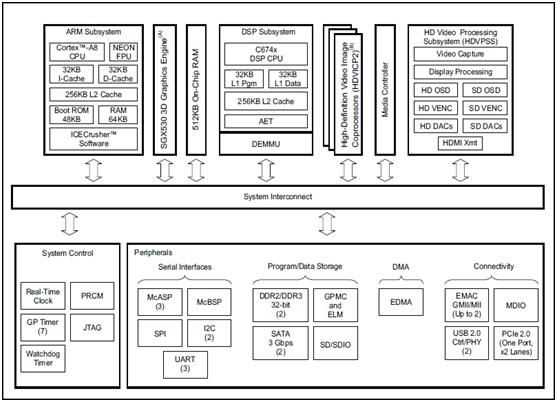

DM816x的系统框图如下。我们以Cortex-A8和C674x两个子系统为例,来看DM816x是如何管理内存。

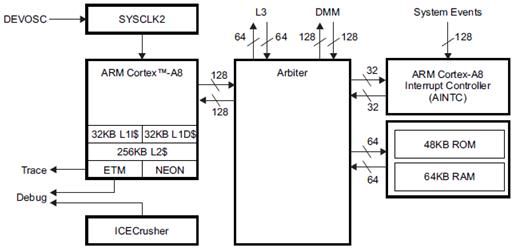

1.Cortex-A8

Cortex-A8的结构框图如下:

从图中我们可以看到:

l Cortex-A8内部有48KB ROM 和64KB RAM。

l Cortex与其它模块互连是通过DMM和L3端口。

n Cortex-A8通过DMM端口(128bit宽)直接存取DDR。

n Cortex-A8通过L3互连端口(64bit)存取芯片的其他模块。

Cortex-A8地址映射:

| 块名 |

起始地址 |

结束地址 |

尺寸 |

描述 |

| Boot Space |

0x0000 0000 |

0x000F FFFF |

1MB |

Boot Space |

| L3 目标空间 |

0x0000 0000 |

0x1FFF FFFF |

512MB |

GPMC |

| 0x2000 0000 |

0x2FFF FFFF |

256MB |

PCIe Gen2 Targets |

|

| 0x3000 0000 |

0x3FFF FFFF |

256MB |

Reserved |

|

| 内部ROM(1) |

0x4000 0000 |

0x4001 FFFF |

128KB |

Reserved |

| 0x4002 0000 |

0x4002 BFFF |

48KB |

ROM Public |

|

| 0x4002 C000 |

0x40F FFFF |

848KB |

Reserved |

|

| Reserved(1) |

0x4010 0000 |

0x401F FFFF |

1MB |

Reserved |

| Reserved(1) |

0x4020 0000 |

0x402E FFFF |

960KB |

Reserved |

| Reserved(1) |

0x402F 0000 |

0x402F FFFF |

64KB |

SRAM(64KB) Secure/Public |

| L3目标空间 |

0x4030 0000 |

0x4033 FFFF |

256MB |

OCMC SRAM |

| 0x4034 0000 |

0x403F FFFF |

768KB |

Reserved |

|

| 0x4040 0000 |

0x4043 FFFF |

256KB |

OCMC SRAM |

|

| 0x4044 0000 |

0x404F FFFF |

768KB |

Reserved(OCMC RAM1) |

|

| 0x4050 0000 |

0x407F FFFF |

3MB |

Reserved |

|

| 0x4080 0000 |

0x4083 FFFF |

256KB |

C674x UMAP0(L2 RAM) |

|

| 0x4084 0000 |

0x40DF FFFF |

5888KB |

Reserved |

|

| 0x40E0 0000 |

0x40E0 7FFF |

32KB |

C674x L1P Cache/RAM |

|

| 0x40E0 8000 |

0x40EF FFFF |

992KB |

Reserved |

|

| 0x40F0 0000 |

0x40F0 7FFF |

32KB |

C674x L1D Cache/RAM |

|

| 0x40F0 8000 |

0x40FF FFFF |

992KB |

Reserved |

|

| 0x4100 0000 |

0x41FF FFFF |

16MB |

Reserved |

|

| 0x4200 0000 |

0x43FF FFFF |

32MB |

Reserved |

|

| 0x4400 0000 |

0x44BF FFFF |

12MB |

L3配置寄存器 |

|

| 0x44C0 0000 |

0c45FF FFFF |

20MB |

Reserved |

|

| 0x4600 0000 |

0x463F FFFF |

4MB |

McASP0 |

|

| 0x4640 0000 |

0x467F FFFF |

4MB |

McASP01 |

|

| 0x4680 0000 |

0x46BF FFFF |

4MB |

McASP02 |

|

| 0x46C0 0000 |

0x46FF FFFF |

4MB |

HDMI1.3 Tx |

|

| 0x4700 0000 |

0x473F FFFF |

4MB |

McBsp |

|

| 0x4740 0000 |

0x477F FFFF |

4MB |

USB2.0寄存器/CPPI |

|

| 0x4780 0000 |

0x47BF FFFF |

4MB |

Reserved |

|

| 0x47C0 0000 |

0x47FF FFFF |

4MB |

Reserved |

|

| 0x4800 0000 |

0x481F FFFF |

2MB |

L4标准外设域 |

|

| ARM Subsystem INTC(1) |

0x4820 0000 |

0x4820 FFFF |

4KB |

仅由Contex-A8存取 |

| Reserved(1) |

0x4820 1000 |

0x4823 FFFF |

252KB |

仅由Contex-A8存取 |

| MPUSS config register(1) |

0x4824 0000 |

0x4824 FFFF |

4KB |

仅由Contex-A8存取 |

| Reserved(1) |

0x4824 1000 |

0x4827 FFFF |

252KB |

仅由Contex-A8存取 |

| Reserved(1) |

0x4828 1000 |

0x482F FFFF |

508KB |

仅由Contex-A8存取 |

| L3目标空间 |

0x4830 0000 |

0x48FF FFFF |

13MB |

L4标准外设域 |

| 0x4900 0000 |

0x490F FFFF |

1MB |

EDMA TPCC寄存器 |

|

| 0x4910 0000 |

0x497F FFFF |

7MB |

Reserved |

|

| 0x4980 0000 |

0x498F FFFF |

1MB |

EDMA TPCC0寄存器 |

|

| 0x4990 0000 |

0x499F FFFF |

1MB |

EDMA TPCC1寄存器 |

|

| 0x49A0 0000 |

0x49AF FFFF |

1MB |

EDMA TPCC2寄存器 |

|

| 0x49B0 0000 |

0x49BF FFFF |

1MB |

EDMA TPCC3寄存器 |

|

| 0x49C0 0000 |

0x49FF FFFF |

4MB |

Reserved |

|

| 0x4A00 0000 |

0x4AFF FFFF |

16MB |

L4高速外设域 |

|

| 0x4B00 0000 |

0x4BFF FFFF |

16MB |

EMU子系统区域 |

|

| 0x4C00 0000 |

0x4CFF FFFF |

16MB |

DDR EMIF0配置寄存器(2) |

|

| 0x4D00 0000 |

0x4DFF FFFF |

16MB |

DDR EMIF1配置寄存器(2) |

|

| 0x4E00 0000 |

0x4FFF FFFF |

32MB |

DDR DMM配置寄存器(2) |

|

| 0x5000 0000 |

0x50FF FFFF |

16MB |

GMPC配置寄存器 |

|

| 0x5100 0000 |

0x51FF FFFF |

16MB |

PCIE配置寄存器 |

|

| 0x5200 0000 |

0x52FF FFFF |

16MB |

Reserved |

|

| 0x5300 0000 |

0x53FF FFFF |

16MB |

HDVICP2-2 Host端口 |

|

| 0x5400 0000 |

0x54FF FFFF |

16MB |

HDVICP2-2 SL2端口 |

|

| 0x5500 0000 |

0x55FF FFFF |

16MB |

Reserved |

|

| 0x5600 0000 |

0x56FF FFFF |

16MB |

SGX530从端口 |

|

| 0x5700 0000 |

0x57FF FFFF |

16MB |

Reserved |

|

| 0x5800 0000 |

0x58FF FFFF |

16MB |

HDVICP2-0 Host端口 |

|

| 0x5900 0000 |

0x59FF FFFF |

16MB |

HDVICP2-0 SL2端口 |

|

| 0x5A00 0000 |

0x5AFF FFFF |

16MB |

HDVICP2-1 Host端口 |

|

| 0x5B00 0000 |

0x5BFF FFFF |

16MB |

HDVICP2-1 SL2端口 |

|

| 0x5C00 0000 |

0x5CFF FFFF |

32Mb |

Reserved |

|

| 0x5E00 0000 |

0x5FFF FFFF |

32MB |

Reserved |

|

| 0x6000 0000 |

0x7FFF FFFF |

512MB |

TILER窗口 |

|

| DDR EMIF0/1 SDRAM(3)(4) |

0x8000 0000 |

0xBFFF FFFF |

1GB |

DDR |

| DDR EMIF0/1 SDRAM(3)(4) |

0xC000 0000 |

0xFFFF FFFF |

1GB |

DDR |

(1) 黑体字部分表示这部分在Cortex-A8内部

(2) 这些存取通过DDR DMM TILER端口。DDR DMM内部分开寻址DDR EMIF和DDR DMM控制寄存器的地址范围

(3) 这些地址路由到与DDR DMM ELLA端口直接相连的Master0端口

(4) DDR EMIF0和DDR EMIF1地址可以连续或BANK交织,取决于DDR DMM配置

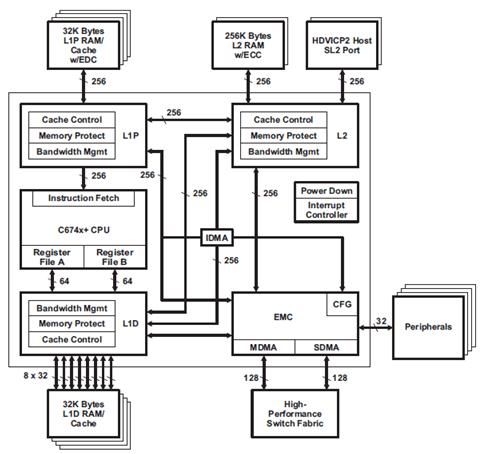

2.C674x

C674x DSP Megamodule框图如下:

从图中,我们看到:

l EMC(Extend Memory Controller)是一个桥,将Megamodule与芯片的其他部分连接起来。它包括3个端口:

n 配置端口(CFG):这个端口提供对内存映射的寄存器(这些寄存器控制不同的外设和资源)的存取,但并不支持对CPU和Megamodule内部的内存映射寄存器的存取。CFG总线总是32bit宽,总是应该使用32bit load/store指令或者IDMA来存取

n Master DMA(MDMA):MDAM提供对MegaModule外部资源的存取,传输的发起者是Megamodule(也就是说这些传输,Megamodule是Master)。MDMA常用来做为CPU/Cache对L2以外的内存的存取。这些存取可能是以对系统内存的Cache Line Allocate、Writeback、Non-Cacheable Load和Store形式。

n Slave DMA(SDMA):SDMA用于Megamodule外部的其它Masters对Megamodule内部资源的存取。这些其它的Master如:DMA控制器、HPI等等,也就是说这些传输是Megamodule外部Master发起的,而Megamodule在交易中是处于Slave地位。

n 所有的MDMA存取都是通过DEMMU来路由做地址翻译的;CFG总是用于存取连L4外设。

l 还有3个Master端口,用于直接存取HDVICP2 SL2(仅HDVICP2-0和HDVICP2-1)内存。

C6474x DSP通过MDMA端口进行的存取是通过DSP/EDMA内存管理单元(DEMMU)来路由的,DEMMU重新映射物理系统地址。这样做可以保护ARM Cortex A8内存区域避免被C674x代码意外破坏,并允许在用户空间里直接定位buffer而不需要在ARM和DSP之间进行翻译。

另外,EDMA TC0进行的存取可以选择通过DEMMU来路由,这允许DSP使用EDMA 通道0进行传输的时候,仅使用相关Buffer的已知虚拟地址来执行传输。EDMA_TC通过控制模块里的MMU_CFG寄存器来使能/禁止DSP/EDMA MMU。

表2-31C674x内存映射

| 区域名称 |

起始地址 |

结束地址 |

尺寸 |

描述 |

| 保留(注1) |

0x0000 0000 |

0x003F FFFF |

4MB |

保留 |

| UMAP1(注1) |

0x0040 0000 |

0x0043 FFFF |

256KB |

C674x UMAP1(HDVICP2-0 SL2) |

| 保留(UMAP1)(注1) |

0x0044 0000 |

0x004F FFFF |

768KB |

保留 |

| UMAP1(注1) |

0x0050 0000 |

0x0053 FFFF |

256KB |

C674x UMAP (HDVICP2-1 SL2) |

| 保留(UMAP1) (注1) |

0x0054 0000 |

0x005F FFFF |

768KB |

保留 |

| 保留(注1) |

0x0060 0000 |

0x007F FFFF |

2MB |

保留 |

| L2 SRAM(注1) |

0x0080 0000 |

0x0083 FFFF |

256KB |

C674x UMAP0(L2 RAM) |

| 保留(注1) |

0x0084 0000 |

0x00DF FFFF |

5888KB |

保留 |

| L1P SRAM(注1) |

0x00E0 0000 |

0x00E0 7FFF |

32KB |

C674x L1P Cache/RAM |

| 保留(注1) |

0x00E0 8000 |

0x00EF FFFF |

992KB |

保留 |

| L1D SRAM(注1) |

0x00F0 0000 |

0x00F0 7FFF |

32KB |

C674x L1D Cache/RAM |

| 保留(注1) |

0x00F0 8000 |

0x017F FFFF |

9184KB |

保留 |

| 内部CFG(注2、3) |

0x0180 0000 |

0x01BF FFFF |

4MB |

C674x内部CFG寄存器 |

| 保留(注3) |

0x01C0 0000 |

0x07FF FFFF |

100MB |

保留 |

| L4标准域(注3) |

0x0800 0000 |

0x08FF FFFF |

16MB |

外设域(见表2-27) |

| EDMA TPCC(注3) |

0x0900 0000 |

0x090F FFFF |

1MB |

EDMA TPCC寄存器 |

| 保留(注3) |

0x0910 0000 |

0x097F FFFF |

7MB |

保留 |

| EDMA TPTC0(注3) |

0x0980 0000 |

0x098F FFFF |

1MB |

EDMA TPTC0寄存器 |

| EDMA TPTC1(注3) |

0x0990 0000 |

0x099F FFFF |

1MB |

EDMA TPTC1寄存器 |

| EDMA TPTC2(注3) |

0x09A0 0000 |

0x09AFFFFF |

1MB |

EDMA TPTC2寄存器 |

| EDMA TPTC3(注3) |

0x09B0 0000 |

0x09BF FFFF |

1MB |

EDMA TPTC3寄存器 |

| 保留(注3) |

0x09C0 0000 |

0x09FF FFFF |

4MB |

保留 |

| L4高速域(注3) |

0x0A00 0000 |

0x0AFF FFFF |

16MB |

外设域(见表2-28) |

| 保留(注3) |

0x0B00 0000 |

0x0FFF FFFF |

80MB |

保留 |

| C674x L1/L2(注4) |

0x1000 0000 |

0x10FF FFFF |

16MB |

C674x内部全局地址 |

| MDMA(注5) |

0x1100 0000 |

0xFFFF FFFF |

3824MB |

DEMMU映射L3域 |

注1:地址0x0000 0000到0x017F FFFF对C674x器件是在内部。

注2:地址0x0180 0000到0x01BF FFFF保留作为C674x内部CFG寄存器。

注3:地址0x01C0 0000到0x0FFF FFFF映射倒C674x CFG总线。

注4: 地址0x1000 0000到0x10FF FFFF映射倒C674x内部地址0x0000 0000 到 0x00FF FFFF。

注5:这些存取通过DEMMU路由,DEMMU通过页表将这些地址翻译到物理L3地址。

3.L3内存映射

L3高性能互连是基于片上网络(Network-on-Chip:NoC)互连基础架构,NoC使用一个内部基于包的通讯规程,用作前向(读命令、带数据负荷的写命令)和后向(带数据负荷的读响应、写响应)交易,所有公开的NoC互连接口(对目标和发起者)满足OCP IP2.2参考标准。

表2-26显示了DM8168的L3的内存映射,表中呈现了L3基础架构使用的物理地址,某些处理器(如Cortex A8 ARM、C674x DSP)可以通过内部或外部MMU重新将这些目标重新映射到不同的虚拟地址。没有MMU的处理器和其他总线Master使用这些物理地址存取L3区域,注意并不是所有MASTER都会对L3所有区域进行存取,而仅仅是那些有明确连接的存取,如表5-1显示的那些才可以。在5.2节列出了连接到L4外设端口的外设。任何发起者如果企图存取一个没有连接的目标, L3互连会返回一个地址空洞错误。

表2-26 L3内存映射

| QUAD |

块名 |

起始地址 |

结束地址 |

尺寸 |

描述 |

| Q0 |

GPMC |

0x0000 0000 |

0x1FFF FFFF |

512MB |

GPMC |

| Q0 |

PCIe Gen2 |

0x2000 0000 |

0x2FFF FFFF |

256MB |

PCIe Gen2 Targets |

| Q0 |

Reserved |

0x3000 0000 |

0x3FFF FFFF |

256MB |

Reserved |

| Q1 |

Reserved |

0x4000 0000 |

0x402F FFFF |

3MB |

Reserved |

| Q1 |

L3 OCMC0 |

0x4030 0000 |

0x4033 FFFF |

256MB |

OCMC SRAM |

| Q1 |

Reserved |

0x4034 0000 |

0x403F FFFF |

768KB |

Reserved |

| Q1 |

L3 OCMC1 |

0x4040 0000 |

0x4043 FFFF |

256KB |

OCMC SRAM |

| Q1 |

Reserved |

0x4044 0000 |

0x404F FFFF |

768KB |

Reserved(OCMC RAM1) |

| Q1 |

Reserved |

0x4050 0000 |

0x407F FFFF |

3MB |

Reserved |

| Q1 |

C674x |

0x4080 0000 |

0x4083 FFFF |

256KB |

C674x UMAP0(L2 RAM) |

| Q1 |

Reserved |

0x4084 0000 |

0x40DF FFFF |

5888KB |

Reserved |

| Q1 |

C674x |

0x40E0 0000 |

0x40E0 7FFF |

32KB |

C674x L1P Cache/RAM |

| Q1 |

Reserved |

0x40E0 8000 |

0x40EF FFFF |

992KB |

Reserved |

| Q1 |

C674x |

0x40F0 0000 |

0x40F0 7FFF |

32KB |

C674x L1D Cache/RAM |

| Q1 |

Reserved |

0x40F0 8000 |

0x40FF FFFF |

992KB |

Reserved |

| Q1 |

Reserved |

0x4100 0000 |

0x41FF FFFF |

16MB |

Reserved |

| Q1 |

Reserved |

0x4200 0000 |

0x43FF FFFF |

32MB |

Reserved |

| Q1 |

L3 CFG Regs |

0x4400 0000 |

0x44BF FFFF |

12MB |

L3配置寄存器 |

| Q1 |

Reserved |

0x44C0 0000 |

0c45FF FFFF |

20MB |

Reserved |

| Q1 |

McASP0 |

0x4600 0000 |

0x463F FFFF |

4MB |

McASP0 |

| Q1 |

McASP1 |

0x4640 0000 |

0x467F FFFF |

4MB |

McASP01 |

| Q1 |

McASP2 |

0x4680 0000 |

0x46BF FFFF |

4MB |

McASP02 |

| Q1 |

HDMI1.3 Tx |

0x46C0 0000 |

0x46FF FFFF |

4MB |

HDMI1.3 Tx |

| Q1 |

McBsp |

0x4700 0000 |

0x473F FFFF |

4MB |

McBsp |

| Q1 |

USB2.0 |

0x4740 0000 |

0x477F FFFF |

4MB |

USB2.0寄存器/CPPI |

| Q1 |

Reserved |

0x4780 0000 |

0x47BF FFFF |

4MB |

Reserved |

| Q1 |

Reserved |

0x47C0 0000 |

0x47FF FFFF |

4MB |

Reserved |

| Q1 |

L4 Standard domain |

0x4800 0000 |

0x48FF FFFF |

16MB |

标准外设域 |

| Q1 |

EDMA TPCC |

0x4900 0000 |

0x490F FFFF |

1MB |

EDMA TPCC寄存器 |

| Q1 |

Reserved |

0x4910 0000 |

0x497F FFFF |

7MB |

Reserved |

| Q1 |

EDMA TPTC0 |

0x4980 0000 |

0x498F FFFF |

1MB |

EDMA TPCC0寄存器 |

| Q1 |

EDMA TPTC1 |

0x4990 0000 |

0x499F FFFF |

1MB |

EDMA TPCC1寄存器 |

| Q1 |

EDMA TPTC2 |

0x49A0 0000 |

0x49AF FFFF |

1MB |

EDMA TPCC2寄存器 |

| Q1 |

EDMA TPTC3 |

0x49B0 0000 |

0x49BF FFFF |

1MB |

EDMA TPCC3寄存器 |

| Q1 |

Reserved |

0x49C0 0000 |

0x49FF FFFF |

4MB |

Reserved |

| Q1 |

L4 High-Speed Domain |

0x4A00 0000 |

0x4AFF FFFF |

16MB |

高速外设域 |

| Q1 |

Instrumentation |

0x4B00 0000 |

0x4BFF FFFF |

16MB |

EMU子系统区域 |

| Q1 |

DDR EMIF0 register |

0x4C00 0000 |

0x4CFF FFFF |

16MB |

配置寄存器 |

| Q1 |

DDR EMIF1 register |

0x4D00 0000 |

0x4DFF FFFF |

16MB |

配置寄存器 |

| Q1 |

DDR DMM Register |

0x4E00 0000 |

0x4FFF FFFF |

32MB |

配置寄存器 |

| Q1 |

GPMC Register |

0x5000 0000 |

0x50FF FFFF |

16MB |

配置寄存器 |

| Q1 |

PCIe Gen2 Register |

0x5100 0000 |

0x51FF FFFF |

16MB |

配置寄存器 |

| Q1 |

Reserved |

0x5200 0000 |

0x52FF FFFF |

16MB |

Reserved |

| Q1 |

HDVICP2-2 Config |

0x5300 0000 |

0x53FF FFFF |

16MB |

HDVICP2-2 Host端口 |

| Q1 |

HDVICP2-2 SL2 |

0x5400 0000 |

0x54FF FFFF |

16MB |

HDVICP2-2 SL2端口 |

| Q1 |

Reserved |

0x5500 0000 |

0x55FF FFFF |

16MB |

Reserved |

| Q1 |

SGX530 |

0x5600 0000 |

0x56FF FFFF |

16MB |

SGX530从端口 |

| Q1 |

Reserved |

0x5700 0000 |

0x57FF FFFF |

16MB |

Reserved |

| Q1 |

HDVICP2-0 Config |

0x5800 0000 |

0x58FF FFFF |

16MB |

HDVICP2-0 Host端口 |

| Q1 |

HDVICP2-0 SL2 |

0x5900 0000 |

0x59FF FFFF |

16MB |

HDVICP2-0 SL2端口 |

| Q1 |

HDVICP2-1 Config |

0x5A00 0000 |

0x5AFF FFFF |

16MB |

HDVICP2-1 Host端口 |

| Q1 |

HDVICP2-1 SL2 |

0x5B00 0000 |

0x5BFF FFFF |

16MB |

HDVICP2-1 SL2端口 |

| Q1 |

Reserved |

0x5C00 0000 |

0x5CFF FFFF |

32Mb |

Reserved |

| Q1 |

Reserved |

0x5E00 0000 |

0x5FFF FFFF |

32MB |

Reserved |

| Q1 |

Tiler |

0x6000 0000 |

0x7FFF FFFF |

512MB |

虚拟Tiled地址空间 |

| Q2 |

DDR EMIF0/1 SDRAM |

0x8000 0000 |

0xBFFF FFFF |

1GB |

DDR |

| Q3 |

DDR EMIF0/1 SDRAM |

0xC000 0000 |

0xFFFF FFFF |

1GB |

DDR |

| Q4-7 |

DDR DMM |

0x1 0000 0000 |

0x1 FFFF FFFF |

4GB |

DDR DMM Tiler 扩展地址映射虚拟视图(仅HDVPPS) |

4. L4内存映射

4.1 L4标准外设

L4标准外设总线存取标准的外设和IP配置寄存器。内存映射表入表2-27

表2-27 L4标准外设内存映射

| 器件名称 |

起始地址 |

结束地址 |

尺寸 |

描述 |

| L4标准配置 |

0x4800 0000 |

0x4800 07FF |

2KB |

地址/保护(AP) |

| 0x4800 0800 |

0x4800 0FFF |

2 KB |

连接代理(LA) |

|

| 0x4800 1000 |

0x4800 13FF |

1 KB |

Initiator端口(IP0) |

|

| 0x4800 1400 |

0x4800 17FF |

1 KB |

Initiator端口(IP1) |

|

| 0x4800 1800 |

0x4800 1FFF |

2 KB |

保留(IP2 – IP3) |

|

| 保留 |

0x4800 2000 |

0x4800 7FFF |

24 KB |

保留 |

| e-Fuse控制器 |

0x4800 8000 |

0x4800 8FFF |

4 KB |

外设寄存器 |

| 0x4800 9000 |

0x4800 9FFF |

4 KB |

支持寄存器 |

|

| 保留 |

0x4800 A000 |

0x4800 FFFF |

24 KB |

保留 |

| DEMMU |

0x4801 0000 |

0x4801 0FFF |

4KB |

外设寄存器 |

| 0x4801 1000 |

0x4801 1FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4801 2000 |

0x4801 FFFF |

56KB |

保留 |

| UART0 |

0x4802 0000 |

0x4802 0FFF |

4KB |

外设寄存器 |

| 0x4802 1000 |

0x4802 1FFF |

4KB |

支持寄存器 |

|

| UART1 |

0x4802 2000 |

0x4802 2FFF |

4KB |

外设寄存器 |

| 0x4802 3000 |

0x4802 3FFF |

4KB |

支持寄存器 |

|

| UART2 |

0x4802 4000 |

0x4802 4FFF |

4KB |

外设寄存器 |

| 0x4802 5000 |

0x4802 5FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4802 6000 |

0x4802 7FFF |

8KB |

保留 |

| I2C0 |

0x4802 8000 |

0x4802 8FFF |

4KB |

外设寄存器 |

| 0x4802 9000 |

0x4802 9FFF |

4KB |

支持寄存器 |

|

| I2C1 |

0x4802 A000 |

0x4802 AFFF |

4KB |

外设寄存器 |

| 0x4802 B000 |

0x4802 BFFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4802 C000 |

0x4802 DFFF |

8KB |

保留 |

| TIMER1 |

0x4802 E000 |

0x4802 EFFF |

4KB |

外设寄存器 |

| 0x4802 F000 |

0x4802 FFFF |

4KB |

支持寄存器 |

|

| SPIOCP |

0x4803 0000 |

0x4803 0FFF |

4KB |

外设寄存器 |

| 0x4803 1000 |

0x4803 1FFF |

4KB |

支持寄存器 |

|

| GPIO0 |

0x4803 2000 |

0x4803 2FFF |

4KB |

外设寄存器 |

| 0x4803 3000 |

0x4803 3FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4803 4000 |

0x4803 7FFF |

16KB |

保留 |

| McASP0 CFG |

0x4803 8000 |

0x4803 9FFF |

8KB |

外设寄存器 |

| 0x4803 A000 |

0x4803 AFFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4803 B000 |

0x4803 BFFF |

4KB |

保留 |

| McASP1 CFG |

0x4803 C000 |

0x4803 DFFF |

8KB |

外设寄存器 |

| 0x4803 E000 |

0x4803 EFFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4803 F000 |

0x4803 FFFF |

4KB |

保留 |

| TIMER2 |

0x4804 0000 |

0x4804 0FFF |

4KB |

外设寄存器 |

| 0x4804 1000 |

0x4804 1FFF |

4KB |

支持寄存器 |

|

| TIMER3 |

0x4804 2000 |

0x4804 2FFF |

4KB |

外设寄存器 |

| 0x4804 3000 |

0x4804 3FFF |

4KB |

支持寄存器 |

|

| TIMER4 |

0x4804 4000 |

0x4804 4FFF |

4KB |

外设寄存器 |

| 0x4804 5000 |

0x4804 5FFF |

4KB |

支持寄存器 |

|

| TIMER5 |

0x4804 6000 |

0x4804 6FFF |

4KB |

外设寄存器 |

| 0x4804 7000 |

0x4804 7FFF |

4KB |

支持寄存器 |

|

| TIMER6 |

0x4804 8000 |

0x4804 8FFF |

4KB |

外设寄存器 |

| 0x4804 9000 |

0x4804 9FFF |

4KB |

支持寄存器 |

|

| TIMER7 |

0x4804 A000 |

0x4804 AFFF |

4KB |

外设寄存器 |

| 0x4804 B000 |

0x4804 BFFF |

4KB |

支持寄存器 |

|

| GPIO1 |

0x4804 C000 |

0x4804 CFFF |

4KB |

外设寄存器 |

| 0x4804 D000 |

0x4804 DFFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4804 E000 |

0x4804 FFFF |

8KB |

保留 |

| McASP2 CFG |

0x4805 0000 |

0x4805 1FFF |

8KB |

外设寄存器 |

| 0x4805 2000 |

0x4805 2FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4805 3000 |

0x4805 FFFF |

52KB |

保留 |

| SD/SDIO |

0x4806 0000 |

0x4806 FFFF |

64KB |

寄存器 |

| 0x4807 0000 |

0x4807 0FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4807 1000 |

0x4807 FFFF |

60KB |

保留 |

| ELM |

0x4808 0000 |

0x4808 FFFF |

64KB |

错误定位模块 |

| 0x4809 0000 |

0x4809 0FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4809 1000 |

0x480B FFFF |

188KB |

保留 |

| RTC |

0x480C 0000 |

0x480C 0FFF |

4KB |

外设寄存器 |

| 0x480C 1000 |

0x480C 1FFF |

4KB |

支持寄存器 |

|

| WDT1 |

0x480C 2000 |

0x480C 2FFF |

4KB |

外设寄存器 |

| 0x480C 3000 |

0x480C 3FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x480C 4000 |

0x480C 7FFF |

16KB |

保留 |

| Mailbox |

0x480C 8000 |

0x480C 8FFF |

4KB |

外设寄存器 |

| 0x480C 9000 |

0x480C 9FFF |

4KB |

支持寄存器 |

|

| Spinlock |

0x480C A000 |

0x480C AFFF |

4KB |

外设寄存器 |

| 0x480C B000 |

0x480C BFFF |

4KB |

支持寄存器 |

|

| 保留 |

0x480C C000 |

0x480F FFFF |

208KB |

保留 |

| HDVPSS |

0x4810 0000 |

0x4811 FFFF |

128KB |

外设寄存器 |

| 0x4812 0000 |

0x4812 0FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4812 1000 |

0x4812 1FFF |

4KB |

保留 |

| HDMI1.3Tx |

0x4812 2000 |

0x4812 2FFF |

4KB |

外设寄存器 |

| 0x4812 3000 |

0x4812 3FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4812 4000 |

0x4812 FFFF |

112KB |

保留 |

| 控制模块 |

0x4814 0000 |

0x4815 FFFF |

128KB |

外设寄存器 |

| 0x4816 0000 |

0x4816 0FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4816 1000 |

0x4817 FFFF |

124KB |

保留 |

| PRCM |

0x4818 0000 |

0x4818 2FFF |

12KB |

外设寄存器 |

| 0x4818 3000 |

0x4818 3FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4818 4000 |

0x4818 7FFF |

16KB |

保留 |

| SmartReflex0 |

0x4818 8000 |

0x4818 8FFF |

4KB |

外设寄存器 |

| 0x4818 9000 |

0x4818 9FFF |

4KB |

支持寄存器 |

|

| SmartReflex1 |

0x4818 A000 |

0x4818 AFFF |

4KB |

外设寄存器 |

| 0x4818 B000 |

0x4818 BFFF |

4KB |

支持寄存器 |

|

| OCP Watchpoint |

0x4818 C000 |

0x4818 CFFF |

4KB |

外设寄存器 |

| 0x4818 D000 |

0x4818 DFFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4818 E000 |

0x4818 EFFF |

4KB |

保留 |

| 0x4818 F000 |

0x4818 FFFF |

4KB |

保留 |

|

| 保留 |

0x4819 0000 |

0x4819 0FFF |

4KB |

保留 |

| 0x4819 1000 |

0x4819 1FFF |

4KB |

保留 |

|

| 保留 |

0x4819 2000 |

0x4819 2FFF |

4KB |

保留 |

| 0x4819 3000 |

0x4819 3FFF |

4KB |

保留 |

|

| 保留 |

0x4819 4000 |

0x4819 4FFF |

4KB |

保留 |

| 0x4819 5000 |

0x4819 5FFF |

4KB |

保留 |

|

| 保留 |

0x4819 6000 |

0x4819 6FFF |

4KB |

保留 |

| 0x4819 7000 |

0x4819 7FFF |

4KB |

保留 |

|

| DDR0 Phy Ctrl Regs |

0x4819 8000 |

0x4819 8FFF |

4KB |

外设寄存器 |

| 0x4819 9000 |

0x4819 9FFF |

4KB |

支持寄存器 |

|

| DDR1 Phy Ctrl Regs |

0x4819 A000 |

0x4819 AFFF |

4KB |

外设寄存器 |

| 0x4819 B000 |

0x4819 BFFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4819 C000 |

0x481F FFFF |

400KB |

保留 |

| 中断控制器(1) |

0x4820 0000 |

0x4820 0FFF |

4KB |

仅Cortex-A8可以存取 |

| 保留(1) |

0x4820 1000 |

0x4823 FFFF |

252KB |

仅Cortex-A8可以存取 |

| MPUSS config Register(1) |

0x4824 0000 |

0x4824 0FFF |

4KB |

仅Cortex-A8可以存取 |

| 保留(1) |

0x4824 1000 |

0x4827 FFFF |

252KB |

仅Cortex-A8可以存取 |

| 保留(1) |

0x4828 1000 |

0x482F FFFF |

508KB |

仅Cortex-A8可以存取 |

| 保留 |

0x4830 0000 |

0x48FF FFFF |

13MB |

保留 |

(1)这些区域在Cortex A8子系统内部译码,物理上不是L4的一部分,它们在这儿被包括,仅是为了当考虑Cortex A8内存映射的时候作为参考。对于除了Cortex A8外的Master,这些区域是保留的。

4.2 L4高速外设

L4高速外设总线存取L3里的高速外设IP配置寄存器。内存映射表如2-28

表2-28 L4高速外设内存映射

| 器件名称 |

起始地址 |

结束地址 |

尺寸 |

描述 |

| L4高速配置 |

0x4A00 0000 |

0x4A00 07FF |

2KB |

地址/保护(AP) |

| 0x4A00 0800 |

0x4A00 0FFF |

2KB |

连接代理(LA) |

|

| 0x4A00 1000 |

0x4A00 13FF |

1KB |

Initiator端口(IP0) |

|

| 0x4A00 1400 |

0x4A00 17FF |

1KB |

Initiator端口(IP1) |

|

| 0x4A00 1800 |

0x4A00 1FFF |

2KB |

保留(IP2 - IP3) |

|

| 保留 |

0x4A00 2000 |

0x4A07 FFFF |

504KB |

保留 |

| 保留 |

0x4A08 0000 |

0x4A0A 0FFF |

132KB |

保留 |

| 保留 |

0x4A0A 0000 |

0x4A0F FFFF |

380KB |

保留 |

| EMAC0 |

0x4A10 0000 |

0x4A10 3FFF |

16KB |

外设寄存器 |

| 0x4A10 4000 |

0x4A10 4FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4A10 5000 |

0x4A11 FFFF |

108KB |

保留 |

| EMAC1 |

0x4A12 0000 |

0x4A12 3FFF |

16KB |

外设寄存器 |

| 0x4A12 4000 |

0x4A12 4FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4A12 5000 |

0x4A13 FFFF |

108KB |

保留 |

| SATA |

0x4A14 0000 |

0x4A14 FFFF |

64KB |

外设寄存器 |

| 0x4A15 0000 |

0x4A15 0FFF |

4KB |

支持寄存器 |

|

| 保留 |

0x4A15 1000 |

0x4A17 FFFF |

188KB |

保留 |

| 保留 |

0x4A18 0000 |

0x4A19 FFFF |

128KB |

保留 |

| 0x4A1A 0000 |

0x4A1A 0FFF |

4KB |

保留 |

|

| 保留 |

0x4A1A 1000 |

0x4AFF FFFF |

14716KB |

保留 |