MBD-FPGA设计小实例:FM接收机

[在此处输入文章标题]

原理及实现思路

2011年6月4日

21:43

Author By McCrocodile

源文件:http://download.csdn.net/source/3340585

原理及实现思路:

1. 常用解调方法:

1. 锁相解调(较优的方法)

2. 包络检波

3. 斜率鉴频

4. 相位鉴频

5. 脉冲技术鉴频

6. 正交解调

2. 正交解调原理

a. 参考文献:

i. 文献A 软件无线电FM中频接受系统的仿真与验证 陈惠兵 硕士论文

ii. 文献B 基于FPGA的FM解调/位同步系统设计与实现 柴俊栓 空空导弹研究院

iii. 文献C 基于SDR的通信系统解调与技术研究 王荔 硕士论文

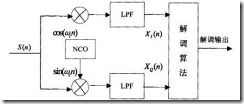

b. 数字正交解调通用模型:(文献C P19)

c. FM正交解调:(文献A P27 文献C P21)

i. 信号表达式:

b. 信号正交分解:

c. 鉴频:

d. 鉴频的改进:(计算反正切和除法将耗费FPGA大量的资源,且实现起来比较复杂)推到请参考:高等数学中的导数和微分章节(函数的微分和arctan的微分)

3. 系统参数设计及容差设计

a. 接收机数字部分架构:

b. 参数设计:

i. 输入IF信号信号:455KHz ,AD采样速度10MHz 10bit位宽

ii. FPGA外部晶振时钟:32.768MHz,内部解调模块工作时钟fsp=10MHz(由外部晶振产生的时钟用FPGA内部PLL分频得到)

iii. CIC阶数:2阶

iv. 下采样系数:4 (Downsample factor)

v. LPF1、LPF2及LPF3参数相同:(满足FM调频信号要求)

1. 采样率Fs=2.5MHz

2. 通带fpass=200KHz 、fstop=400Hz

3. 阶数和通带波纹及阻带衰减:阶数8阶(由于资源限制,只选8阶,由其决定阻带衰减)

文件说明

2011年6月5日

0:03

工程文件说明

1. 目录说明:FM_demod_classification为顶层目录,FM_demod_classification的子目录QII为QuartusII工程所在目录,QII的子目录IQCIC,JianpinQI,mynco和Unsig2Sign为子系统演进和仿真文件所在目录,QII的子目录hdlsrc为生成可以用于FPGA上HDL代码。

2. 文件说明:

a. FM_demod_classification目录下文件:(此目录下模型生成HDL不一定能用于FPGA)

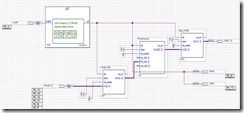

i. _Basic.mdl为基本原理仿真模型

ii. _hdllib.mdl为兼容HDL生成的模型

iii. _fp.mdl为定点模型

iv. UnsigSign.mdl为有符号和无符号之间的转换

v. _over_CompareToDouble.mdl为最中用于生成代码的模型与浮点模型的比较

b. QII目录下文件:

i. _over_CoderUsing.mdl用于生成代码的模型

ii. FM_demod.qpf为用于FPGA的最终接收机的QuartusII工程文件。

c. IQCIC,JianpinQI,mynco和Unsig2Sign子系统仿真测试目录:qpf均为对于子系统的工程文件,其下的simulation/modelsim为时序仿真文件和模型所在目录

3. 工程文件的共同点:通过后缀顾名思义

MBD开发的模型以及结构

2011年6月5日

0:11

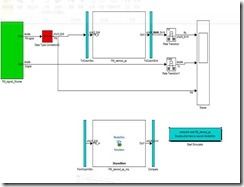

测试平台:武汉凌特入门级软件无线电开发平台

FPGA:EP2C5Q240

ADC:AD9200 10MHz 10bit

DAC:TLC5602 10MHz 8bit 外界扬声器或者耳机

DSP 未使用

测试环境:

接受FM广播信号。约100M(86M~106M)变换到低IF 455KHz

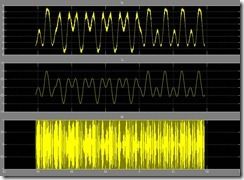

测试结果:

接收到质量不错的广播信号。

屏幕剪辑的捕获时间: 2011/6/5 2:03

屏幕剪辑的捕获时间: 2011/6/5 2:00

屏幕剪辑的捕获时间: 2011/6/5 2:00

屏幕剪辑的捕获时间: 2011/6/5 2:04

屏幕剪辑的捕获时间: 2011/6/5 1:58

联合仿真测试EDA Link

2011年6月5日

1:59

屏幕剪辑的捕获时间: 2011/6/5 2:10

屏幕剪辑的捕获时间: 2011/6/5 2:11

屏幕剪辑的捕获时间: 2011/6/5 2:12

屏幕剪辑的捕获时间: 2011/6/5 2:11

屏幕剪辑的捕获时间: 2011/6/5 2:12

总结

2011年6月5日

0:00

1. LPF滤波器资源耗费过大:

a. FIR IP core 和Matlab的filter HDL coder生成代码都比较占用资源,即使选择一个满足误差要求的较窄位宽。

b. 使用一种减少乘法器的FIR实现,同时减小位宽和系数精度。参考文献:数字信号处理的FPGA实现 刘凌译 清华大学 P79

3. 使用CIC+LPF代替单个LPF,CIC只是用加法器和延时器

3. 对模型的几个配置:simulationàconfigure param

a. Slover:

i. Type:Fixed-step

ii. Solver:Discrete (no cantinous status)

iii. TaskModel:SingleTasking

b. Diagnostis/Sampletime:

i. Multitask rate transition:error

ii. Singletask rate transition:error