Quartus II modelsim使用与testbench编写

本文使用的是Quartus II Version 10.0 和Modelsim 6.5e。

下面是如何使用modelsim进行时序仿真的步骤:

建立工程led0_module.qpf ,输入让led灯翻转的Verilog HDL。源代码和后面要使用到的testbench在下面链接中。

http://download.csdn.net/detail/wu20093346/6523223 //源代码资源

led0_module.v 如下:

module led0_module

(

CLK, RSTn, LED_Out

);

input CLK;

input RSTn;

output LED_Out;

/*************************************/

parameter T = 21'd20;

/*************************************/

reg [20:0]Count1;

always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

Count1 <= 21'd0;

else if( Count1 == T )

Count1 <= 21'd0;

else

Count1 <= Count1 + 1'b1;

/*************************************/

reg rLED_Out;

always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

rLED_Out <= 1'b0;

else if( Count1 >= 21'd0 && Count1 < 21'd5 )

rLED_Out <= 1'b1;

else

rLED_Out <= 1'b0;

/***************************************/

assign LED_Out = rLED_Out;

/***************************************/

endmodule

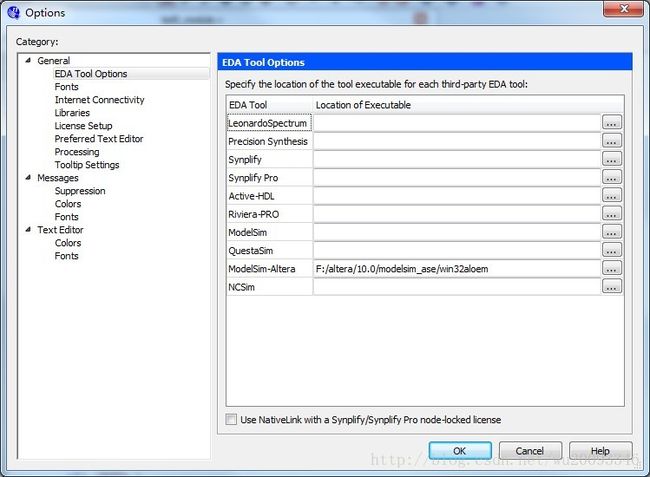

第一次使用modelsim要进行EDA tool的位置设置:打开Tools》Options》General》EDA Tool Options找到ModelSim-Altera位置

点击Processing 》Start 》Start Test Bench Template Writer创建testbench的.vt文件

自动保存在工程目录下的simulation/modelsim文件夹下,打开编辑

`timescale 1 ps/ 1 ps

module led0_module_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg CLK;

reg RSTn;

// wires

wire LED_Out;

// assign statements (if any)

led0_module i1 (

// port map - connection between master ports and signals/registers

.CLK(CLK),

.LED_Out(LED_Out),

.RSTn(RSTn)

);

initial

begin

// code that executes only once

// insert code here --> begin

RSTn=0; //reset

#1000; //delay

RSTn=1;

// --> end

$display("Running testbench");

end

initial

begin

CLK = 0;

forever

#10 CLK= ~CLK; //clk set

end

endmodule

在待测模块中的reg型信号在Testbench中自动变成了wire,待测模块中的wire型信号在Testbench中则对应为reg型。

输入testbench之后设置仿真:

点击Assignments》Setting…

点击Test Benches 输入test bench name,保持和testbench.vt中的module后面的一致,这个界面可以设置初始执行时间。

点击“…”浏览vt文件,点击add

ok,ok,ok。

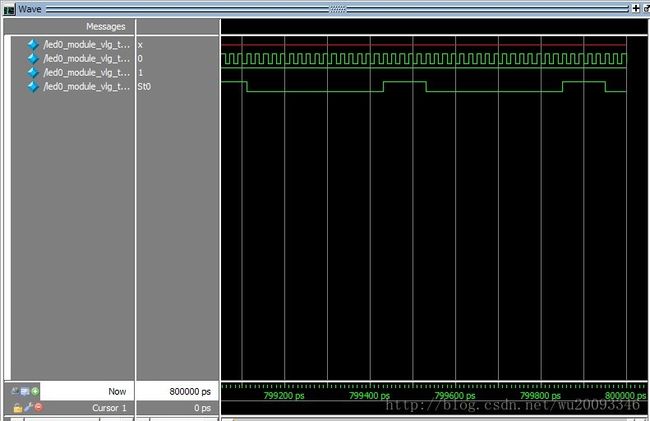

开始仿真:

Tools》Run EDA Simulation Tool》EDA RTL Simulation

仿真成功。

源代码参照资源

http://download.csdn.net/detail/wu20093346/6523223