系统设计---算法与架构

这片文章对系统设计的具体步骤及相关知识进行介绍,主要分为四部分:算法设计、IC系统架构设计、基于systemC的IC系统设计、系统设计工具SPW简介。

(一)算法设计

系统设计的第一步是给出清晰的系统规范,该规范写明了系统的功能、性能、费用、开发时间等。接下来创建一个系统行为模型,并且可以用来初步验证设计的性能。再下来,对行为模型进行细化,即进行算法设计。算法设计大致分为三步:

1)给出浮点运算

2)给出定点数运算

3)如有可能,给出周期精确的模型,可用于软件调试

算法确定以后,要进行详细的架构设计。设计者要确定功能子模块的划分、子模块的接口、存储器架构、总线架构、总线带宽等。

算法是对数进行操作。数由定点数和浮点数之分。定点数分诶定点整数和定点小数。对于定点整数,小数点的位置约定在最低位的右边,用来表示整数。对于定点小数,小数点的位置约定在符号位之后,用来表示小于1的纯小数。浮点数是由阶码E、尾数M、符号位S、基数R构成。R为2的幂,S为符号位。一个浮点数的数值可以表示为: N=(-1)S *M *RE。

在设计算法时,首先要考虑的问题是如何表示数据。也就是要考虑用多长的位宽来表示数据,数据是否是有符号的。

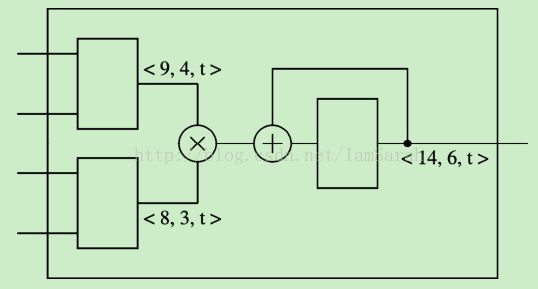

这里给出了一种数的表示方法,这里用

下面对数字信号处理(DSP)概括介绍一下。通信、个人计算机、汽车电子、视频等式IC应用的几个重要领域。这些领域都需要大量的数字信号处理。数字信号处理与模拟信号处理相比,有以下优点:

1)受温度漂移和工艺变化影响小

2)受噪声干扰小

3)可以得到更高的信噪比

4)通过改变信号字长,可以很灵活的控制精度

5)可以在放大信号的同时消除噪声和干扰

6)可以无误差的存储和传输

信号处理的一般过程如下:

评价一个DSP性能指标,主要针对下面几个方面:

1)执行速度:跟系统的吞吐量和时钟频率有关

2)功耗

3)字长:字长越大,量化噪声和舍入噪声越小,但所占面积越大。

一般情况下,DSP运算包括卷积、相关、数字滤波、自适应滤波、快速傅里叶变换、离散余弦变换等。DSP算法的描述:可以利用框图表示、也可以用信号流图表示。

(二)IC系统架构设计

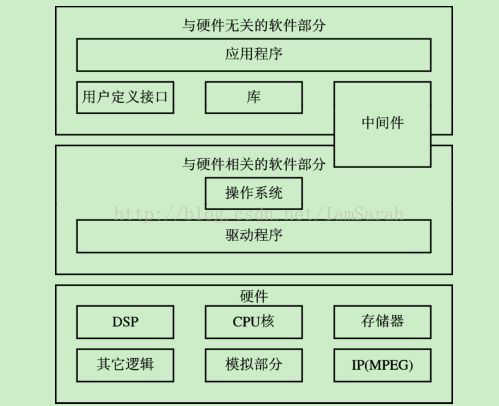

下图表示的是一个SOC包含的内容:

由图可知,SOC包括软件和硬件两部分,硬件包括CPU核,DSP,存储器、模拟部分、特定IP、用户设计的逻辑。软件部分包括与硬件相关的操作系统、驱动程序以及与硬件无关的应用程序和用户定义的接口。架构设计是一个逐步细化的过程,将系统的功能模块映射为实现架构的过程,在进行架构设计时,需考虑如下因素:

1)系统的性能要求、功耗、造价、开发回见

2)对系统的功能要求

3)可供选择的IP功能和性能

4)系统中数据的流向和操作

5)系统中的控制操作

6)输入数据精度和输出精度

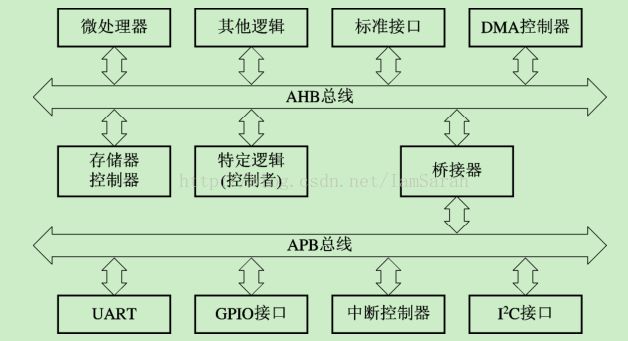

选取何种微处理器是确定SOC架构的重要环节,占主要市场的还是ARM处理器。设计SOC架构时,需要考虑模块的连接方式,有两种方式,一是点对点的连接,一种是基于总线的连接。点对点连接可以保证最大的性能,但是复用性较差,因此在SOC设计中,一般采用基于总线的连接。数据要在模块间传递,必须通过片上总线。总线是一种共享资源,在某一时刻,只能有一个模块驱动总线,这样才不会发生冲突。总线设计中定义了master 和slave的概念,系统中存在多个master时就需要仲裁器来仲裁。一般嵌入式处理器、DMA、DSP均可以作为master。通常外部存储器接口、APB桥、内部存储器都可以用作slave。

目前,有两种主要的片上系统总线标准:ARM的AMBA及IBM的CoreConnect。下面主要对AMBA总线进行介绍。AMBA总线中定义了三种总线。

1)AHB总线:具有高性能、支持流水操作、支持多个master,支持突发burst传输,支持分段split传输,采用单时钟沿操作、数据宽度可配置为128bit。

2)ASB总线:具有高性能、流水线操作,支持多个master的特点.

3)APB总线:具有低功耗、接口简单、对地址和控制信号进行锁存,适合多种外围电路。

APB主要面向低功耗、对性能要求不高的外围电路,AHB、ASB都面向性能要求较高的场合。ASB是较早定义的高速总线标准,AHB是后来定义的高速总线标准。ARM建议在高速场合尽可能用AHB。下图是基于AMBA总线的IC系统架构示例:

(三)基于SystemC的IC系统设计

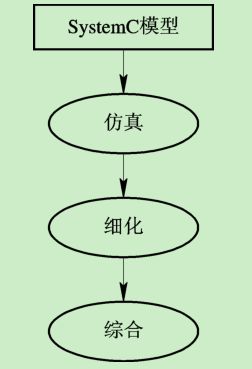

以往,系统设计多用C/C++语言进行建模。在这种设计流程中, 当系统级模型完成后,需要设计者依据C/C++程序的功能给出Verilog/VHDL的RTL描述。由于C/C++语言是在很高抽象层次上的描述,不支持时间、并发、硬件等数据类型,因此设计者需要重新用Verilog/VHDL进行RTL设计。这一过程很耗时,且非常容易发生错误。采用SystemC语言, 在行为模型完成后,系统设计者可以逐步细化模型, 直至给出SystemC的RTL实现。采用SystemC的RTL实现可通过综合工具生成网表,该流程如图所示:

(四)系统设计工具SPW简介

目前最著名的系统级设计工具是cadence公司的SPW,主要应用于数字信号处理及通信领域,有五个基本部分组成:

1)文件管理器:负责创建和管理SPW库,访问所有类型的SPW数据文件,调用不同的SPW工具。

2)框图编辑器:允许以框图的形式构造系统;

3)sigCalc:生成仿真输入信号,分析仿真输出信号,并运行仿真;

4)仿真管理器:对仿真进行设置,并运行仿真。

5)DSP库:提供标准的库模块,以方便DSP系统的设计与仿真。