PCIe总线初识

PCIe总线

一、PCIe总线与PCI总线的区别

PCIe总线与PCI最大的区别在工作原理上,PCIe是采用点到点的串行方式进行传输的,被称为“串行PCI”,由于采用了串行方式传输使得其工作频率可以达到2.5Ghz,大大增加了传输速率,同时采用全双工的通信方式,使得其传输速度提高了一倍,每一个PCIe总线设备与外部通信时有四根数据总线,分别有两个RX和TX,两根用于发送,两根由于接收。

二、PCI总线的优点

1、双通道,高带宽,传输速度快

首先采用全双工的工作模式,在同一时刻既可以进行数据发送,也可以进行数据接收。两个信道,每个信道单方向的传输速率至少达到2.5Gbps。

2、灵活性号

可以直接延伸到系统外部,通过专用接口与外部设备相连接。

3、低电源消耗,含有电源管理系统

PCIe采用了比较少的物理结构,与外部相连的只有四根引脚。

4、支持设备的热插拔和热交换

PCIe接口的插槽上含有热插拔感应信号。

5、支持同步数据传输

6、具有数据包和层协议架构,

它采用类似于网络通信中的OSI分层模式,各层使用专门的协议架构。

7、具有错误处理和先进的错误报告功能

PCI Express总线采用分层架构,具有软件层,软件层的主要功能就是进行错误处理和提供错误报告。

8、在软件层保持与PCI兼容

兼容性比较好,能够兼容PCI架构的设备。

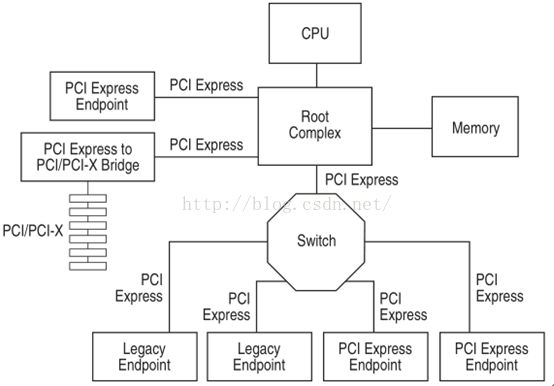

三、PCIe总线的总线架构

PCIe总线的基本结构包括根组件(Root Complex)、交换器(Switch)和各种终端设备(Endpoint)。根组件可以集成在北桥芯片中,用于处理器和内存子系统与I/O设备之间的连接,而交换器的功能通常是以软件形式提供的,它包括两个或更多的逻辑PCI到PCI的连接桥(PCI-PCI Bridge),以保持与现有PCI兼容。下图即为PCie总线的拓扑结构图。目前,几乎除了与内存的连接之外,其他的连接都是使用PCie总线的。

图1 PCie总线的拓扑结构图

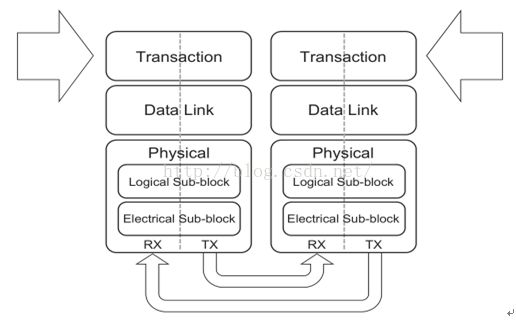

四、PCie总线的分层结构

为了便于跨平台使用,PCIe总线体系结构采用分层设计。PCIe体系结构如图2所示。它共分为四层,从下到上分别为:物理层(Physical Layer)、数据链路层(Link Layer)、处理层(Transaction Layer)和软件层(Software Layer)。图中并木有显示出软件层。

图2 PCie总线的分层结构图

1、物理层

物理层是最底层,它负责接口或者设备之间的连接。物理层决定了PCIe总线接口的物理特性,如点对点串行连接、微差分信号驱动、热拨插、可配置带宽等,决定了其四根线全双工的串行数据传输方式。

在物理层的另一处重要方面就是中断。PCIe总线支持两个类型的中断,现行的PCI INTx (x= A, B, C, or D) 中断(即PCI总线的中断)被保留下来了,仍可在PCIe总线中应用。还有一个新的中断类型,那就是MSI (Message Signaled Interrupt,信息信号中断),INTx中断方式可以用信号方式中断主机芯片请求,它可以与现行的PCI总线的驱动程序和操作系统兼容。PCIe设备必须支持INTx和MSI两种中断模式,原有设备将压缩INTx中断信息在PCIe处理信息中。MSI中断是通过内存写处理操作边沿触发和发送的。重新编写驱动程序对于MSI边沿触发中断是非常有利的,MSI方案在使用数据包协议通过串行连接中是一种行之有效的本地中断方式。MSI在多处理器系统中任何设备都可以发送中断,比起主机直接发送中断更加有效,所以现在许多多处理器系统和I/O架构都对MSI中断技术提供支持。

2、数据链路层

数据链路层的主要职责就是确保数据包可靠、正确的传输。确保数据包的完整性,并在数据包中添加序列号和发送冗余校验码到处理层。大多数数据包是由处理层发起的,基于信任的原则,数据流控制协议确保数据包只在终端缓存空闲时进行传输。排队了所有数据的重试,使得信道带宽浪费现象得到有效地约束。但数据链路层在信号中断时自动重新传输数据包。

3、处理层

处理层的作用主要是接受从软件层送来的读、写请求,并且建立一个请求包传输到数据链路层。所有请求都是分离执行的。处理层同时接受从链路层传来的响应包,并与原始的软件请求关联。处理层还整合或者拆分处理级数据包来发送请求,如数据读、写请求,并且操纵链接配置和信号控制。以确保端到端连接通信正确,没有无效数据通过整个组织(包括源设备和目标设备,甚至包括可能通过的多个桥接器和交换器)。处理层包括4个地址空间,其中3个是PCI接口原有的,如内存、I/O和配置地址空间,加上一个PCie新增的“信息空间”。

4、软件层

软件层是保持与PCI总线兼容的关键。其目的在于使系统在使用PCIe启动时,像在PCI下的初始化和运行那样,无论是在系统中发现的硬件设备,还是在系统中的资源,如内存、I/O空间和中断等,它可以创建非常优化的系统环境,而不需要进行任何改动。在PCIe体系结构中保持这些配置空间和I/O设备连接的规范稳定是非常关键的。事实上,在PCIe平台中,所有操作系统在引导时都不需要进行任何编辑,也就是说在软件方面完全可以实现从PCI总线平稳过渡。

在软件响应时间模式方面,PCIe体系结构支持PCI的本地存储、共享内存模式,这样所有PCI软件在PCIe体系中运行都不需任何改变。当然新的软件可能包括新的特性。

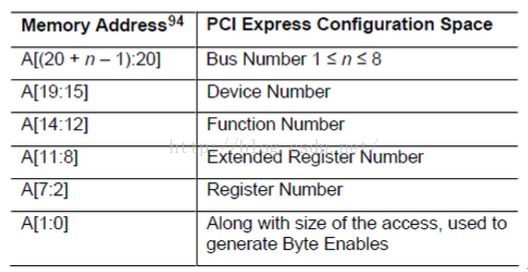

五、PCie总线的配置机制

与PCI局部总线标准允许的256字节配置空间相比,PCIe规范将配置空间扩展到4096字节。PCIe配置空间分为 1个PCI3.0兼容区域(前256字节)和剩余的PCIe配置空间。PCI3.0兼容配置空间既可以被PCI局部总线标准定义的机制访问,也可以被PCIe增强配置访问机制(ECAM)访问。两者是等同的。而PCIe扩展的配置空间只能够通过ECAM机制访问。PCIe兼容PCI总线的配置机制,在PCI总线的配置空间中占用4M空间地址,不同的是PCI总线设备在超过的256K后的空间使用0来代替,这样使得可以使用PCIe的访问机制继续访问。

PCIe 增强的配置访问机制(ECAM)使用一个平坦内存映射的地址空间来访问设备配置寄存器。在这种情况下,配置寄存器的访问、内存数据刷新、返回寄存器的内容等操作都是在内存中完成的。映射空间的大小和基址由host桥和固件决定。由硬件在“应用规范”行为中向操作系统汇报。

图3 内存地址访问

如上图所示。总线范围的大小由host桥映射到Bus Number field在配置地址空间中的二进制位数决定的,即系统映射了几个内存地址到Bus Number field中,这个映射的个数就是n值,n取值1~8。一个映射了n个内存地址位的host桥支持0~2n-1个总线,除此之外,范围的基址要和2(n+20)字节内存地址空间边界对齐。任何在Bus Number field中没有映射到内存地址的位必须被清零。