嵌入式硬件开发之四——原理图后期处理

4 原理图后期处理

4.1 DRC检查

按照前面的方法把原理图剩下的部分绘制完成后需要仔细检查,这一般通过自查和组织评审来完成。通常在人工检查之前可以由软件来完成初步的检查,可以发现一些比较基础的错误,比如输出管脚连接了输出管脚(通常应该连接到输入管脚)。检查的步骤如下:

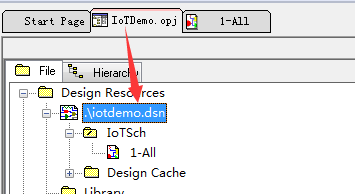

首先切换到项目所在的标签页,然后点击要检查的DSN。

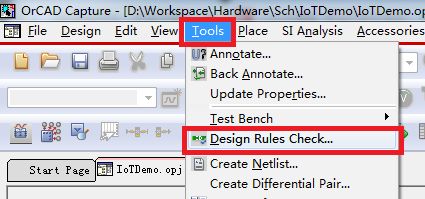

接下来依次选择Tools->Design roules check...菜单

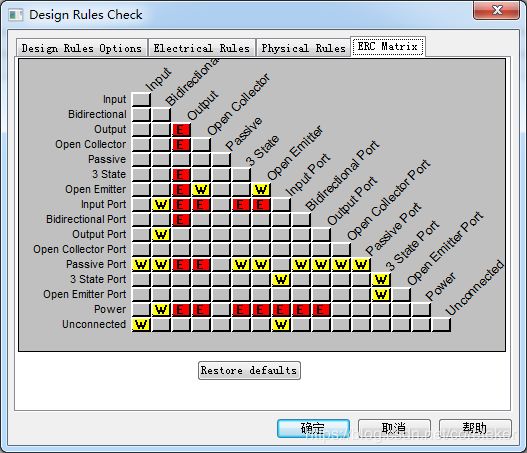

在弹出的对话框中选择ERC Matrix标签,设置规则。

上图中,Output和Output相连会产生错误,其他以此类推。点击小方块,可改变规则,但通常使用默认规则。

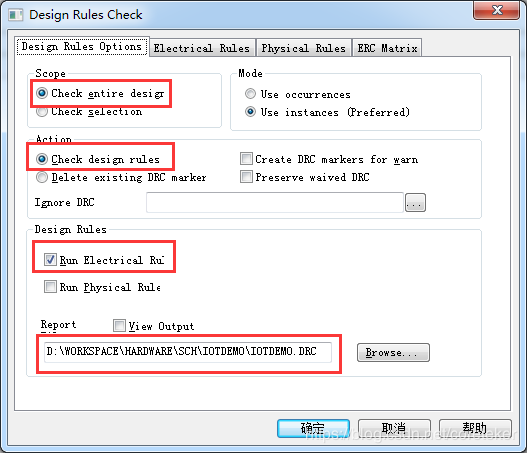

规则设置好之后,点击Design Rules Options标签,进行相应的设置后,点击OK可以进行DRC检查。

检查完成如有警告或错误产生会弹出如下对话框,点击是可以查看日志来确定错误或警告。

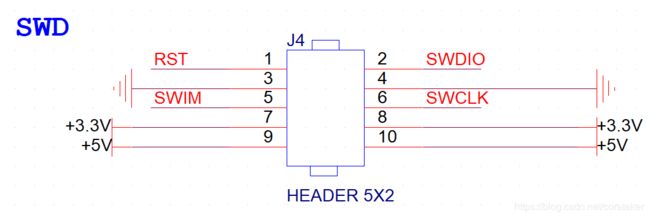

本例中的两处处警告是RST和SWIM网络没有与电路图中的其他任何一处相连,这可能是有意这么设计的,也有可能是网络名写错了,导致线路没有连通,需要根据具体情况来处理。

4.2 元器件编号

在放置元件的时候,软件会自动对元件编号,如上图中的J4。但随着电路的反复修改,会导致编号很乱。我们通常希望一个功能模块的元件的编号也集中在一个小范围内,这样在做硬件调试的时候,方便快速在电路板上找到关心的元器件。电路图设计完成后,可以对整个设计进行一次重新编号,步骤如下。

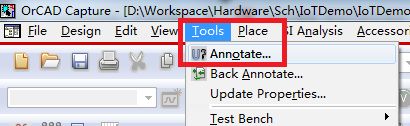

首先还是切换到项目的标签页上,然后依次选择Tools->Annotate...菜单。

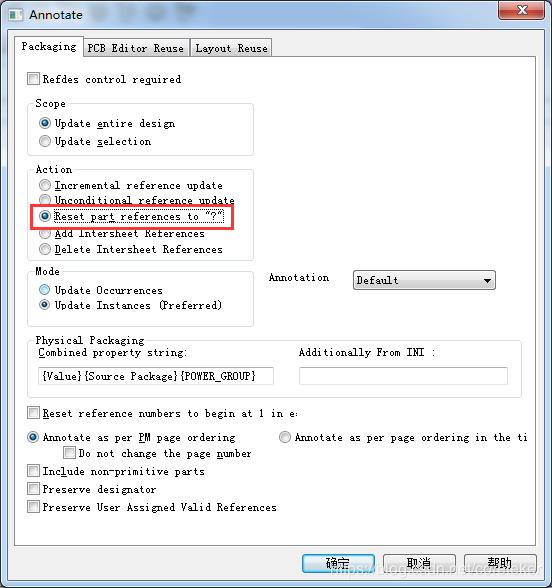

在弹出的对话框中我们可以首先选择将所有的编号重置为?,然后点击确定。

然后再次按照上面的步骤,选择顺序编号,点击确定。这样元件的编号就会全部重新依次顺序编排一次。

需要注意的是,如果在进行PCB设计的过程中发现有器件增删的情况,则最好不要重新编号,因为这会导致已经完成的PCB部分的位号和最新的原理图不符和,会给PCB设计增加很大的工作量。

4.3 添加封装属性

原理图中的每个元件最终会摆放在PCB中,他们的形状,大小等由封装属性来描述。PCB的设计者会给每种器件都设计好这个封装(后面的章节会介绍),我们在原理图设计的时候要指定好这些封装,从而PCB设计者才能进行进一步设计。如果某个元件第一次在原理图中使用,那么他通常是没有封装信息的。如果是拷贝了已经设好封装的元件,那封装属性也会一起拷贝过来。但不管怎样,在原理图设计完成之后,确认所有元件的封装还是非常有必要的。步骤如下。

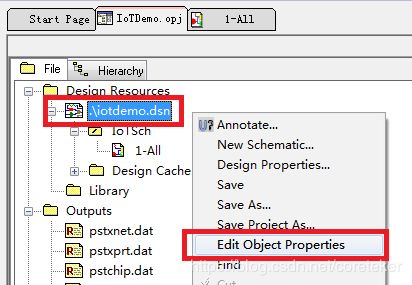

首先还是切换到项目标签页上,然后右击项目文件,在弹出的菜单中选择Edit object properties。

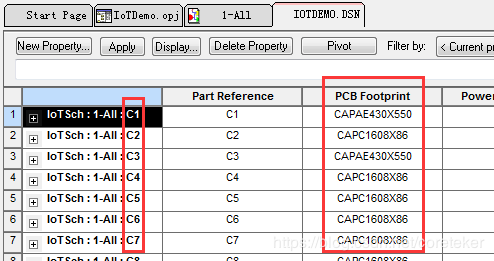

在新的标签页中,左边红框内就是元件的编号,右边红框内就是该器件的封装的名称。

设置完成后注意保存。

4.4 导出网表

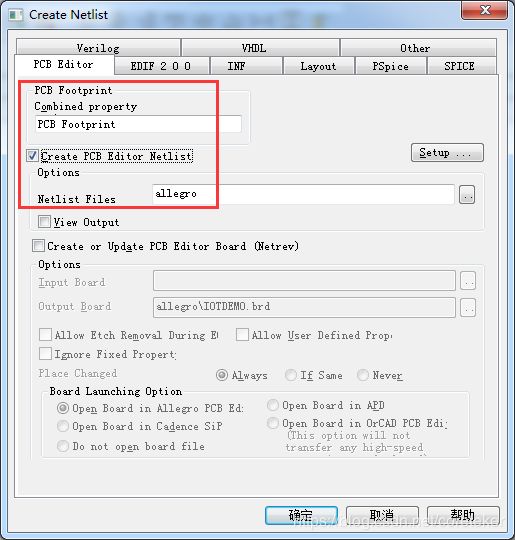

网表是原理图和PCB交互的最重要的信息,PCB中器件的大小和连接方式都来自于这个网表,是PCB设计的重要输入。输出网表的步骤如下。

切换到项目标签页,选择项目,依次选择Tools->Create Netlist...菜单。

默认情况下在弹出的对话框中点击确定即可。

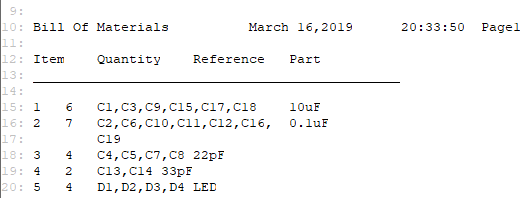

4.5 生成BOM表

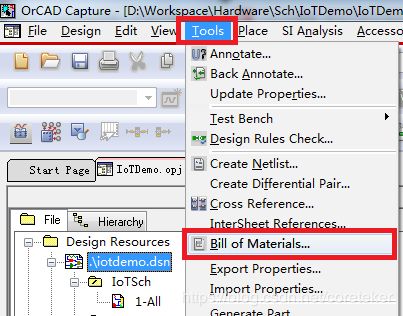

BOM表是电路板加工的重要表单,其中记录了元件位号和该元件的封装、元件的值和数量等属性。生成BOM表的方法如下。

选择项目标签页,点击项目,依次选择Tools->Bill of Materials...菜单。

通常采用默认设置即可,点击OK生成BOM。

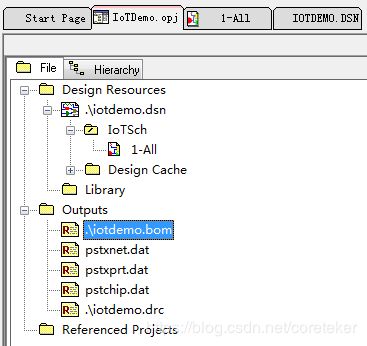

输出的BOM文件可以通过点击下图中BOM后缀的文件名来查看。另外dat后缀是网表文件,drc后缀是DRC输出文件。

4.6 打印原理图

原理图打印和其他文件打印类似,为方便其他人员查看,通常会打印成PDF格式,当然这需要先有PDF打印机。在出图时注意设置右下角的文档编号和版本等信息。