06 初始化SDRAM

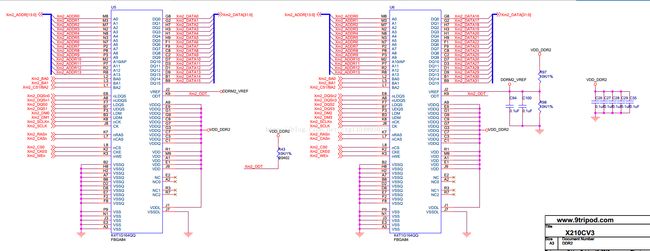

一、查阅核心板原理图SDRAM部分

从以上原理图中可以得出以下信息:

(1)开发板上使用的SDRAM编码是K4T1G164QQ

(2)开发板上包括4片内存芯片,每片内存的数据总线都是16位的

(3)横向的两颗内存芯片是并联的(并联时地址总线的接法一样,但数据总线要加起来),这样连接相当于在逻辑上可以把这两颗内存芯片看成是一个32位的内存芯片

(4)每个内存端口都由3类总线构成:地址总线(Xm1_ADDR0~Xm1_ADDR13、Xm2_ADDR0~Xm2_ADDR13)+ 控制总线 + 数据总线(Xm1_DATA0~Xm1_DATA31、Xm2_DATA0~Xm2_DATA31)

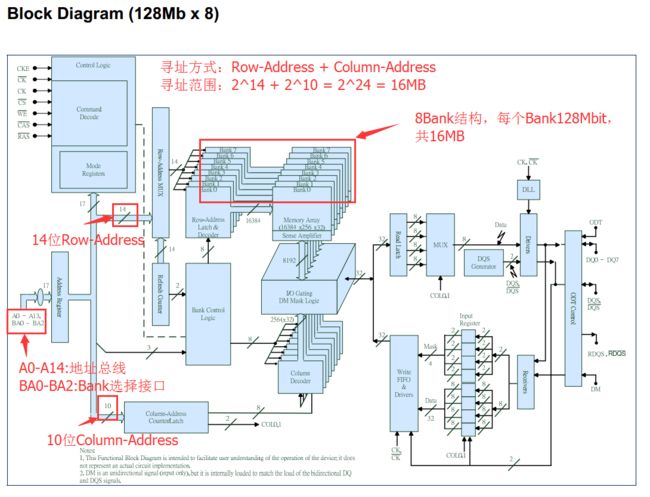

二、查阅SDRAM数据手册

由上图可得出K4T1G164QQ的含义如下:

K:三星内存

4:DRAM

T:DDR2 SDRAM

1G:1Gb(128MB)

16:单芯片16位宽

4:8 Banks

三、内存寻址详解

由上图可得出以下信息:

(1)S5PV210的内存端口信号中有BA0~BA2,接在内存芯片的BA0~BA2上,这些引脚用来选择Bank

(2)每个Bank内部有128Mb,通过Row Address(14位)+ Column Address(10位)的方式来综合寻址

(3)一共能寻址的范围是:2的24次方,也就是16MB(128Mb)的内存

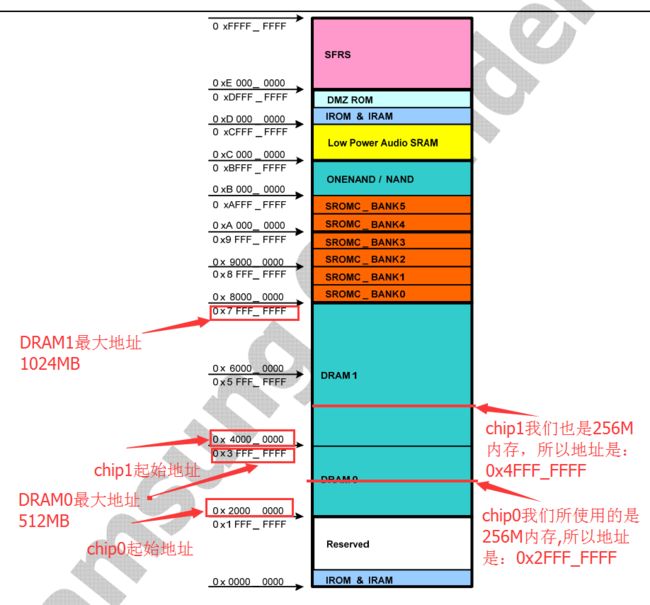

四、内存映射

从上图可得出以下信息:

(1)S5PV210共有两个内存端口,分别是DRAM0和DRAM1

(2)DRAM0的内存地址范围是0x20000000~0x3FFFFFFF(512MB)

(3)DRAM1的内存地址范围是0x40000000~0x7FFFFFFF(1024MB)

由此,得出结论:

(1)S5PV210最多支持1.5GB的内存,如果给它更多的内存,CPU就无法识别

(2)S5PV210最多支持1.5GB的内存,但实际开发板上不一定有这么多。例如X210开发板就只有512MB的内存(DRAM0端口分布256MB,DRAM1端口分布256MB)

(3)X210开发板上内存的合法地址是0x20000000~0x2FFFFFFF(256MB)+ 0x40000000~0x4FFFFFFF(256MB)

综合以上信息,进一步得出结论:

(1)X210开发板共使用了4片内存,每片1Gb(128MB),共512MB

(2)DRAM0对应的引脚是Xm1_xxxx

(3)DRAM1对应的引脚是Xm2_xxxx

(4)从数据总线的位数可知,X210开发板用的是32位的内存

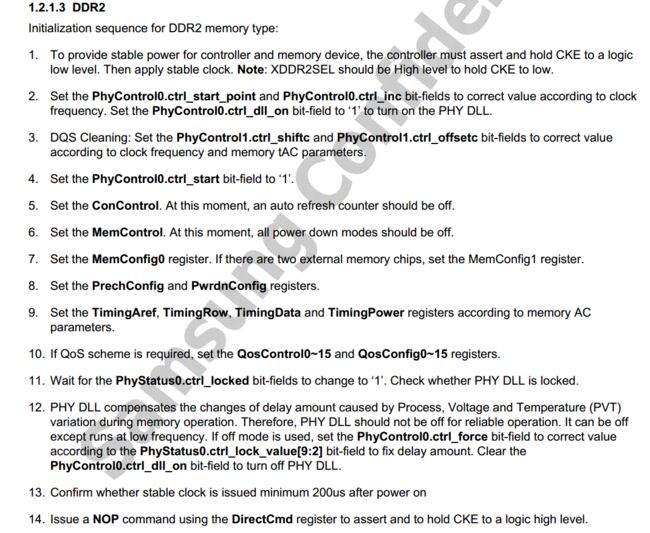

五、SDRAM初始化详解

SDRAM初始化共涉及到两个文件:s5pv21.h 和 sdram_init.s

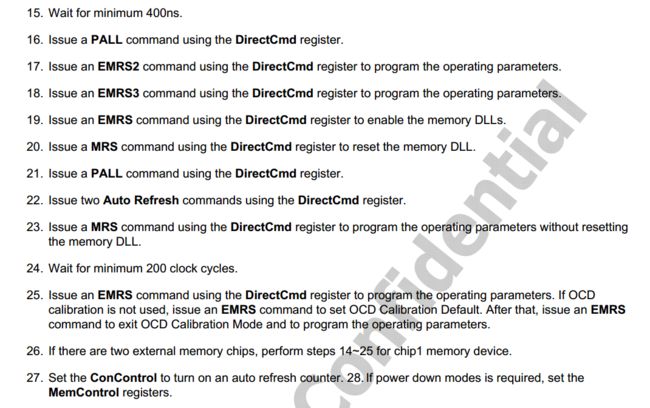

三星在官方的数据手册里(section 05 memory->DRAM CONTROLLER->1.2.1.3章节中)讲到DDR2的初始化过程,共27步,如下图:

15. 等最小400ns

初始化步骤翻译请参考:http://blog.csdn.net/mutemob/article/details/12968565

代码请参考:http://blog.csdn.net/czg13548930186/article/details/54893629

代码详细解释请参考:http://www.cnblogs.com/biaohc/p/6346949.html