【 Vivado 】使用Vivado设计一个加/减法器的IP核(简洁英文版)

数据手册地址:Adder/Subtracter v12.0

Vivado Integrated Design Environment

You can customize the IP for use in your design by specifying values for the various parameters associated with the IP core using the following steps:

1. Select the IP from the IP catalog.

2. Double-click the selected IP

Core Parameters

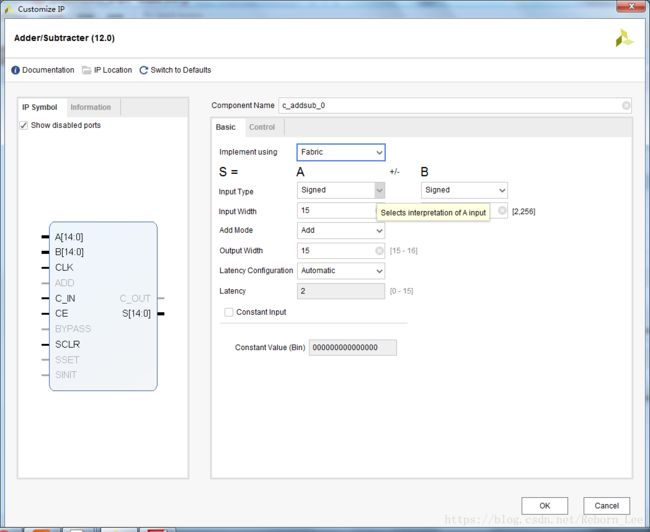

The Adder/Subtracter Vivado IDE provides fields to set the parameters values for the required instantiation. This section provides a description of each field.

Implement using: Sets the implementation type to Fabric or DSP48.

A Input Width: Sets the width of the port A input. In IP integrator, this parameter is auto-updated.

A Input Type: Sets the type of the port A data to Signed or Unsigned.

B Input Width: Sets the width of the port B input.

B Input Type: Sets the type of the port B data to Signed or Unsigned.

Constant Input and Constant Value: When Constant Input is TRUE, port B is set to the value that is specified with the parameter Constant Value. Constant Value must be entered in binary format and must not exceed B Input Width. In most cases specifying port B to be a constant creates a module without port B. The only exception to this is when bypass functionality is requested, as port B is needed to provide the bypass data in this case. The default setting is for the port B value to be provided by port B.

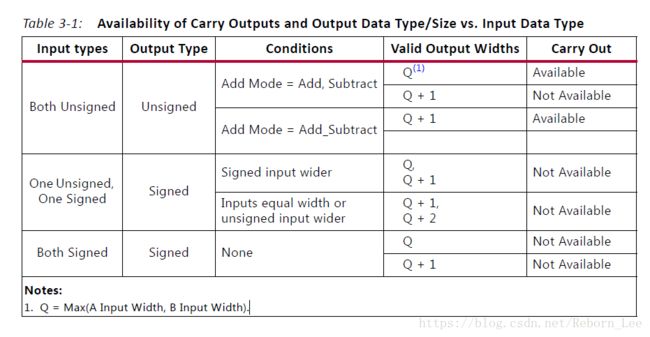

Output Width: Sets the output width. The valid range varies depending on the settings of A Input Width, A Input Type, B Input Width, and B Input Type

Add Mode: Sets the mode of operation of the module. Valid values are Add, Subtract, and Add/Subtract. If an adder/subtracter is specified, the ADD pin sets the mode of operation.

Carry In: When this parameter is set to TRUE, a C_IN port is created. This is an active-High, carry-in port for adders and a programmable (active-High/active-Low with Borrow In/Out Sense) carry-in port for subtracters and adder/subtracters in subtract mode.

Carry Out: When set to TRUE, this parameter creates port C_OUT which is the synchronous active-High carry-out from the adder and adder/subtracter in add mode and the programmable (active-High/active-Low with Borrow In/Out Sense) borrow-out from the subtracter or adder/subtracter in subtract mode.

Bypass: When set to TRUE, creates a BYPASS pin. Activating the BYPASS pin sets the output to be the value given on port B. This functionality is used for creating loadable counters and accumulators.

Clock Enable: When set to TRUE, the module is generated with a clock enable input.

Power on Reset Init Value: Specifies (in hex) the value the S register initializes to during power-up reset.

Latency Configuration: Automatic sets optimal latency for maximum speed; Manual allows user to set Latency to one of the allowed values.

Latency: Value used for latency when Latency Configuration is set to Manual.

博文最开始给出了设计这个IP核的收据手册,如果想了解全部,则认真研读数据手册。

博文给出了设计这个IP核最关键的信息:

Vivado Integrated Design Environment表示打开定制IP核的环境,分为两个步骤:

第一步,建立一个工程,进入IP核设计页面:

第二步,双击选择需要的IP核。

然后进入IP核设计页面:

然后根据需求,设计IP核。

之后给出各个参数的意思,认真阅读这些参数之后,就可以直接设计自己需要的IP核了。

上面的博文中简单的列出了比较关键的参数,至于那些一眼就能看出啥意思的,也省略了一些,例如:

框里的这些东西,一眼就能看出是谁的优先级高而已,自己看着选择就好了。

由于是最简单的一个IP和设计,如果写成中文版,那就太low了,直接看英文的,更有意思点!