- 嵌入式MCU平台汇总

TENET-

嵌入式单片机嵌入式硬件mcu

文章目录1.单片机(MCU)2.数字信号处理器(DSP)3.ARMCortex系列4.超低功耗MCU5.物联网MCU(IoTMCU)6.开源架构MCU(RISC-V)7.可编程逻辑器件(FPGA)1.单片机(MCU)概念:单片机(MicrocontrollerUnit,MCU)是集成了中央处理器(CPU)、存储器(RAM、ROM或Flash)、输入输出端口(I/O)以及各种外设(如定时器、串行通信

- Stm32中SysTick 定时器的使用

weixin_58038206

stm32单片机嵌入式硬件

ysTick_Config(SystemCoreClock/100);这行代码通常出现在基于ARMCortex-M内核微控制器的程序中,用于配置SysTick定时器,下面结合代码进行详细解释:1.SysTick定时器SysTick定时器是ARMCortex-M内核中一个简单的24位递减定时器,也被称为系统滴答定时器。它常用于产生精确的时间延迟、实现周期性的任务调度等功能。2.SystemCoreC

- STM32操作FLASH

weixin_58038206

stm32嵌入式硬件单片机

以下将为你详细介绍STM32的Flash操作相关知识,包含基本原理、操作步骤,并给出具体的代码示例。1.STM32Flash基本原理1.1Flash存储器结构STM32的Flash存储器用于存储程序代码和一些需要掉电保存的数据。它通常被划分为多个扇区,每个扇区有固定的大小。不同系列的STM32芯片,其Flash扇区大小和数量可能不同。例如,STM32F103系列的Flash扇区大小有1KB、2KB

- Stm32定时器输出PWM

weixin_58038206

stm32单片机嵌入式硬件

下面为你提供使用STM32标准库实现定时器初始化、输出PWM以及添加定时器中断功能的详细代码及解释。此示例以STM32F103系列芯片为例,使用定时器3输出PWM信号并添加定时器更新中断。代码示例#include"stm32f10x.h"//函数声明voidRCC_Configuration(void);voidGPIO_Configuration(void);voidTIM3_Configura

- STM32F103C8T6 USB寄存器开发详解(3)-中断

云汐独渺

STM32USB开发单片机嵌入式硬件

对于USB模块,因为其通讯流程比较复杂,因此配置硬件中断就显得很重要了.STM32F103的中断寄存器位于另一个手册中,也就是下方蓝色标题的链接地址.NVIC寄存器用于启用中断,中断向量表中有两个USB相关中断,从机设备仅需要RX中断,也就是表项20.因此只需要配置NVIC_ISER0寄存器的位20即可开启USB模块中断,至于中断优先级分组等情况,可以直接使用默认配置,若有需要可以手动配置其余NV

- stm32正常运行流程图_stm32初始化流程图解析

imToken-Daisy

stm32正常运行流程图

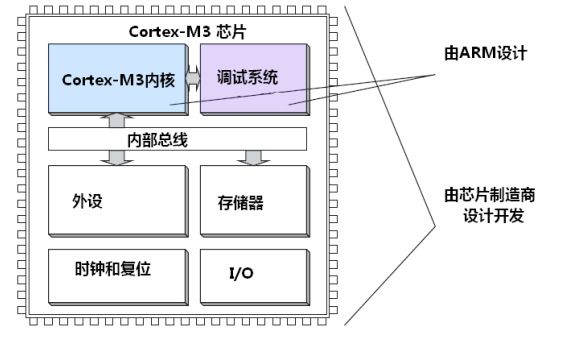

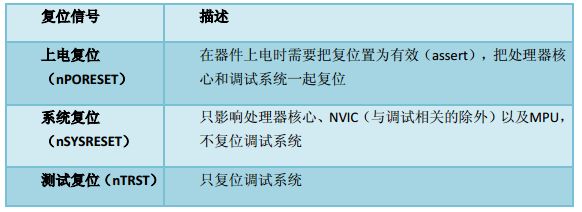

STM32系列基于专为要求高性能、低成本、低功耗的嵌入式应用专门设计的ARMCortex-M3内核。stm32参数:12V-36V供电兼容5V的I/O管脚优异的安全时钟模式带唤醒功能的低功耗模式内部RC振荡器内嵌复位电路工作温度范围:-40°C至+85°C或105°Cstm32特点:内核:ARM32位Cortex-M3CPU,最高工作频率72MHz,1.25DMIPS/MHz。单周期乘法和硬件除法

- 在单片机中是否应该取消32.768kHz外部晶振

鹿屿二向箔

单片机嵌入式硬件

在STM32F103C8T6中,32.768kHz外部晶振(LSE)并非必须,其必要性取决于具体应用需求。以下是详细分析:1.是否需要32.768kHz晶振?需要LSE晶振的场景实时时钟(RTC):若需RTC功能(如日历、精确计时),且要求高精度时间基准,必须使用32.768kHz晶振(LSE)。原因:内部低速RC振荡器(LSI,约40kHz)精度较低(±1%),可能导致时间累积误差(每天约1分钟

- STM32基础教程——按键控制LED

Czzzzlq

stm32嵌入式硬件单片机

目录概要技术实现1.硬件接线图2.引脚定义3.代码实现实验要点问题总结概要1.实验名称:按键控制LED2.实验环境:STM32F103C8T6最小系统板3.实验内容:两个按键分别控制两个LED的亮灭4.作者;abai5.实验时间:2025-2-18技术实现1.硬件接线图2.引脚定义3.代码实现main.c#include"stm32f10x.h"//Deviceheader#include"Del

- STM32F4系列微控制器深入应用手册

满天乱走

本文还有配套的精品资源,点击获取简介:STM32F4系列微控制器由意法半导体推出,基于ARMCortex-M4内核,旨在提供高性能和低功耗的嵌入式解决方案。这些详细文档覆盖了Cortex-M4处理器架构、处理器状态、系统控制寄存器、调试接口、外设功能和电气特性等方面,帮助开发者深入理解STM32F4的设计和应用。文档内容详尽,包括直接内存访问、图形显示控制器、音频接口和内存控制器的特定外设,以及如

- RTOS 特性及其思考

TianYaKe-天涯客

arm开发

前言最近在研究FreeRTOS,觉得RTOS有些特性还是比较有趣的,有一些想法,问了一下AI,简单探讨一下。有纰漏请指出,转载请说明。学习交流请发邮件

[email protected]百问网《FreeRTOS入门与工程实践-基于STM32F103》教程-基于DShanMCU-103(STM32F103)|百问网为什么有些项目,裸机编程不再适用,需要RTOS一、任务调度与并发处理裸机编程:在裸机环境

- 《Linux设备驱动开发具体解释(第3版)》进展同步更新

weixin_33943836

驱动开发内存管理嵌入式

本博实时更新《Linux设备驱动开发具体解释(第3版)》的最新进展。2015.2.26差点儿完毕初稿。本书已经rebase到开发中的Linux4.0内核,案例多数基于多核CORTEX-A9平台。[F]是修正或升级;[N]是新增知识点;[D]是删除的内容第1章《Linux设备驱动概述及开发环境构建》[D]删除关于LDD6410开发板的介绍[F]更新新的Ubuntu虚拟机[N]加入关于QEMU模拟ve

- [008] [RT-Thread学习笔记] 求结构体首地址rt_list_entry函数与字节对齐RT_ALIGN宏

柯西的彷徨

RT-Threadlist数据结构rtos

RT-Thread学习笔记rt_list_entry函数源码分析应用示例RT_ALIGN宏源码分析应用示例RT-Thread版本:4.0.5MCU型号:STM32F103RCT6(ARMCortex-M3内核)1rt_list_entry函数rt_list_entry函数的作用是根据已知成员的地址,算出其结构体的首地址。函数定义如下(在rtservice.h中):1.1源码分析#definert_

- DSP和ARM的优劣比较(也有FPGA)

bingfeng_adonis

工作

概念1.FPGA:是可编程逻辑阵列,常用于处理高速数字信号,不过随着科技的发展,现在很多FPGACPLD可以集成mcu内核,甚至具备了ARMDSP的功能2.ARM,是一类内核的称谓,就像51一样,具体到芯片的话,会有很多不同的厂家不同等级,诸如三星、易法、飞利浦、摩托罗拉等等,其中STM32是易法半导体的一款面向工控低功耗内核为CortexM3内核的ARM芯片3.DSP顾名思义就是数字信号处理,厂

- 【项目实战】Miniforge安装和管理python

本本本添哥

Pythonpython

Miniforge是一个轻量级的Conda安装器,它提供了一种快速、独立的方法来安装和管理Python的科学计算环境。Miniforge由社区维护,并专注于兼容ARM架构的设备(如AppleM1/M2/M3芯片)和其他CPU架构。与Anaconda和Miniconda相比,Miniforge提供了几个显著的优势,包括更小的安装包、更快的安装速度、较少的磁盘占用以及使用conda-forge作为默认

- STM32之SG90舵机控制

如愿小李

stm32嵌入式硬件单片机

目录前言:一、硬件准备与接线1.1硬件清单1.2接线二、SG90舵机简介1.1外观1.2基本参数1.3引脚说明1.4控制原理1.5特点1.6常见问题三、单片机简介四、程序设计4.1定时器配置4.2角度控制函数4.3主函数调用五、总结前言:STM32F103C8T6是一款性价比极高的ARMCortex-M3内核微控制器,广泛应用于嵌入式开发。SG90舵机则是小型舵机的代表,常用于机器人、智能家居等场

- STM32 是什么?同类产品有哪些

天机️灵韵

硬件设备物联网stm32单片机嵌入式硬件

STM32是什么?STM32是由意法半导体(STMicroelectronics)推出的基于ARMCortex-M内核的32位微控制器(MCU)系列。它专为高性能、低功耗的嵌入式应用设计,广泛应用于以下领域:工业控制(PLC、电机驱动)消费电子(智能家居、穿戴设备)物联网(传感器、通信模块)汽车电子(车载控制、CAN总线)医疗设备(便携式监测仪)。STM32提供丰富的产品线(如STM32F、STM

- 汇编简介&常用语法

官子无敌刘小路

汇编

为什么要有汇编因为Cortex-A芯片一上电SP指针还没初始化,C环境还没准备好,所以肯定不能运行C代码,必须先用汇编语言设置好C环境,比如初始化DDR、设置SP指针等等,当汇编把C环境设置好了以后才可以运行C代码GNU语法如果大家使用过STM32的话就会知道MDK和IAR下的启动文件startup_stm32f10x_hd.s其中的汇编语法是有所不同的,将MDK下的汇编文件直接复制到IAR下去编

- 使用RT-Thread Studio DIY 迷你桌面时钟(三)| 获取NTP时间(at_device软件包 + netutils软件包)----基于stm32f103rct6

杜嗨皮

c语言

先参考官方的文章使用RT-ThreadStudioDIY迷你桌面时钟(三)|获取NTP时间(at_device软件包+netutils软件包)_Mculover666的博客-CSDN博客1.项目进度桌面Mini时钟项目用来演示如何使用RT-ThreadStduio开发项目,整个项目的架构如下:在上一篇博文中简单的介绍了RT-ThreadStudio一站式工具,基于STM32L431RCT6这个芯片

- 基于STM32的智能加湿器设计

5132单片机设计

单片机设计stm32嵌入式硬件单片机

一、任务简述本次设计采用基于单片机的智能加湿器系统,以STM32F103C8T6和温湿度传感器DHT11为核心,通过湿度传感器采集和转换温湿度信号,再利用单片机进行数据分析和处理,实现智能开启和关闭加湿功能,并通过继电器控制加湿器,以实现对湿度的精准调节。实现加湿器防干烧和实时显示室内相对湿度的功能,需要外接辅助电路的支持。由于其简洁明了的电路设计、易于读取的特点以及高精度的检测能力,该系统在可靠

- STM32标准库与C语言实现的电子琴发声单元

黄冈新学爸

本文还有配套的精品资源,点击获取简介:该项目利用STM32F103C8T6微控制器和无源蜂鸣器,通过C语言和PWM技术控制音调,实现了电子琴的音调高低变化。电子琴支持演奏、录制和播放录制三种模式,代码组织结构清晰,涵盖了嵌入式系统开发的核心技术点。1.STM32F103C8T6微控制器应用STM32F103C8T6微控制器是STMicroelectronics生产的一款性能强大的Cortex-M3

- 操作系统|ARM和X86的区别,存储,指令集

wowing-

操作系统arm开发stm32windows

文章目录主频寄存器寄存器在硬件中的体现是什么寄存器的基本特性硬件实现寄存器类型内存和寄存器的区别内存(Memory)和磁盘(Disk)指令的执行ARMCortex-M3与Thumb-2指令集Thumb-2与流水线虚拟地址指令的执行多核CPU芯片间的通信机制ISA指令集主频主频,即CPU的时钟频率(ClockSpeed),是指每秒钟内CPU能够执行的基本操作次数,通常以赫兹(Hz)为单位表示,现代处

- 探索物联网世界:STM32F103C8T6与ESP8266无线通信指南

郎爽果

探索物联网世界:STM32F103C8T6与ESP8266无线通信指南STM32F103C8T6与ESP8266构建通信二项目地址:https://gitcode.com/Resource-Bundle-Collection/d2ab9项目介绍在物联网(IoT)快速发展的今天,将传统嵌入式设备连接到互联网已成为许多开发者的迫切需求。本项目旨在为开发者提供一个详细的指南,帮助他们利用STM32F10

- STM32F103C8T6与ESP8266构建无线通信指南

薄化克Oswald

STM32F103C8T6与ESP8266构建无线通信指南STM32F103C8T6与ESP8266构建通信二项目地址:https://gitcode.com/Resource-Bundle-Collection/d2ab9简介本资源文档旨在指导开发者如何利用STM32F103C8T6微控制器与ESP8266WiFi模块建立通信。通过详细的步骤说明,您将学会如何配置ESP8266无需预先烧录特定固

- 嵌入式Linux驱动学习_简单了解Cortex-A7 MPCore架构

Les maths

linux运维服务器

Cortex-A7MPcore处理器支持1~4核,通常是和Cortex-A15组成big.LITTLE架构的,Cortex-A15作为大核负责高性能运算,比如玩游戏啥的,Cortex-A7负责普通应用,因为CortexA7省电。Cortex-A7本身性能也不弱,不要看它叫做Cortex-A7但是它可是比Cortex-A8性能要强大,而且更省电。Cortex-A7MPCore支持在一个处理器上选配1

- ARM Cortex-A7 MPCore 架构

小火球2.0

BSP从入门到精通arm开发

1、Cortex-A7MPCore简介Cortex-A7MPcore处理器支持1~4核,通常是和Cortex-A15组成big.LITTLE架构的,Cortex-A15作为大核负责高性能运算,比如玩游戏啥的,Cortex-A7负责普通应用,因为CortexA7省电。Cortex-A7本身性能也不弱,不要看它叫做Cortex-A7但是它可是比Cortex-A8性能要强大,而且更省电。ARM官网对于C

- (盈鹏飞嵌入式SBC-T113全志T113-i主板)-Qt5.12图形库配置说明(可选组件)

szembed

T113-i/T113-S3qt开发语言

SBC-T113产品特性:采用Allwinner公司Cortex-A7双核T113-i处理器,运行最高速度为1.2GHZ;内置64位玄铁C906RISC-VCPU和DSP,提供高效的计算能力;支持1080P视频编码,多格式1080P60fps视频解码(H.265,H.264,MPEG-1/2/4)支持LVDS/MIPI-DSI,分辨率最高1920x1080;支持512-1GBytesDDR3SDR

- T113 Linux Qt

szembed

T113-i/T113-S3linuxqt运维

本系列调试说明记录了Linux在全志T113-S3/S4平台上的移植过程,说明过程中可能会技术瑕疵,希望大家提供宝贵意见。本文移植的硬件平台来自于盈鹏飞嵌入式的SBC-T113S(处理器是T113-S3)主板。SBC-T113S产品特性:采用Allwinner公司Cortex-A7双核T113-S3/S4处理器,运行最高速度为1.2GHZ;内置64-bitXuanTieC906RISC-V协处理器

- (盈鹏飞嵌入式SBC-T113全志T113-i主板)-配置Buildroot

szembed

T113-i/T113-S3网络大数据linux

SBC-T113产品特性:采用Allwinner公司Cortex-A7双核T113-i处理器,运行最高速度为1.2GHZ;内置64位玄铁C906RISC-VCPU和DSP,提供高效的计算能力;支持1080P视频编码,多格式1080P60fps视频解码(H.265,H.264,MPEG-1/2/4)支持LVDS/MIPI-DSI,分辨率最高1920x1080;支持512-1GBytesDDR3SDR

- CubeMX生成STM32工程文件,对串口测试使用(一)

魂兮-龙游

单片机stm32嵌入式硬件信息与通信

目录引言硬件连接软件配置步骤步骤一:开启USART和相关时钟步骤二:配置USART参数步骤三:配置USART(GPIO)数据发送和接收发送数据阻塞方式发送数据中断方式发送数据接收数据阻塞方式接收数据中断方式接收数据引言项目基于STM32F103C8T6开发,工程代码基于CubeMX生成,具体代码生成步骤见用CubeMX生成STM32F103C8T6的工程。本节对生成的工程代码进行初步的解析,实现利

- STM32使用ESP8266接入机智云点亮LED教程_stm32cubemx 使用esp8266连接机智云使用机智云生成的代码

2401_87557120

stm32javascript前端

然后点击保存跳转到如下界面点击去添加数据点,添加我们的一个数据点。数据点,就可以理解为我们编程中定义的变量。我们给数据点起一个名字,叫state,这个后来会在STM32工程里用到。其他属性很简单,不再说明。点击添加,添加第一个数据点点击应用,确认本次修改然后点击左侧导航栏的MCU开发选择独立MCU方案硬件平台就选择STM32F103C8TX在下方粘贴你的ProductSecretProductSe

- SQL的各种连接查询

xieke90

UNION ALLUNION外连接内连接JOIN

一、内连接

概念:内连接就是使用比较运算符根据每个表共有的列的值匹配两个表中的行。

内连接(join 或者inner join )

SQL语法:

select * fron

- java编程思想--复用类

百合不是茶

java继承代理组合final类

复用类看着标题都不知道是什么,再加上java编程思想翻译的比价难懂,所以知道现在才看这本软件界的奇书

一:组合语法:就是将对象的引用放到新类中即可

代码:

package com.wj.reuse;

/**

*

* @author Administrator 组

- [开源与生态系统]国产CPU的生态系统

comsci

cpu

计算机要从娃娃抓起...而孩子最喜欢玩游戏....

要让国产CPU在国内市场形成自己的生态系统和产业链,国家和企业就不能够忘记游戏这个非常关键的环节....

投入一些资金和资源,人力和政策,让游

- JVM内存区域划分Eden Space、Survivor Space、Tenured Gen,Perm Gen解释

商人shang

jvm内存

jvm区域总体分两类,heap区和非heap区。heap区又分:Eden Space(伊甸园)、Survivor Space(幸存者区)、Tenured Gen(老年代-养老区)。 非heap区又分:Code Cache(代码缓存区)、Perm Gen(永久代)、Jvm Stack(java虚拟机栈)、Local Method Statck(本地方法栈)。

HotSpot虚拟机GC算法采用分代收

- 页面上调用 QQ

oloz

qq

<A href="tencent://message/?uin=707321921&Site=有事Q我&Menu=yes">

<img style="border:0px;" src=http://wpa.qq.com/pa?p=1:707321921:1></a>

- 一些问题

文强chu

问题

1.eclipse 导出 doc 出现“The Javadoc command does not exist.” javadoc command 选择 jdk/bin/javadoc.exe 2.tomcate 配置 web 项目 .....

SQL:3.mysql * 必须得放前面 否则 select&nbs

- 生活没有安全感

小桔子

生活孤独安全感

圈子好小,身边朋友没几个,交心的更是少之又少。在深圳,除了男朋友,没几个亲密的人。不知不觉男朋友成了唯一的依靠,毫不夸张的说,业余生活的全部。现在感情好,也很幸福的。但是说不准难免人心会变嘛,不发生什么大家都乐融融,发生什么很难处理。我想说如果不幸被分手(无论原因如何),生活难免变化很大,在深圳,我没交心的朋友。明

- php 基础语法

aichenglong

php 基本语法

1 .1 php变量必须以$开头

<?php

$a=” b”;

echo

?>

1 .2 php基本数据库类型 Integer float/double Boolean string

1 .3 复合数据类型 数组array和对象 object

1 .4 特殊数据类型 null 资源类型(resource) $co

- mybatis tools 配置详解

AILIKES

mybatis

MyBatis Generator中文文档

MyBatis Generator中文文档地址:

http://generator.sturgeon.mopaas.com/

该中文文档由于尽可能和原文内容一致,所以有些地方如果不熟悉,看中文版的文档的也会有一定的障碍,所以本章根据该中文文档以及实际应用,使用通俗的语言来讲解详细的配置。

本文使用Markdown进行编辑,但是博客显示效

- 继承与多态的探讨

百合不是茶

JAVA面向对象 继承 对象

继承 extends 多态

继承是面向对象最经常使用的特征之一:继承语法是通过继承发、基类的域和方法 //继承就是从现有的类中生成一个新的类,这个新类拥有现有类的所有extends是使用继承的关键字:

在A类中定义属性和方法;

class A{

//定义属性

int age;

//定义方法

public void go

- JS的undefined与null的实例

bijian1013

JavaScriptJavaScript

<form name="theform" id="theform">

</form>

<script language="javascript">

var a

alert(typeof(b)); //这里提示undefined

if(theform.datas

- TDD实践(一)

bijian1013

java敏捷TDD

一.TDD概述

TDD:测试驱动开发,它的基本思想就是在开发功能代码之前,先编写测试代码。也就是说在明确要开发某个功能后,首先思考如何对这个功能进行测试,并完成测试代码的编写,然后编写相关的代码满足这些测试用例。然后循环进行添加其他功能,直到完全部功能的开发。

- [Maven学习笔记十]Maven Profile与资源文件过滤器

bit1129

maven

什么是Maven Profile

Maven Profile的含义是针对编译打包环境和编译打包目的配置定制,可以在不同的环境上选择相应的配置,例如DB信息,可以根据是为开发环境编译打包,还是为生产环境编译打包,动态的选择正确的DB配置信息

Profile的激活机制

1.Profile可以手工激活,比如在Intellij Idea的Maven Project视图中可以选择一个P

- 【Hive八】Hive用户自定义生成表函数(UDTF)

bit1129

hive

1. 什么是UDTF

UDTF,是User Defined Table-Generating Functions,一眼看上去,貌似是用户自定义生成表函数,这个生成表不应该理解为生成了一个HQL Table, 貌似更应该理解为生成了类似关系表的二维行数据集

2. 如何实现UDTF

继承org.apache.hadoop.hive.ql.udf.generic

- tfs restful api 加auth 2.0认计

ronin47

目前思考如何给tfs的ngx-tfs api增加安全性。有如下两点:

一是基于客户端的ip设置。这个比较容易实现。

二是基于OAuth2.0认证,这个需要lua,实现起来相对于一来说,有些难度。

现在重点介绍第二种方法实现思路。

前言:我们使用Nginx的Lua中间件建立了OAuth2认证和授权层。如果你也有此打算,阅读下面的文档,实现自动化并获得收益。SeatGe

- jdk环境变量配置

byalias

javajdk

进行java开发,首先要安装jdk,安装了jdk后还要进行环境变量配置:

1、下载jdk(http://java.sun.com/javase/downloads/index.jsp),我下载的版本是:jdk-7u79-windows-x64.exe

2、安装jdk-7u79-windows-x64.exe

3、配置环境变量:右击"计算机"-->&quo

- 《代码大全》表驱动法-Table Driven Approach-2

bylijinnan

java

package com.ljn.base;

import java.io.BufferedReader;

import java.io.FileInputStream;

import java.io.InputStreamReader;

import java.util.ArrayList;

import java.util.Collections;

import java.uti

- SQL 数值四舍五入 小数点后保留2位

chicony

四舍五入

1.round() 函数是四舍五入用,第一个参数是我们要被操作的数据,第二个参数是设置我们四舍五入之后小数点后显示几位。

2.numeric 函数的2个参数,第一个表示数据长度,第二个参数表示小数点后位数。

例如:

select cast(round(12.5,2) as numeric(5,2))

- c++运算符重载

CrazyMizzz

C++

一、加+,减-,乘*,除/ 的运算符重载

Rational operator*(const Rational &x) const{

return Rational(x.a * this->a);

}

在这里只写乘法的,加减除的写法类似

二、<<输出,>>输入的运算符重载

&nb

- hive DDL语法汇总

daizj

hive修改列DDL修改表

hive DDL语法汇总

1、对表重命名

hive> ALTER TABLE table_name RENAME TO new_table_name;

2、修改表备注

hive> ALTER TABLE table_name SET TBLPROPERTIES ('comment' = new_comm

- jbox使用说明

dcj3sjt126com

Web

参考网址:http://www.kudystudio.com/jbox/jbox-demo.html jBox v2.3 beta [

点击下载]

技术交流QQGroup:172543951 100521167

[2011-11-11] jBox v2.3 正式版

- [调整&修复] IE6下有iframe或页面有active、applet控件

- UISegmentedControl 开发笔记

dcj3sjt126com

// typedef NS_ENUM(NSInteger, UISegmentedControlStyle) {

// UISegmentedControlStylePlain, // large plain

&

- Slick生成表映射文件

ekian

scala

Scala添加SLICK进行数据库操作,需在sbt文件上添加slick-codegen包

"com.typesafe.slick" %% "slick-codegen" % slickVersion

因为我是连接SQL Server数据库,还需添加slick-extensions,jtds包

"com.typesa

- ES-TEST

gengzg

test

package com.MarkNum;

import java.io.IOException;

import java.util.Date;

import java.util.HashMap;

import java.util.Map;

import javax.servlet.ServletException;

import javax.servlet.annotation

- 为何外键不再推荐使用

hugh.wang

mysqlDB

表的关联,是一种逻辑关系,并不需要进行物理上的“硬关联”,而且你所期望的关联,其实只是其数据上存在一定的联系而已,而这种联系实际上是在设计之初就定义好的固有逻辑。

在业务代码中实现的时候,只要按照设计之初的这种固有关联逻辑来处理数据即可,并不需要在数据库层面进行“硬关联”,因为在数据库层面通过使用外键的方式进行“硬关联”,会带来很多额外的资源消耗来进行一致性和完整性校验,即使很多时候我们并不

- 领域驱动设计

julyflame

VODAO设计模式DTOpo

概念:

VO(View Object):视图对象,用于展示层,它的作用是把某个指定页面(或组件)的所有数据封装起来。

DTO(Data Transfer Object):数据传输对象,这个概念来源于J2EE的设计模式,原来的目的是为了EJB的分布式应用提供粗粒度的数据实体,以减少分布式调用的次数,从而提高分布式调用的性能和降低网络负载,但在这里,我泛指用于展示层与服务层之间的数据传输对

- 单例设计模式

hm4123660

javaSingleton单例设计模式懒汉式饿汉式

单例模式是一种常用的软件设计模式。在它的核心结构中只包含一个被称为单例类的特殊类。通过单例模式可以保证系统中一个类只有一个实例而且该实例易于外界访问,从而方便对实例个数的控制并节约系统源。如果希望在系统中某个类的对象只能存在一个,单例模式是最好的解决方案。

&nb

- logback

zhb8015

loglogback

一、logback的介绍

Logback是由log4j创始人设计的又一个开源日志组件。logback当前分成三个模块:logback-core,logback- classic和logback-access。logback-core是其它两个模块的基础模块。logback-classic是log4j的一个 改良版本。此外logback-class

- 整合Kafka到Spark Streaming——代码示例和挑战

Stark_Summer

sparkstormzookeeperPARALLELISMprocessing

作者Michael G. Noll是瑞士的一位工程师和研究员,效力于Verisign,是Verisign实验室的大规模数据分析基础设施(基础Hadoop)的技术主管。本文,Michael详细的演示了如何将Kafka整合到Spark Streaming中。 期间, Michael还提到了将Kafka整合到 Spark Streaming中的一些现状,非常值得阅读,虽然有一些信息在Spark 1.2版

- spring-master-slave-commondao

王新春

DAOspringdataSourceslavemaster

互联网的web项目,都有个特点:请求的并发量高,其中请求最耗时的db操作,又是系统优化的重中之重。

为此,往往搭建 db的 一主多从库的 数据库架构。作为web的DAO层,要保证针对主库进行写操作,对多个从库进行读操作。当然在一些请求中,为了避免主从复制的延迟导致的数据不一致性,部分的读操作也要到主库上。(这种需求一般通过业务垂直分开,比如下单业务的代码所部署的机器,读去应该也要从主库读取数